ИпЫйADCЩшМЦжаЕФPCBВМОжВМЯпММЧЩ

ЗЂВМЪБМфЃК2012-4-11 16:34

ЗЂВМепЃКeechina

|

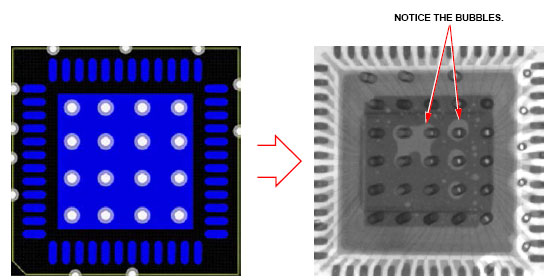

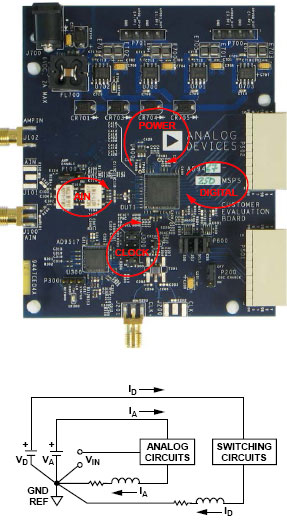

зїепЃКADIЙЋЫОRob Reeder дкЕБНёЕФЙЄвЕСьгђЃЌЯЕЭГЕчТЗАхВМОжвбГЩЮЊЩшМЦБОЩэЕФвЛИізщГЩВПЗжЁЃвђДЫЃЌЩшМЦЙЄГЬЪІБиаыСЫНтгАЯьИпЫйаХКХСДЩшМЦадФмЕФЛњжЦЁЃ дкИпЫйФЃФтаХКХСДЩшМЦжаЃЌгЁЫЂЕчТЗАх(PCB)ВМОжВМЯпашвЊПМТЧаэЖрбЁЯюЃЌгааЉбЁЯюБШЦфЫќбЁЯюИќживЊЃЌгааЉбЁЯюдђШЁОігкгІгУЁЃзюжеЕФД№АИИїВЛЯрЭЌЃЌЕЋдкЫљгаЧщПіЯТЃЌЩшМЦЙЄГЬЪІЖМгІОЁСПЯћГ§зюМбзіЗЈЕФЮѓВюЃЌЖјВЛвЊЙ§ЗжМЦНЯВМОжВМЯпЕФУПвЛИіЯИНкЁЃБОгІгУБЪМЧЬсЙЉЕФаХЯЂЖдЩшМЦЙЄГЬЪІЕФЯТвЛИіИпЫйЩшМЦЯюФПЛсгаЫљАяжњЁЃ ТуТЖКИХЬ ТуТЖКИХЬ(EPAD)гаЪБЛсБЛКіЪгЃЌЕЋЫќЖдГфЗжЗЂЛгаХКХСДЕФадФмвдМАЦїМўГфЗжЩЂШШЗЧГЃживЊЁЃ ТуТЖКИХЬЃЌADIЙЋЫОГЦжЎЮЊв§НХ0ЃЌЪЧФПЧАДѓЖрЪ§ЦїМўЯТЗНЕФКИХЬЁЃЫќЪЧвЛИіживЊЕФСЌНгЃЌаОЦЌЕФЫљгаФкВПНгЕиЖМЪЧЭЈЙ§ЫќСЌНгЕНЦїМўЯТЗНЕФжааФЕуЁЃВЛжЊФњЪЧЗёзЂвтЕНЃЌФПЧАаэЖрзЊЛЛЦїКЭЗХДѓЦїжаШБЩйНгЕив§НХЃЌдвђОЭдкгкТуТЖКИХЬЁЃ ЙиМќЪЧНЋДЫв§НХЭзЩЦЙЬЖЈ(МДКИНг)жСPCBЃЌЪЕЯжРЮППЕФЕчЦјКЭШШСЌНгЁЃШчЙћДЫСЌНгВЛРЮЙЬЃЌОЭЛсЗЂЩњЛьТвЃЌЛЛбджЎЃЌЩшМЦПЩФмЮоаЇЁЃ ЪЕЯжзюМбСЌНг РћгУТуТЖКИХЬЪЕЯжзюМбЕчЦјКЭШШСЌНггаШ§ИіВНжшЁЃЪзЯШЃЌдкПЩФмЕФЧщПіЯТЃЌгІдкИїPCBВуЩЯИДжЦТуТЖКИХЬЃЌетбљзіЕФФПЕФЪЧЮЊСЫгыЫљгаНгЕиКЭНгЕиВуаЮГЩУмМЏЕФШШСЌНгЃЌДгЖјПьЫйЩЂШШЁЃДЫВНжшгыИпЙІКФЦїМўМАОпгаИпЭЈЕРЪ§ЕФгІгУЯрЙиЁЃдкЕчЦјЗНУцЃЌетНЋЮЊЫљгаНгЕиВуЬсЙЉСМКУЕФЕШЕчЮЛСЌНгЁЃ ЩѕжСПЩвддкЕзВуИДжЦТуТЖКИХЬ(МћЭМ1)ЃЌЫќПЩвдгУзїШЅёюЩЂШШНгЕиЕуКЭАВзАЕзВрЩЂШШЦїЕФЕиЗНЁЃ

ЭМ1. ТуТЖКИХЬВМОжЪОР§ ЦфДЮЃЌНЋТуТЖКИХЬЗжИюГЩЖрИіЯрЭЌЕФВПЗжЃЌШчЭЌЦхХЬЁЃдкДђПЊЕФТуТЖКИХЬЩЯЪЙгУЫПЭјНЛВцИёеЄЃЌЛђЪЙгУзшКИВуЁЃДЫВНжшПЩвдШЗБЃЦїМўгыPCBжЎМфЕФЮШЙЬСЌНгЁЃдкЛиСїКИзщзАЙ§ГЬжаЃЌЮоЗЈОіЖЈКИИрШчКЮСїЖЏВЂзюжеСЌНгЦїМўгыPCBЁЃСЌНгПЩФмДцдкЃЌЕЋЗжВМВЛОљЁЃПЩФмжЛЕУЕНвЛИіСЌНгЃЌВЂЧвСЌНгКмаЁЃЌЛђепИќдуИтЃЌЮЛгкЙеНЧДІЁЃНЋТуТЖКИХЬЗжИюЮЊНЯаЁЕФВПЗжПЩвдШЗБЃИїИіЧјгђЖМгавЛИіСЌНгЕуЃЌЪЕЯжИќРЮППЁЂОљдШСЌНгЕФТуТЖКИХЬ(МћЭМ2КЭЭМ3)ЁЃ

ЭМ2. EPADВМОжВЛЕБЕФЪОР§

ЭМ3. НЯМбEPADВМОжЪОР§ зюКѓЃЌгІЕБШЗБЃИїВПЗжЖМгаЙ§ПзСЌНгЕНЕиЁЃИїЧјгђЭЈГЃЖМКмДѓЃЌзувдЗХжУЖрИіЙ§ПзЁЃзщзАжЎЧАЃЌЮёБигУКИИрЛђЛЗбѕЪїжЌЬюГфУПИіЙ§ПзЃЌетвЛВНЗЧГЃживЊЃЌПЩвдШЗБЃТуТЖКИХЬКИИрВЛЛсЛиСїЕНетаЉЙ§ПзПеЖДжаЃЌгАЯье§ШЗСЌНгЁЃ зюКѓЃЌгІЕБШЗБЃИїВПЗжЖМгаЙ§ПзСЌНгЕНЕиЁЃИїЧјгђЭЈГЃЖМКмДѓЃЌзувдЗХжУЖрИіЙ§ПзЁЃзщзАжЎЧАЃЌЮёБигУКИИрЛђЛЗбѕЪїжЌЬюГфУПИіЙ§ПзЃЌетвЛВНЗЧГЃживЊЃЌПЩвдШЗБЃТуТЖКИХЬКИИрВЛЛсЛиСїЕНетаЉЙ§ПзПеЖДжаЃЌгАЯье§ШЗСЌНгЁЃ ШЅёюКЭВуЕчШн гаЪБЙЄГЬЪІЛсКіТдЪЙгУШЅёюЕФФПЕФЃЌНіНідкЕчТЗАхЩЯЗжЩЂДѓаЁВЛЭЌЕФаэЖрЕчШнЃЌЪЙНЯЕЭзшПЙЕчдДСЌНгЕНЕиЁЃЕЋЮЪЬтвРОЩЃКашвЊЖрЩйЕчШнЃПаэЖрЯрЙиЮФЯзБэУїЃЌБиаыЪЙгУДѓаЁВЛЭЌЕФаэЖрЕчШнРДНЕЕЭЙІТЪДЋЪфЯЕЭГ(PDS)ЕФзшПЙЃЌЕЋетВЂВЛЭъШЋе§ШЗЁЃЯрЗДЃЌНіашбЁдёе§ШЗДѓаЁКЭе§ШЗжжРрЕФЕчШнОЭФмНЕЕЭPDSзшПЙЁЃ

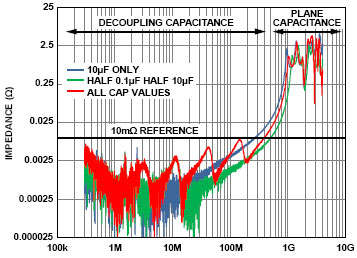

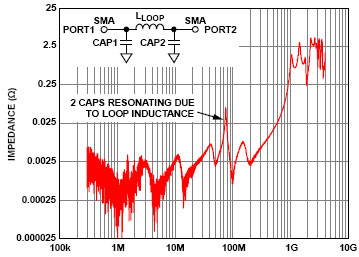

ЭМ4. ЕчШнЪОР§ Р§ШчЃЌПМТЧЩшМЦвЛИі10 mІИВЮПМВуЃЌШчЭМ4ЫљЪОЁЃШчКьЩЋЧњЯпЫљЪОЃЌЯЕЭГЕчТЗАхЩЯЪЙгУаэЖрВЛЭЌжЕЕФЕчШнЃЌ0.001ІЬFЁЂ0.01ІЬFЁЂ0.1ІЬFЕШЕШЁЃетЕБШЛПЩвдНЕЕЭ500 MHzЦЕТЪЗЖЮЇФкЕФ зшПЙЃЌЕЋЪЧЃЌЧыПДТЬЩЋЧњЯпЃЌЭЌбљЕФЩшМЦНіЪЙгУ0.1ІЬFКЭ10ІЬFЕчШнЁЃетжЄУїЃЌШчЙћЪЙгУе§ШЗЕФЕчШнЃЌдђВЛашвЊШчДЫЖрЕФЕчШнЁЃетвВгажњгкНкЪЁПеМфКЭЮяСЯ(BOM)ГЩБОЁЃ зЂвтЃЌВЂЗЧЫљгаЕчШнЁАЩњЖјЦНЕШЁБЃЌМДЪЙЭЌвЛЙЉгІЩЬЃЌЙЄвеЁЂГпДчКЭбљЪНвВгаВюБ№ЁЃШчЙћЮДЪЙгУе§ШЗЕФЕчШнЃЌВЛТлЪЧЖрИіЕчШнЛЙЪЧМИИіВЛЭЌРраЭЃЌЖМЛсИјPDSДјРДЗДзїгУЁЃ НсЙћПЩФмЪЧаЮГЩЕчИаЛЗТЗЁЃЕчШнЗХжУВЛЕБЛђепЪЙгУВЛЭЌЙЄвеКЭаЭКХЕФЕчШн(вђЖјЖдЯЕЭГФкЕФЦЕТЪзіГіВЛЭЌЯьгІ)ЃЌБЫДЫжЎМфПЩФмЛсЗЂЩњаГеё(МћЭМ5)ЁЃ

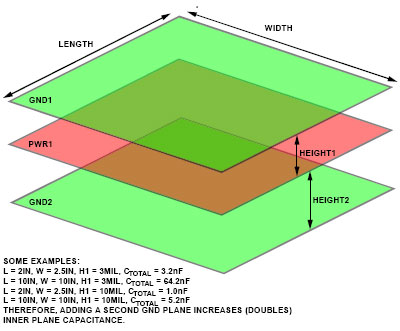

ЭМ5. аГеёЕчШн СЫНтЯЕЭГЫљгУЕчШнРраЭЕФЦЕТЪЯьгІКмживЊЁЃЫцБубЁгУЕчШнЃЌЛсШУЩшМЦЕЭзшПЙPDSЯЕЭГЕФХЌСІИЖжЎЖЋСїЁЃ PDSЕФИпЦЕВуЕчШн вЊЩшМЦГіКЯИёЕФPDSЃЌашвЊЪЙгУИїжжЕчШн(МћЭМ4)ЁЃPCBЩЯЪЙгУЕФЕфаЭЕчШнжЕжЛФмНЋжБСїЛђНгНќжБСїЦЕТЪжСдМ500 MHzЗЖЮЇЕФзшПЙНЕЕЭЁЃИпгк500 MHzЦЕТЪЪБЃЌЕчШнШЁОігкPCBаЮГЩЕФФкВПЕчШнЁЃзЂвтЃЌЕчдДВуКЭНгЕиВуНєУмЕўжУЛсгаАяжњЁЃ гІЕБЩшМЦвЛИіжЇГжНЯДѓВуЕчШнЕФPCBВуЕўНсЙЙЁЃР§ШчЃЌСљВуЖбЕўПЩФмАќКЌЖЅВПаХКХВуЁЂЕквЛНгЕиВуЁЂЕквЛЕчдДВуЁЂЕкЖўЕчдДВуЁЂЕкЖўНгЕиВуКЭЕзВПаХКХВуЁЃЙцЖЈЕквЛНгЕиВуКЭЕквЛЕчдДВудкВуЕўНсЙЙжаБЫДЫППНќЃЌетСНВуМфОрЮЊ2ЕН4УмЖћЃЌаЮГЩвЛИіЙЬгаИпЦЕВуЕчШнЁЃДЫЕчШнЕФзюДѓгХЕуЪЧЫќЪЧУтЗбЕФЃЌжЛашдкPCBжЦдьБЪМЧжазЂУїЁЃШчЙћБиаыЗжИюЕчдДВуЃЌЭЌвЛВуЩЯгаЖрИіVDDЕчдДЙьЃЌдђгІЪЙгУОЁПЩФмДѓЕФЕчдДВуЁЃВЛвЊСєЯТПеЖДЃЌЭЌЪБгІзЂвтУєИаЕчТЗЁЃетНЋЪЙИУVDDВуЕФЕчШнзюДѓЁЃ ШчЙћЩшМЦдЪаэДцдкЖюЭтЕФВу(ЩЯР§жаЃЌДгСљВуБфЮЊАЫВу)ЃЌдђгІНЋСНИіЖюЭтЕФНгЕиВуЗХдкЕквЛКЭЕкЖўЕчдДВужЎМфЁЃдкКЫаФМфОрЭЌбљЮЊ2ЕН3УмЖћЕФЧщПіЯТЃЌДЫЪБВуЕўНсЙЙЕФЙЬгаЕчШнНЋМгБЖ(ЪОР§МћЭМ6)ЁЃ гыЬэМгИќЖрЗжСЂИпЦЕЕчШнвддкИпЦЕЪББЃГжЕЭзшПЙЯрБШЃЌДЫНсЙЙИќвзгкЩшМЦЁЃ

ЭМ6. ИпЦЕВуЕчШнЪОР§ PDSЕФШЮЮёЪЧНЋЯьгІЕчдДЕчСїашЧѓЖјВњЩњЕФЕчбЙЮЦВЈНЕжСзюЕЭЃЌетЕуКмживЊЕЋГЃБЛКіТдЁЃЫљгаЕчТЗЖМашвЊЕчСїЃЌгааЉЕчТЗашЧѓСПНЯДѓЃЌгааЉЕчТЗдђашвЊвдНЯПьЕФЫйТЪЬсЙЉЕчСїЁЃВЩгУГфЗжШЅёюЕФЕЭзшПЙЕчдДВуЛђНгЕиВувдМАСМКУЕФPCBВуЕўЃЌгажњгкНЋвђЕчТЗЕФЕчСїашЧѓЖјВњЩњЕФЕчбЙЮЦВЈНЕжСзюЕЭЁЃР§ШчЃЌИљОнЫљгУЕФШЅёюВпТдЃЌШчЙћЯЕЭГЩшМЦЕФПЊЙиЕчСїЮЊ1 AЃЌPDSЕФзшПЙЮЊ10 mІИЃЌдђзюДѓЕчбЙЮЦВЈЮЊ10 mVЁЃМЦЫуКмМђЕЅЃКV = IRЁЃ ЦОНшЭъУРЕФPCBЖбЕўЃЌПЩИВИЧИпЦЕЗЖЮЇЃЌЭЌЪБдкЕчдДВуЦ№ЪМШыПкЕуКЭИпЙІТЪЛђРЫгПЕчСїЦїМўжмЮЇЪЙгУДЋЭГШЅёюЃЌПЩИВИЧЕЭЦЕЗЖЮЇ(<500 MHz)ЁЃетПЩШЗБЃPDSзшПЙдкећИіЦЕТЪЗЖЮЇФкОљзюЕЭЁЃУЛгаБивЊИїДІЖМХфжУЕчШнЃЛЕчШне§ЖдзХУПИіICЗХжУЛсЦЦЛЕаэЖржЦдьЙцдђЁЃШчЙћашвЊетжжбЯРїЕФДыЪЉЃЌдђЫЕУїЕчТЗДцдкЦфЫќЮЪЬтЁЃ ВуёюКЯ вЛаЉВМОжВЛПЩБмУтЕиОпгажиЕўЕчТЗВу(МћЭМ7)ЁЃгааЉЧщПіЯТЃЌПЩФмЪЧУєИаФЃФтВу(Р§ШчЕчдДЁЂНгЕиЛђаХКХ)ЃЌЯТЗНЕФвЛВуЪЧИпдыЩљЪ§зжВуЁЃ

ЭМ7. НЛВцёюКЯВуЪОР§ етГЃГЃБЛКіТдЃЌвђЮЊИпдыЩљВуЪЧдкСэвЛВуЁЊЁЊдкУєИаЕФФЃФтВуЯТЗНЁЃШЛЖјЃЌвЛИіМђЕЅЕФЪЕбщОЭПЩвджЄУїЪТЪЕВЂЗЧШчДЫЁЃвдФГвЛВуУцЮЊР§ЃЌдкШЮвЛВузЂШыаХКХЁЃНгзХСЌНгСэвЛВуЃЌНЋИУЯрСкВуНЛВцёюКЯжСЦЕЦзЗжЮівЧЁЃёюКЯЕНЯрСкВуЕФаХКХСПШчЭМ8ЫљЪОЁЃМДЪЙМфОр40УмЖћЃЌФГжжвтвхЩЯЫќШдЪЧЕчШнЃЌвђДЫдкФГаЉЦЕТЪЯТШдЛсёюКЯаХКХжСЯрСкВуЁЃ

ЭМ8. НЛВцёюКЯВуЪЕВтНсЙћ ЭМ8ЯдЪОСЫетбљЕФвЛИіР§згЁЃОйР§РДЫЕЃЌМйЩшвЛИіВуУцЩЯЕФИпдыЩљЪ§зжВуОпгаИпЫйПЊЙиЕФ1 VаХКХЁЃетвтЮЖзХЃЌСэвЛВуНЋПДЕН1 mVЕФёюКЯ(дМ60 dBИєРы)ЁЃЖдОпга2-V p-pТњСПГЬАкЗљЕФ12ЮЛADCЃЌетЪЧ2 LSBЕФёюКЯЁЃЖдгкЬиЖЈЕФЯЕЭГетПЩФмВЛГЩЮЪЬтЃЌЕЋгІзЂвтЃЌШчЙћЯЕЭГЕФСщУєЖШЬсЩ§СНЮЛЃЌДг12ЮЛдіжС14ЮЛЃЌДЫёюКЯЕФСщУєЖШжЛЛсЬсИпЫФБЖЃЌМД8 LSBЁЃ КіТдДЫРраЭЕФНЛВцВуёюКЯПЩФмЪЙЯЕЭГЪЇаЇЃЌЛђепЯїШѕЩшМЦЁЃБиаызЂвтЃЌСНВужЎМфДцдкЕФёюКЯПЩФмГЌГіЯыЯѓЁЃдкФПБъЦЕЦзФкЗЂЯждыЩљдгЩЂёюКЯЪБгІзЂвтетвЛЕуЁЃгаЪБВМОжОіЖЈСЫЗЧдЄЦкаХКХЛђВугІНЛВцёюКЯжСВЛЭЌВуЁЃЭЌбљЃЌЕїЪдУєИаЯЕЭГЪБгІзЂвтетвЛЕуЁЃИУЮЪЬтПЩФмГіЯждкЯТУцвЛВуЁЃ ЗжРыНгЕи ФЃФтаХКХСДЩшМЦШЫдБзюГЃЬсГіЕФЮЪЬтЪЧЃКЪЙгУADCЪБЪЧЗёгІНЋНгЕиВуЗжЮЊAGNDКЭDGNDНгЕиВуЃПМђЕЅЛиД№ЪЧЃКЪгЧщПіЖјЖЈЁЃ ЯъЯИЛиД№дђЪЧЃКЭЈГЃВЛЗжРыЁЃЮЊЪВУДВЛФиЃПвђЮЊдкДѓЖрЪ§ЧщПіЯТЃЌУЄФПЗжРыНгЕиВужЛЛсдіМгЗЕЛиТЗОЖЕФЕчИаЃЌЫќЫљДјРДЕФЛЕДІДѓгкКУДІЁЃ ДгЙЋЪНV = L(di/dt)ПЩвдПДГіЃЌЫцзХЕчИадіМгЃЌЕчбЙдыЩљЛсЬсИпЁЃЫцзХЕчИадіМгЃЌЩшМЦШЫдБвЛжБХЌСІбЙЕЭЕФPDSзшПЙвВЛсдіМгЁЃЫцзХЬсИпADCВЩбљЫйТЪЕФашЧѓМЬајдіГЄЃЌНЕЕЭПЊЙиЕчСї(di/dt)ЕФЗНЪНШДКмгаЯоЁЃвђДЫЃЌГ§ЗЧашвЊЗжРыНгЕиВуЃЌЗёдђЧыБЃГжетаЉНгЕиСЌНгЁЃ ЙиМќЪЧЕчТЗЗжИювЊКЯРэЃЌетбљОЭВЛБиЗжРыНгЕиВуЃЌШчЭМ9ЫљЪОЁЃзЂвтЃЌШчЙћВМОждЪаэФњНЋЕчТЗБЃГждкИїздЧјгђФкЃЌБуВЛашвЊЗжРыНгЕиВуЁЃШчДЫЗжИюПЩЬсЙЉаЧаЭНгЕиЃЌДгЖјНЋЗЕЛиЕчСїОжЯодкЬиЖЈЕчТЗВПЗжЁЃ

ЭМ9. СМКУЕчТЗЗжИюЪОР§ Р§ШчЃЌЪмГпДчЯожЦЕФгАЯьЃЌЕчТЗАхЮоЗЈЪЕЯжСМКУЕФВМОжЗжИюЪБЃЌОЭашвЊЗжРыНгЕиВуЁЃетПЩФмЪЧЮЊСЫЗћКЯДЋЭГЩшМЦвЊЧѓЛђГпДчЃЌБиаыНЋдрТвЕФзмЯпЕчдДЛђИпдыЩљЪ§зжЕчТЗЗХдкФГаЉЧјгђЁЃетжжЧщПіЯТЃЌЗжРыНгЕиВуЪЧЪЕЯжСМКУадФмЕФЙиМќЁЃШЛЖјЃЌЮЊЪЙећЬхЩшМЦгааЇЃЌБиаыдкЕчТЗАхЕФФГИіЕиЗНЭЈЙ§вЛИіЕчЧХЛђСЌНгЕуНЋетаЉНгЕиВуСЌдквЛЦ№ЁЃвђДЫЃЌгІНЋСЌНгЕуОљдШЕиЗжВМдкЗжРыЕФНгЕиВуЩЯЁЃ зюжеЃЌPCBЩЯЭљЭљЛсгавЛИіСЌНгЕуГЩЮЊЗЕЛиЕчСїЭЈЙ§ЖјВЛЛсЕМжТадФмНЕЕЭЛђЧПааНЋЗЕЛиЕчСїёюКЯжСУєИаЕчТЗЕФзюМбЮЛжУЁЃШчЙћДЫСЌНгЕуЮЛгкзЊЛЛЦїЁЂЦфИННќЛђЯТЗНЃЌдђВЛашвЊЗжРыНгЕиЁЃ НсЪјгя гЩгкзюМббЁЯюЬЋЖрЃЌВМОжПМТЧзмЪЧСюШЫРЇЛѓЁЃММЪѕКЭддђвЛжБЪЧЙЋЫОЩшМЦЮФЛЏЕФвЛВПЗжЁЃЙЄГЬЪІЯВЛЖНшМјвдЧАЩшМЦжаЕФОбщЃЌЭЌЪБВњЦЗЩЯЪабЙСІЪЙЩшМЦШЫдБВЛдИИќИФЛђГЂЪдаТММЪѕЁЃЫћУЧОаФргкЗчЯеШЈКтЃЌжБжСЯЕЭГФкГіЯжжиДѓЮЪЬтЁЃ дкЦРЙРАхЁЂФЃПщКЭЯЕЭГМЖБ№ЃЌМђЕЅЕФЕЅвЛНгЕизюМбЁЃСМКУЕФЕчТЗЗжИюЪЧЙиМќЁЃетвВгАЯьЕНВуКЭЯрСкВуВМОжЁЃШчЙћУєИаВудкИпдыЩљЪ§зжВувдЩЯЃЌЧызЂвтПЩФмЛсЗЂЩњНЛВцёюКЯЁЃзщзАвВКмживЊЃЛЬсЙЉИјPCBГЕМфЛђзщзАГЕМфЕФжЦдьБЪМЧгІЩЦМгРћгУЃЌШЗБЃICТуТЖКИХЬКЭPCBжЎМфОпгаПЩППСЌНгЁЃ зщзАВЛСМГЃГЃЕМжТЯЕЭГадФмЧЗМбЁЃППНќЕчдДВуШыПкЕуКЭзЊЛЛЦїЛђICЕФVDDв§НХЕФШЅёюзмЪЧгаРћЕФЁЃШЛЖјЃЌЮЊСЫдіМгЙЬгаИпЦЕШЅёюЕчШнЃЌгІЪЙгУНєУмЕўжУЕФЕчдДКЭНгЕиВу(МфОрЁм4УмЖћ)ЁЃДЫЗНЗЈВЛЛсДјРДЖюЭтГЩБОЃЌжЛашЛЈМИЗжжгИќаТPCBжЦдьБЪМЧЁЃ ЩшМЦИпЫйЁЂИпЗжБцТЪзЊЛЛЦїВМОжЪБЃЌКмФбееЙЫЕНЫљгаЕФОпЬхЬиадЁЃУПИігІгУЖМЪЧЖРвЛЮоЖўЕФЁЃЯЃЭћБОгІгУБЪМЧЫљЪіЕФМИИівЊЕугажњгкЩшМЦЙЄГЬЪІИќКУЕиСЫНтЮДРДЕФЯЕЭГЩшМЦЁЃ ЯТдидЮФЃК  AN-1142.pdf

(392.98 KB)

AN-1142.pdf

(392.98 KB)

|

ЭјгбЦРТл