半导体制造朝8nm节点技术迈进 电子束光刻法获突破

发布时间:2012-4-11 11:27

发布者:李宽

|

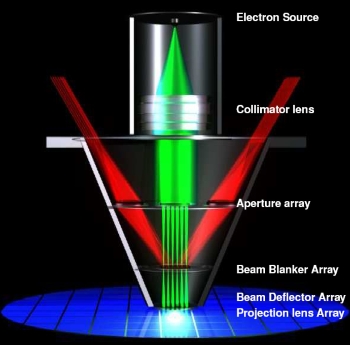

稍早前,IEEE举办的国际物理设计研讨会(ISPD)中,与会专家探讨了半导体制造朝8nm节点迈进的可能性。尽管目前有三种相互竞争的工具可用于量产,但未来的发展道路仍然荆棘遍布。来自台积电(TSMC)的研究员Burn Lin表示,无论采用这三种方法中的哪一种,都必须先克服微缩到8nm设计规则的障碍。 这三种方法分别是采用多重图案(multi-patterning)辅助的193nm浸入式光刻技术;超紫外光(EUV)光刻;以及电子束光刻(e-beam lithography)。据Lin表示,浸入式光刻已经接近真正可实现的阶段了,但它仍面临着不断上升的成本障碍。EUV在13.5nm波长已经证实能用于次20nm设计规则,但它需要更好的聚焦机制和可实现更高产出的光源,以克服低于65%的光学反射率问题。而今天,我们已经知道电子束能够用于8nm节点,但由于它的速度太慢、吞吐量过低,因此被视为最后一个技术选项。 为了解决电子束的吞吐量问题,Lin表示他们已经在KLA-Tencor和Mapper Lithography BV设备上采用大规模平行电子束,即同时让数千个电子束来加快吞吐量,但目前仅在可靠性、一致性和精确性方面获得改善。 在今年度的ISPD中,其中一篇最佳论文提名,是来自于台大教授张耀文(Yao-Wen Chang)带领的研究团队,该论文探讨了藉由重新排列写入顺序来解决大规模电子束写入过程中的过热问题, 以便更好地控制维度扭曲。 IBM Research的科学家Shayak Banerjee则说明如何在多边形布局上形塑容差,这对更先进节点光刻技术将有所助益。他同时说明了运用掩膜和布局最佳化来控制这些多边形的两种制造方法。

为了向8nm节点目标迈进,Mapper Lithography公司让超过10万个电子光束同时运作╱资料来源:Mapper Lithography 3D架构忆阻器 加州大学圣塔巴巴拉分校教授Tim Cheng的论文描述了如何运用3D技术来实现梦幻半导体──忆阻器(memristor)。 采用混合3D整合技术,Cheng的存储器架构在密度达每平方公分100,000Gb,以及频宽达每秒10亿Gb的纵横闩(crossbar)垂直线中夹入忆阻材料(memristive material)。 该设计的最大挑战,是必须克服基于纵横闩元件的细粒维度和芯片接口引脚的失配情况,Cheng已经克服了新的3D过孔朝接口引脚方向倾斜的挑战。 而最佳论文奖则由爱荷华州立大学(Iowa State University)教授Chirs Chu获得,他提出了一种可在VLSI固定摆置范围平面规划中检测最佳化电路模组外形的演算法,与之前最先进的技术相比,其效能可提升10~100倍。 ISPD同时宣布向台湾清华大学教授刘炯朗(Dave CL Liu)致意,他稍早前才获得了ISPD颁发的菲尔卡夫曼奖(Phil Kaufman Award),用以表扬他在VLSI电路物理设计方面的杰出成就。 |

网友评论