进军服务器市场,RISC-V能否与X86一战?

发布时间:2023-9-15 08:50

发布者:eechina

|

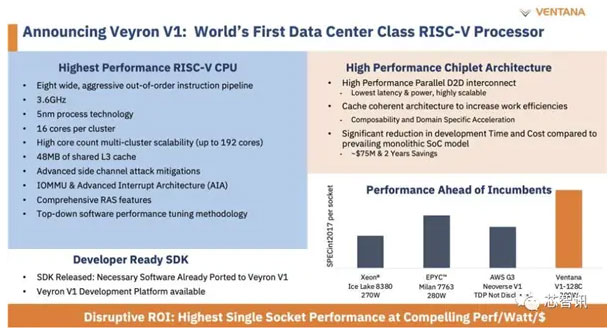

来源:芯智讯 众所周知,目前x86架构处理器统治着PC和服务器市场,而Arm架构处理器则统治着移动市场,并在IoT市场占据着较大的市场份额。 但是,近年来RISC-V架构则凭借着开源、指令精简、可扩展等优势,在注重能效比的物联网领域大受追捧。 在RISC-V International及相关芯片厂商的推动下,RISC-V也开始进入更高性能需求的服务器市场。 2023年初,RISC-V International将HPC确定为RISC-V增长的战略优先领域,再加上最近批准的矢量扩展和大量移植关键HPC库和工具的HPC软件工作,很明显,这一领域的势头正在迅速增长。 世界各地的很多项目,如欧洲eProcessor项目、拥有上千RISC-V核心的Esperanto CPU,以及旨在开发RISC-V关键软件组件支持的多供应商RISE项目,都有可能推动RISC-V在包括HPC在内的高端计算中普及,并最终使社区能够围绕这一技术构建超级计算机。 此外,早期的应用研究对RISC-V可以为高性能工作负载带来的好处也表示赞同。 2022年12月,芯片初创企业Ventana Microsystems公司在RISC-V峰会上发布了全球首款面向服务市场的基于RISC-V架构的最高192核CPU——Veyron V1。 据介绍,Veyron V1采用先进的5nm制程工艺,基于Ventana自研的高性能RISC-V内核,8流水线设计,支持乱序执行,主频高达3.6GHz,每个集群最多16个内核,多集群最多可扩展至192核,拥有48MB共享三级缓存,拥有高级侧信道攻击缓解措施、IOMMU和高级中断架构(AIA)、支持全面的RAS功能、自上而下的软件性能调整方法,可以满足数据中心的各种需求。

根据Ventana披露的数据显示,在SPECint 2017测试中,128核心版本的Veyron V1在300W功耗下,大幅性能领先于64核的AMD EPYC Milan 7763(280W),并且达到了64核心AWS Graviton G3(Neoverse v1内核)、40核心Intel Xeon Ice Lake 8380(270W)的两倍。当然这也主要得益于其核心数量达到了竞品的两倍。 需要指出的是,Veyron V1并没有SIMD或向量执行单元,这对上有AVX-512的Intel或AMD的服务器处理器会非常吃亏。 另外,Veyron V1目前还没有量产,之前承诺的是今年第二季或第三季向客户提供样品。所以,以上官方公布的数据都还是纸面上的数据。 相比之下,今年三月国内某厂商推出的64核RISC-V服务器芯片SG2042目前已经小批量出货。 近日,国外研究人员Nick Brown 通过RAJAPerf基准测试套件对于这款芯片进行了实测,发现其与最新的广泛可用的RISC-V芯片相比,其平均每个核心的性能提高了5到10倍。但是在多线程工作负载下,x86高性能CPU的平均性能依然达到了它的4-8倍。 据该研究报告显示,该64核RISC-V处理器,运行频率为2GHz,由四个高性能的C920内核组成,并采用了12级无序多问题超标量管道设计。 C920提供RV64GCV指令集,具有三个解码、四个重命名/调度、八个发布/执行和两个加载/存储执行单元。支持矢量化标准扩展(RVV v0.7.1),矢量宽度为128位,支持数据类型FP16、FP32、INT8、INT16、INT32和INT64。然而,C920并不支持FP64矢量化 研究称,双精度浮点是绝大多数高性能工作负载的基础,因此能够支持矢量化这些操作的核心可能会为HPC提供更高的性能。每个C920核心还包含64KB的L1指令(I)和数据(D)缓存,1MB的L2缓存,在四个核心的集群之间共享,64MB的L3系统缓存,由集群中的所有核心共享。还提供四个DDR4-3200内存控制器和32条PCIe Gen4通道。 HPC工作负载的一个重要考虑因素是矢量化,由于C920核心仅支持RVV v0.7.1,编译器支持是一个挑战。RISC-V GNU编译器的当前上游版本不支持任何版本的矢量扩展。虽然GNU存储库包含一个rvv下一个分支,其目的是支持rvv v1.0,但在研究人员撰写研究报告时,它并没有得到积极维护。 此外,还有一个针对rvv v0.7.1的rvv-0.7.1分支,但该分支已被删除。由于缺乏对主线GCC的支持,阿里平头哥(T-Head)提供了自己的GNU编译器分支(玄铁GCC),该编译器已针对其处理器进行了优化。 T-Head的定制编译器同时支持RVV v0.7.1和他们自己定制的自定义扩展。虽然已经提供了该编译器的几个版本,但作为其20210618版本的一部分,GCC8.4提供了最佳的自动向量化能力,因此这是研究人员进行的基准测试实验选择的版本。 该版本的编译器生成矢量长度特定(VLS)RVV组件,该组件专门针对C920的128位矢量宽度。所有内核都在优化级别三进行编译,所有报告的结果都在五次运行中取平均值。 与其他高性能RISC-V内核比较 研究人员比较了SG2042与赛昉(StarFive)开发板VisionFive V1和 Vision V2的性能,V1包含赛昉JH7100 SoC,而V2包含赛昉JH7110 SoC。 JH7100和JH7110这两个SoC都是基于64位RISC-V SiFive U74内核构建的,JH7100包含两个内核,JH7110包含四个内核。SoC被列为以1.5GHz运行,U74内核包含32KB(D)和32KB(I)L1缓存,两种SoC型号还包含内核之间共享的2MB L2缓存。 然而,SiFive U74仅提供RV64GC,因此不支持RISC-V矢量扩展。

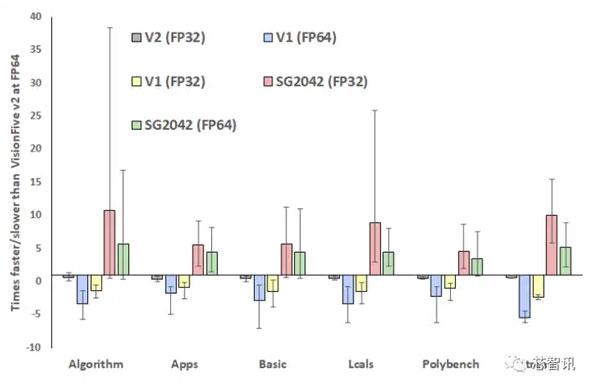

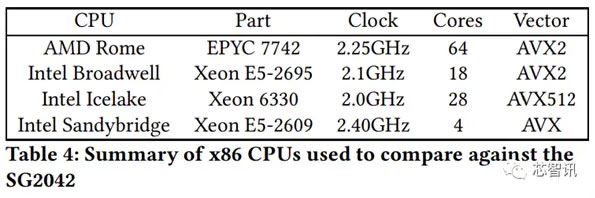

图1展示了VisionFive V2和V1与SG2042在双精度(FP64)和单精度(FP32)方面的单核性能比较。其中条形图是整个类别中速度更快或更慢的平均次数,线条的范围从最大到最小。 从图1中可以看出,单个C920核心在双精度和单精度方面都优于V2和V1的U74核心。 在双倍精度下,C920核心的平均性能是V2中U74以双倍精度运行时的4.3至6.5倍。此外,在单精度下,C920的性能是基准测试平均性能的5.6至11.8倍。这是一个令人印象深刻的性能提升,并且C920内核上没有比U74运行得慢的内核。 一些内核在C920上的性能非常令人印象深刻,例如,来自算法组的内存集基准在FP32中的运行速度是U74的40倍,在FP64中运行速度是U74的18倍。 需要强调的是,该基准测试在这些核心上都是以尽可能好的配置,即C920上利用了矢量化,但是U74不支持矢量化,因此在V1或V2上不可用。 SG2042上的FP32和FP64之间存在显著的性能差异,这表明事实上C920矢量运算不支持FP64。相比之下,在V2上运行双精度和单精度之间的性能差异要小得多。 图1中结果的一个方面让研究人员感到惊讶的是,VisionFive V1比V2慢得多。考虑到测试只是在单核上运行RAJAPerf,所以芯片的双核和四核性质并不重要,因为它们都包含相同的U74核心,那么其性能应该相当相似。 但是,在双倍精度下,V1比V2慢了六倍到三倍,单精度则慢了一倍到三倍。虽然可以假设V1可能以比V2更低的时钟频率运行,尽管它们在数据表中都被列为以1.5GHz运行,但机器上没有任何文件或输出可以证实这一点。 从图1中可以看出,与现有的、公开可用的商品RISC-V内核相比,单个C920核心所获得的性能令人印象深刻。T-Head将该核心描述为一种高性能RISC-V处理器。 测试也表明,其与U74相比,在整个基准测试套件中的性能有了很大的提高,U74以前被认为是广泛可用的RISC-V CPU的最佳选择,可以在其上进行HPC工作负载的实验。 除了单核性能外,SG2042在核数量方面也显著领先于V1的JH7100和V2的JH7110 SoC。 与x86服务器CPU性能比较 那么相对于其他商用的x86服务器芯片,SG2042在HPC工作负载中的表现如何呢? 对此,研究人员将其与当前一代服务器中使用的其他CPU进行了比较,分别为64核的AMD Rome EPYC 7742、18核的Intel Broadwell Xeon E5-2695、28核的Intel IceLake Xeon 6330、4核心的Intel SandyBridge Xeon E5-2609。 测试只在这些x86 CPU的物理内核上执行,因为默认情况下禁用了所有SMT。

AMD EPYC 7742在四个NUMA区域中包含64个物理内核,每个区域有16个内核,但有八个内存控制器。每个核心包含32KB(I)和32KB(D)L1缓存,512KB的L2缓存,四个核心之间共享16MB的L3缓存。EPYC 7742提供支持AVX2,具有256位宽的矢量寄存器,是SG2042的两倍,并支持FP64的矢量化。 Intel Xeon E5-2695的18个物理内核位于一个NUMA区域中,提供32KB(I)和32KB(D)L1缓存,256KB的L2缓存,以及45MB的跨内核共享的L3缓存。与AMD EPYC 7742类似,Xeon E5-2695支持AVX2,并且有四个内存控制器。 Intel Xeon 6330是比较的最新CPU,所有28个物理内核都在一个NUMA区域中,具有8个内存控制器,具有32KB(I)和48KB(D)L1缓存,每个内核1MB L2缓存,以及43MB共享L3缓存。Xeon 6330支持AVX512,并提供512位宽的矢量寄存器。 Intel Xeon E5-2609属于本次测试当中最古老的CPU,其于2012年发布,仅提供四个物理核,每个核都有64KB(I)和64KB(D)L1缓存,以及256KB的L2缓存和共享的10MB L3缓存。该E5-2609仅支持AVX,因此矢量寄存器长度与SG2042相同,为128位,尽管AVX支持FP64。 在所有测试当中,研究人员禁用了x86物理内核的超线程。除了ARCHER2之外,研究人员在所有系统上都使用GCC版本8.3,编译始终在优化级别O3下进行。全部在性能最高的线程数量上执行的系统。

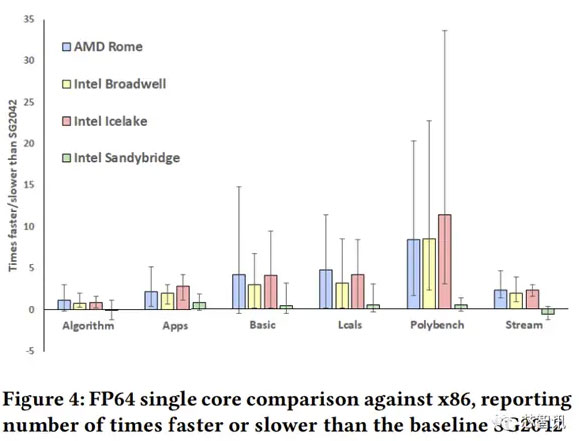

图4展示了各芯片在FP64上运行基准测试套件的单核性能。其中条形图是整个类别中速度更快或更慢的平均次数,线条的范围从最大到最小。SG2042为均值基线。 从测试结果来看,除了除了古老的Xeon E5-2609内核之外,所有x86内核的性能都优于C920,后者在流和算法基准类中的平均性能较慢。 AMD EPYC 7742和Intel Xeon 6330 CPU的表现往往优于Intel Xeon E5-2695,这是可以理解的,因为Xeon E5-2695是这三款CPU中的老款。

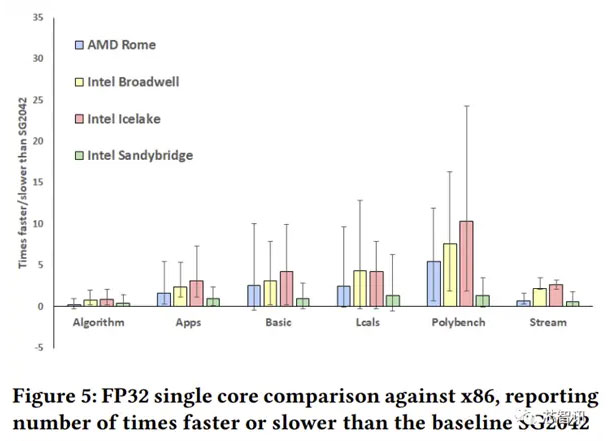

图5展示了各芯片在FP32上运行基准测试套件的单核性能与基线相比的快慢次数。 从图5可以看出,AMD EPYC 7742在单精度执行时与双倍精度执行时相当乏善可陈,而英特尔处理器的平均性能也一样好,事实上,当使用FP32时,古老的Xeon E5-2609内核在每种级别上的平均性能都优于C920。 然而,图5中的平均条形图并不能提供完整的图片。 C920仅支持FP32的矢量化,事实上,从图5和图4中的线条可以看出,FP32的许多基准类的最大速度比FP64快。 此外,有更多运行速度最慢的内核在x86 CPU上的执行速度比FP32上的C920慢。这些内核是有效应用自动矢量化的地方,事实上,可以看出,对于lcals基准类,所有x86 CPU上至少有一个内核的性能低于C920。 总结来说,在单核性能比较上,FP32下的AMD EPYC 7742平均表现要比C920快3倍,Intel Xeon E5-2695要快2倍,Intel Xeon 6330也要快4倍,Xeon E5-2609则快2倍,FP64下的这些数字则分别快4倍、4倍、5倍和20%。

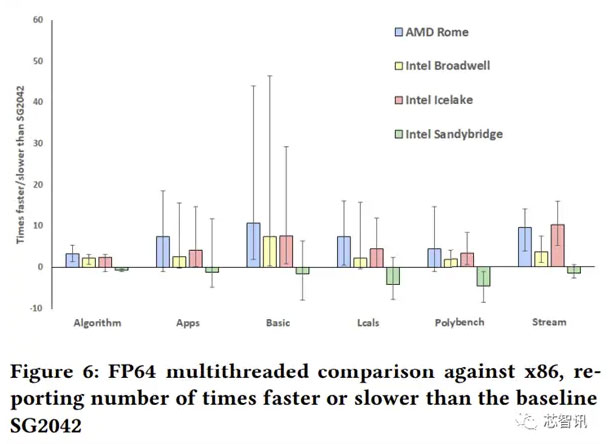

FP64多线程性能比较,报告比基线快或慢的次数 图6展示了针对双精度FP64的性能比较。 可以看出,basic、lcals、polybench和stream类测试从更多的内核中受益最大,因此SG2042的平均性能优于古老的Xeon E5-2609。

FP32多线程性能比较,报告比基线快或慢的次数 图7展示了FP32的多线程性能比较,这些结果包含最大的差异。为了提高可读性,研究人员限制了纵轴,并标记了超过该值的实际数值。 在多线程FP32方面,SG2042往往比FP64在与x86 CPU的竞争中表现得略强,尽管polybench类是一个异常,因为它在三个最新的x86 CPU上的表现要好得多,而Intel Xeon E5-2609的表现则差得多。 总结来说,在SG2042多线程性能与x86 CPU进行比较时,在FP32和FP64上运行的所有基准类型测试中,其64核平均性能优于4核的Intel Xeon E5-2609。 64核的AMD EPYC 7742在FP32和FP64方面的性能分别是SG2042的8倍和5倍。18核的Intel Xeon E5-2695在单精度和双精度方面分别平均达到了6倍和4倍。最后,28核的Intel Xeon 6330在FP32和FP64方面的表现分别是其6倍和8倍。 结论: 研究人员表示,尽管当前有许多公司在开发高性能RISC-V硬件原型,但到目前为止,当希望在可商用的RISC-V软件上运行工作负载时,选择非常有限。 不管怎样,尽管这些解决方案能够对RISC-V进行实验,但它们并不能在体系结构上提供生产高性能工作负载所需的功能。因此,尽管HPC社区对RISC-V很感兴趣,但它还没有完全准备好迎接这项技术。 当然,作为世界上第一款广泛可用的针对HPC的多核RISC-V服务器芯片,SG2042可能会大大提高HPC社区对RISC-V的兴趣和采用率。然而,一个关键的问题是其与当前一代超级计算机中普遍存在的x86 CPU相比依然有着较大的差距。 不过,与目前可商用的RISC-V硬件相比,这是一款非常令人兴奋的RISC-V服务器芯片,它提供了一些重大的变化。 虽然性能还没有达到x86服务器CPU的水平,但应该强调的是,RISC-V供应商在短时间内取得了长足的进步。相比之下,x86 CPU有着悠久的历史,并从他们多年的开发中受益。 目前RISC-V进入服务器CPU市场的竞争对手主要还是Arm服务器CPU,毕竟其理论上RISC-V CPU可以拥有相比Arm CPU更低的成本、更高的定制化和可扩展性。 对于下一代高性能RISC-V处理器来说,研究人员认为,提供RVV v1.0将非常有用,因为这将提供使用用于编译矢量化代码的主线GCC和Clang。 此外,提供FP64矢量化、更宽的矢量寄存器、增加的L1高速缓存以及每个NUMA区域更多的存储器控制器也可能带来显著的性能优势,并有助于缩小与x86高性能处理器的差距。 |

网友评论