富士通新技术:0.4V电压即可驱动芯片工作

发布时间:2011-12-13 17:17

发布者:1770309616

|

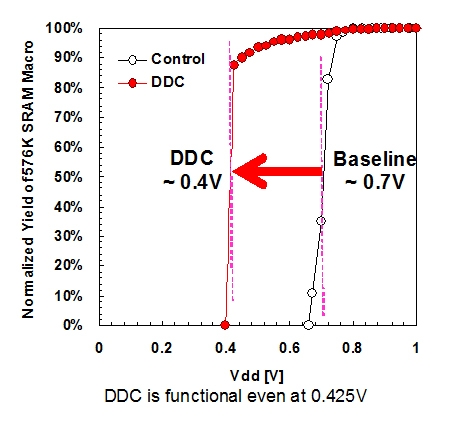

虽然芯片制程方面一直在飞速进步,不过自从进入0.18微米(180nm)时代CPU核心电压降至 1.xV级别后,即使是目前实际生产用最新的28nm制程也只能使核心电压维持在1V左右。“高”电压带来的功耗问题也使移动计算方面处处受限,目前智能手机、平板电脑等最大的问题之一就是功耗和续航。而芯片电压之所以无法突破1V的重要原因之一就是低压无法驱动内部的SRAM模块。不过上周富士通半导体和美国SuVolta公司开发的新制程却可以使电压阈值下降至0.4V左右。 SoVolta开发的DDC晶体管制造的576Kb SRAM模块最低可在0.425V电压下工作,相比目前常用SRAM最低0.7V左右的工作电压减少了40%左右。相对于效果类似的ETSOI和Tri-Gate制程,SuVolta与富士通的这种技术更加简便易行。 富士通半导体计划继续改进此技术,并应客户要求将低功耗特性全面导入对应的产品中,对于逐渐SoC化的移动处理器来说这的确是个不错的消息。

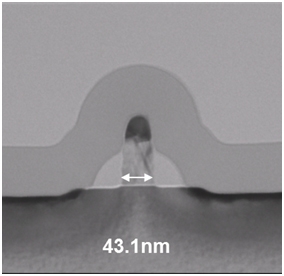

DDC晶体管与普通晶体管的阈值电压对比 |

网友评论