ADALM2000КµСйЈєCMOSВЯјµзВ·ЎўDРНЛшґжЖч

·ўІјК±јдЈє2023-6-9 17:26

·ўІјХЯЈєeechina

|

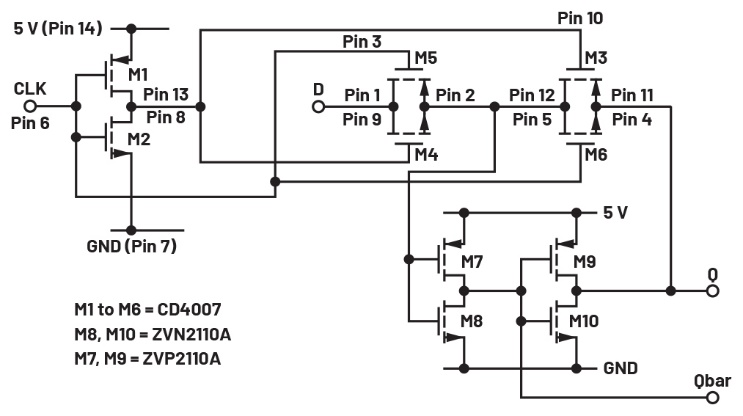

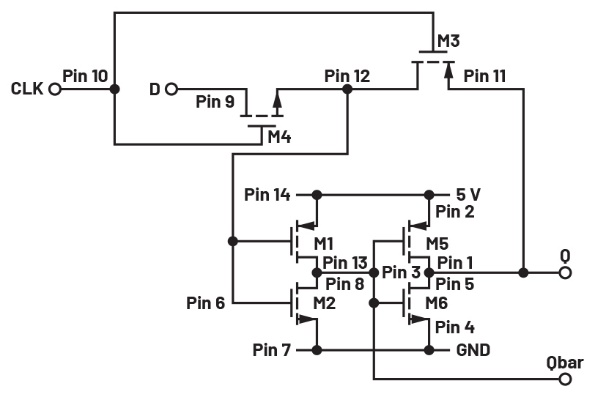

ЧчХЯЈєDoug MercerЈ¬№ЛОКСРѕїФ±єНAntoniu MiclausЈ¬ADI№«ЛѕПµНіУ¦УГ№¤іМК¦ Дї±к ±ѕКµСй»о¶ЇµДДї±кКЗЅшТ»ІЅЗї»ЇЙПТ»ёцКµСй»о¶ЇЎ°ADALM2000КµСйЈєК№УГCD4007ХуБР№№ЅЁCMOSВЯј№¦ДЬЎ±ЦРМЅМЦµДCMOSВЯј»щ±ѕФАнЈ¬Іў»сИЎёь¶аК№УГёґФУCMOSГЕј¶µзВ·µДѕСйЎЈѕЯМе¶шСФЈ¬ДъЅ«БЛЅвИзєОК№УГCMOSґ«КдГЕєНCMOS·ґПаЖчАґ№№ЅЁDРНґҐ·ўЖч»тЛшґжЖчЎЈ ±іѕ°ЦЄК¶ ОЄБЛФЪ±ѕКµСй»о¶ЇЦР№№ЅЁВЯј№¦ДЬЈ¬РиТЄК№УГADALP2000ДЈДвІїјюМЧјюЦРµДCD4007 CMOSХуБРєН·ЦБўКЅNMOSєНPMOSѕ§Ме№ЬЈЁZVN2110A NMOSєНZVP2110A PMOSЈ©ЎЈCD4007УЙ3¶Ф»ҐІ№MOSFETЧйіЙЈ¬ИзНј1ЛщКѕЎЈГї¶Ф№ІУГТ»ёц№ІХ¤ЈЁТэЅЕ6Ўў3єН10Ј©ЎЈЛщУРPMOSFETЈЁХэµзФґТэЅЕ14Ј©ТФј°NMOSFETЈЁµШТэЅЕ7Ј©µДіДµЧ¶ј№ІУГЎЈЧу±ЯµД»ҐІ№MOSFET¶ФЈ¬NMOSФґј«ТэЅЕБ¬ЅУµЅNMOSіДµЧЈЁТэЅЕ7Ј©Ј¬PMOSФґј«ТэЅЕБ¬ЅУµЅPMOSіДµЧЈЁТэЅЕ14Ј©ЎЈБнНвБЅ¶ФѕщОЄНЁУГРНЎЈУТ±ЯµД»ҐІ№MOSFET¶ФЈ¬NMOSµДВ©ј«ТэЅЕБ¬ЅУµЅPMOSµДВ©ј«ТэЅЕЈ¬јґТэЅЕ12ЎЈ

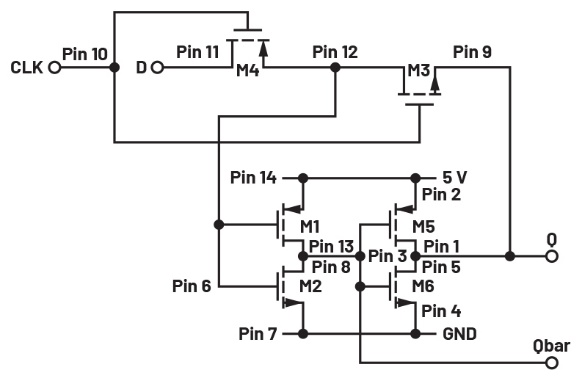

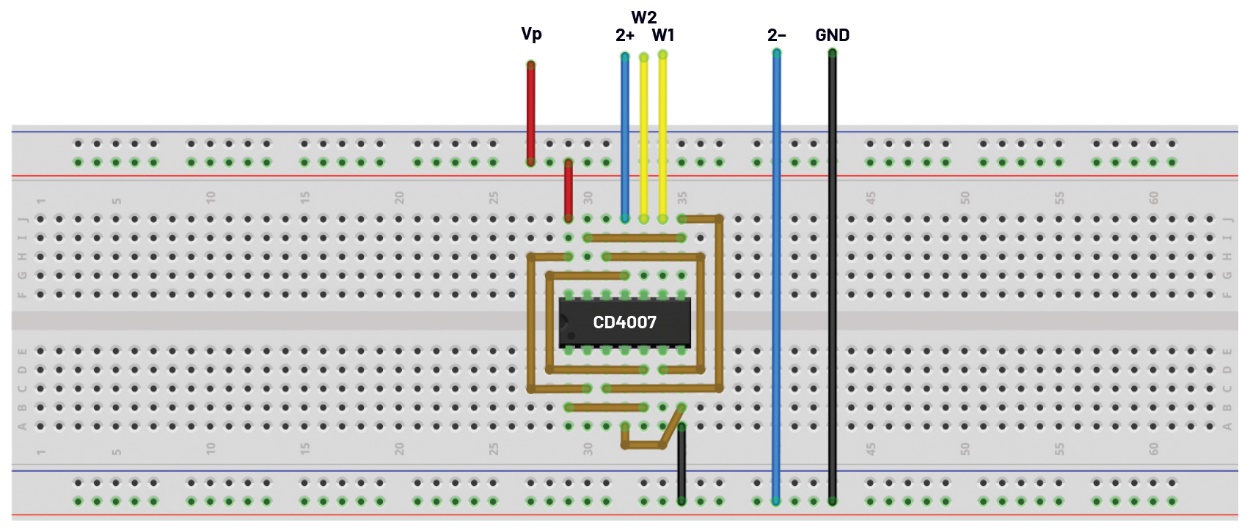

Нј1.CD4007№¦ДЬїтНјЎЈ CD4007КЗТ»їо¶а№¦ДЬICЈ¬ОТГЗФЪЙПТ»ёцКµСй»о¶ЇЦРТСУРЛщБЛЅвЎЈАэИзЈ¬µҐёцCD4007їЙУГУЪ№№ЅЁТ»ёц·ґПаЖчБґЈЁ°ьАЁИэёц·ґПаЖчЈ©ЎўТ»ёц·ґПаЖчјУЙПБЅёцґ«КдГЕ»тЖдЛыёґФУµДВЯј№¦ДЬЈ¬ИзNANDєНNORГЕЎЈ·ґПаЖчєНґ«КдГЕУИЖдККєП№№ЅЁDРНЛшґжЖч»тЦч/ЅЪµгґҐ·ўЖчЎЈ ѕІµз·Еµз CD4007УлРн¶аCMOSјЇіЙµзВ·Т»СщЈ¬єЬИЭТЧ±»ѕІµз·ЕµзЛр»µЎЈCD4007°ьАЁ¶юј«№ЬЈ¬їЙ·АЦ№ЖдКЬѕІµз·ЕµзµДУ°ПмЈ¬µ«Из№ыІЩЧчІ»µ±ИФїЙДЬ»бЛр»µЎЈК№УГ¶ФѕІµзГфёРµДµзЧУІъЖ·К±Ј¬НЁіЈ»бК№УГ·АѕІµзµжєННуґшЎЈИ»¶шЈ¬ФЪјТАпЈЁХэ№жµДКµСй»·ѕіЦ®НвЈ©№¤ЧчК±Ј¬їЙДЬГ»УРХвР©ОпЖ·ЎЈ±ЬГвѕІµз·ЕµзµДТ»ЦЦµНіЙ±ѕ·Ѕ·ЁКЗФЪЅУґҐICЦ®З°ПИК№ЧФјєЅУµШЎЈФЪІЩЧчCD4007Ц®З°Ј¬К№»эѕЫµДѕІµз·ЕµзЅ«УРЦъУЪИ·±ЈФЪКµСй№эіМЦРІ»»бЛр»µРѕЖ¬ЎЈ ІДБП ► ADALM2000Цч¶ЇС§П°ДЈїй ► ОЮєёКФСй°е ► 1ёцCD4007ЈЁCMOSХуБРЈ© ► 2ёцZVN2110A NMOSѕ§Ме№Ь ► 2ёцZVP2110A PMOSѕ§Ме№Ь ЛµГч ПЦФЪОТГЗЅ«ЅбєПК№УГЦ®З°Б·П°ЦРµД·ґПаЖчБґ№№ЅЁµДЛ«ґ«КдГЕАґ№№ЅЁDРНЛшґжЖчЈ¬ИзНј2ЛщКѕЎЈБЅёцґ«КдГЕРН¬№¤ЧчТФКµПЦDРНЛшґжЖчЎЈФЪЛшґжЖчµДНёГчДЈКЅПВЈ¬µ±CLK=0К±Ј¬µЪТ»ёцґ«КдГЕЈЁЧуЈ©ґтїЄЈ¬Н¬К±µЪ¶юёцґ«КдГЕЈЁУТЈ©№Ш±ХЎЈDНЁ№эµЪТ»ёцґ«КдГЕєНБЅёцґ®БЄµД·ґПаЖчґ«КдЦБКдіц¶Л(Q)ЎЈФЪЛшґжЖчµД±ЈіЦДЈКЅПВЈ¬µ±CLK=1К±Ј¬µЪТ»ёцґ«КдГЕ№Ш±ХЈ¬µ«µЪ¶юёцґ«КдГЕґтїЄЎЈТтґЛЈ¬КдИл¶ЛDЦРµДИОєО±д»Ї¶јІ»»б·ґУіФЪКдіц¶ЛQЙПЎЈІ»№эЈ¬ПЦТСїЄЖфµДµЪ¶юёцґ«КдГЕїЙИ·±ЈНЁ№эФЪБЅёцґ®БЄµД·ґПаЖчЦЬО§РОіЙµД±ХєПХэ·ґАЎ»ШВ·Аґ±ЈБфQЙППИЗ°µДВЯјµзЖЅЎЈФЪОЮєёКФСй°еЙП№№ЅЁНј2ЛщКѕµДDРНЛшґжЖчµзВ·ЎЈЖчјюM1ЦБM6ІЙУГCD4007 CMOSХуБРЈ¬БЅёц·ґПаЖчј¶ЦРµДГїТ»ј¶ЈЁ·ґПаЖчј¶M7єНM8Ј¬ТФј°M9єНM10Ј©К№УГТ»ёцZVN2110A NMOSєНТ»ёцZVP2110A PMOSЎЈµзВ·К№УГADALM2000µД№М¶Ё5 VµзФґ№©µзЎЈ

Нј2.DРНЛшґжЖчЎЈ УІјюЙиЦГ ФЪКµСйЧоіхЈ¬Ѕ«БЅёцAWGКдіцЕдЦГЦ±БчФґЎЈёщѕЭРиТЄЈ¬КѕІЁЖчНЁµАЅ«УГУЪјаїШµзВ·µДКдИлєНКдіцЎЈ№М¶Ё5 VµзФґУГУЪОЄµзВ·№©µзЎЈФЪґЛКµСйЦРЈ¬У¦ЅыУГ№М¶ЁЁC5 VµзФґЎЈ

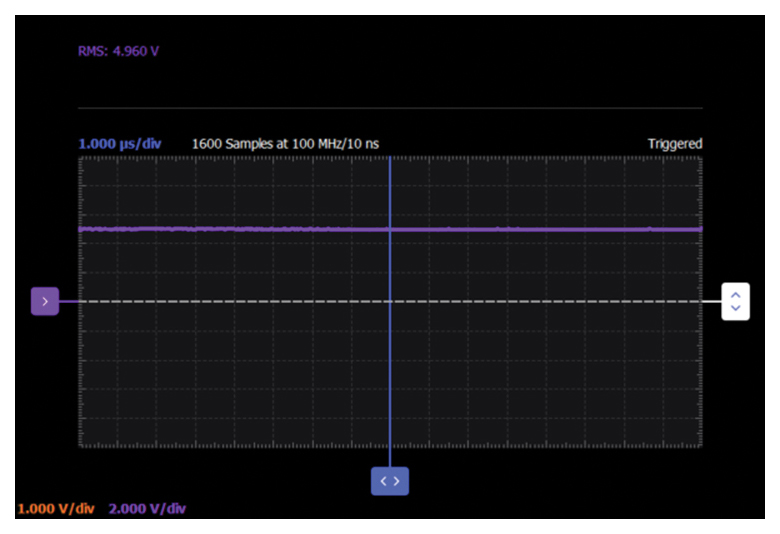

Нј3.DРНЛшґжЖчКФСй°еБ¬ЅУЎЈ іМРтІЅЦи Б¬ЅУТэЅЕ1єН9Ј¬ЛшґжЖчµДDКдИл¶ЛБ¬ЅУµЅAWG1µДКдіц¶ЛЎЈБ¬ЅУТэЅЕ4єН11Ј¬ЛшґжЖчµДQКдіц¶ЛБ¬ЅУµЅКѕІЁЖчНЁµА2ЎЈБ¬ЅУТэЅЕ6Ј¬ЧчОЄБ¬ЅУµЅAWG2µДCLKЎЈИ·±ЈґтїЄ№М¶Ё5 VµзФґЎЈ КЧПИЈ¬ґтїЄAWGїШЦЖЅзГжІўЅ«AWG2ЙиЦГОЄ0 VЦ±БчµзС№Ј¬¶ФCLKК©јУВЯјµНµзЖЅЎЈЅ«AWG1ЙиЦГОЄ5 VЦ±БчµзС№Ј¬¶ФDКдИл¶ЛК©јУВЯјёЯµзЖЅЎЈ №ЫІмКѕІЁЖчНЁµА2ЙПЛшґжЖчµДКдіц¶ЛQЎЈКѕІЁЖчЅзГжЙПУ¦ПФКѕОИ¶ЁµД5 VµзС№ЎЈІ¶»сЖБД»ЅШНјЎЈ

Нј4.ScopyЖБД»ЅШНјЎЈ Ѕ«AWG1ЙиЦГОЄ0 VЦ±БчµзС№Ј¬¶ФDКдИл¶ЛК©јУВЯјµНµзЖЅЎЈ№ЫІмКѕІЁЖчЙПµДКдіцЎЈХвКЗЛшґжЖчµДНёГчДЈКЅЎЈґЛК±У¦ДЬїґµЅКѕІЁЖчНЁµА2ТІКЗ0 VЦ±БчµзС№ЎЈПЦФЪЅ«AWG2ЙиЦГОЄ5 VЦ±БчµзС№Ј¬¶ФCLKК©јУВЯјёЯµзЖЅЎЈН¬К±Ѕ«AWG1ЙиЦГОЄ5 VЦ±БчµзС№Ј¬¶ФDКдИл¶ЛК©јУВЯјёЯµзЖЅЎЈ №ЫІмКѕІЁЖчЅзГжЙПµДQКдіцЎЈУЙУЪDКдИл¶ЛЦ®З°ОЄµНµзЖЅЈ¬ТтґЛѕЎ№ЬЅ«DёьёДОЄВЯјёЯµзЖЅЈ¬ИФ»бПФКѕОИ¶ЁµДµНµзЖЅЎЈІ¶»сЖБД»ЅШНјЎЈХвКЗµзВ·µД±ЈіЦДЈКЅЎЈ

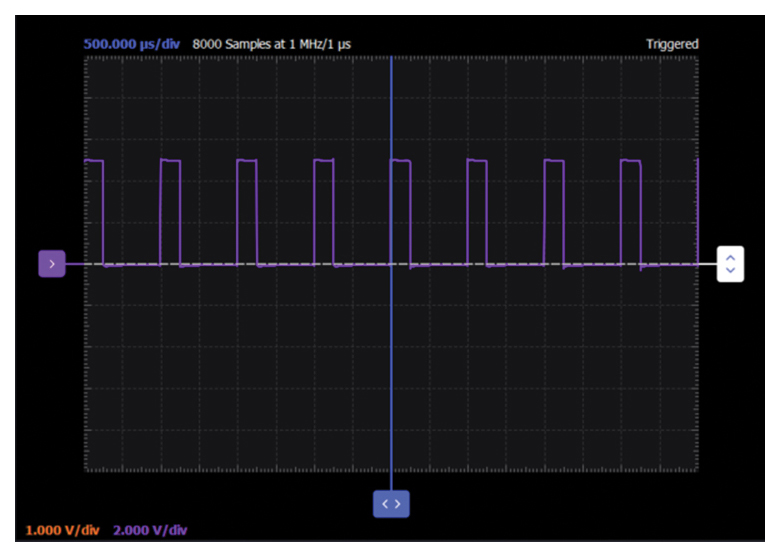

Нј5.ScopyЖБД»ЅШНјЎЈ ПЦФЪЅ«БЅёцAWGНЁµАѕщЕдЦГОЄ·е·еЦµОЄ5VµД·ЅІЁЎЈЅ«AWG1ЙиЦГОЄ1 kHzЖµВКЈ¬Ѕ«AWG2ЙиЦГОЄ2 kHzЖµВК»тAWG1ЖµВКµДБЅ±¶ЎЈЅ«AWG2µДПаО»ЙиЦГОЄ0¶ИЎЈИ·±ЈЅ«AWGЙиЦГОЄН¬ІЅФЛРРЎЈ №ЫІмКѕІЁЖчЅзГжЙПФЪЙПКцCLKєНDКдИлПВПаУ¦µДQКдіцЎЈІ¶»сёчЦЦІЁРОІў±ЈґжЅШНјЈ¬УГУЪ°ьє¬ФЪКµСй±ЁёжЦРЎЈ

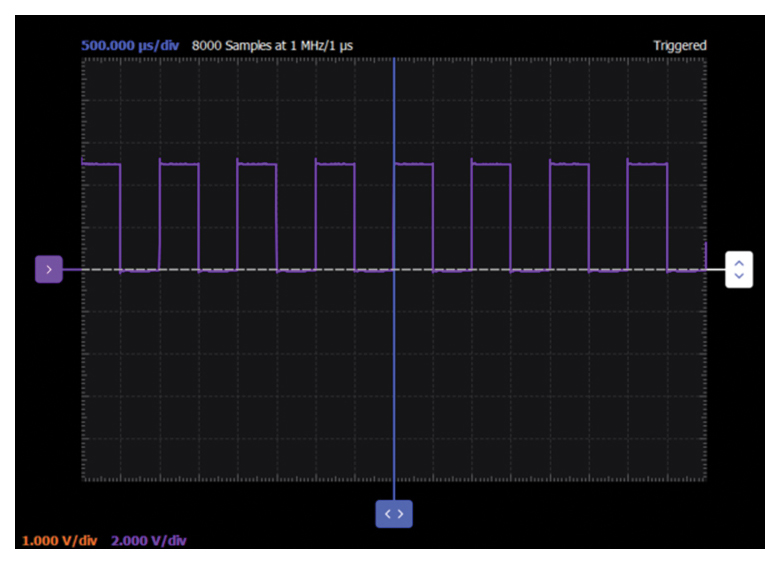

Нј6.ScopyЖБД»ЅШНјЎЈ ПЦФЪЅ«AWG2µДПаО»ЙиЦГОЄ90¶ИЎЈФЩґО№ЫІмКѕІЁЖчЅзГжЙПФЪґЛК±CLKєНDКдИлПВПаУ¦µДQКдіцЎЈУлAWG2ПаО»ОЄ0¶ИК±Па±ИУРєО±д»ЇЈїЛµГчФТтЎЈІ¶»сёчЦЦІЁРОІў±ЈґжЅШНјЈ¬УГУЪ°ьє¬ФЪКµСй±ЁёжЦРЎЈ

Нј7.ScopyЖБД»ЅШНјЎЈ ОКМв µҐёцDРНЛшґжЖчЅ«К№КдИлРЕєЕСУіЩ1/2К±ЦУЦЬЖЪЎЈЛµГчК±ЦУПаО»Па·ґµДБЅёцґ®БЄDРНЛшґжЖчИзєО№№іЙЦчЅЪµгDРНґҐ·ўЖчЈ¬їЙТФК№КдИлРЕєЕСУіЩТ»ёцНкХыµДК±ЦУЦЬЖЪЎЈ Из№ы»№УРCD4007ХуБРїЙУГЈ¬їЙ№№ЅЁЦчЅЪµгDРНґҐ·ўЖчЧчОЄ¶оНвµДБ·П°ЎЈ МжґъРОКЅ Нј2ЛщКѕµДDРНЛшґжЖчК№УГѕЯУРNMOSєНPMOSѕ§Ме№ЬµД»ҐІ№ґ«КдГЕЎЈµҐёцNMOS»тPMOSОЮ·Ёґ«µЭѕЯУРПаН¬Зї¶ИЈЁјґµјНЁµзЧиЈ©µДёЯµНВЯјµзЖЅЎЈµҐёцNMOSЖчјюїЙТФґ«µЭЗїВЯјµзЖЅ0Ј¬µ«»бґ«µЭИхВЯјµзЖЅ1ЎЈПа·ґЈ¬µҐёцPMOSЖчјюїЙТФґ«µЭЗїВЯјµзЖЅ1Ј¬µ«»бґ«µЭИхВЯјµзЖЅ0ЎЈ ФЪРн¶ајЇіЙµзВ·ЙијЖ°ёАэЦРЈ¬ДЪІїРЕєЕЅцФЪДЪІїµзВ·ДЈїйЦ®јдґ«µЭЈ¬ґЛК±µҐёцNMOS»тPMOSѕ§Ме№Ьґ«µЭµД·З¶ФіЖЗэ¶ЇІ»КЗЦчТЄОКМвЎЈФЪХвЦЦЗйїцПВЈ¬ЛшґжЖчЦР№МУРµДХэ·ґАЎїЙДЬ»бУРЛщ°пЦъЎЈїЙТФІЙУГјт»ЇµДDРНЛшґжЖчЈ¬јґЦ»К№УГ6ёцЖчјю¶шІ»КЗНј2ЦРК№УГµД10ёцЖчјюЈ¬ИзНј8ЈЁЛшґжЖчФЪЙПЙэСШЈ©єН9ЈЁЛшґжЖчФЪПВЅµСШЈ©ЛщКѕЎЈ

Нј8.6ѕ§Ме№ЬЙПЙэСШDРНЛшґжЖчЎЈ

Нј9.6ѕ§Ме№ЬПВЅµСШDРНЛшґжЖчЎЈ УІјюЙиЦГ

Нј10.6ѕ§Ме№ЬЙПЙэСШDРНЛшґжЖчКФСй°еБ¬ЅУЎЈ

Нј11.6ѕ§Ме№ЬПВЅµСШDРНЛшґжЖчКФСй°еБ¬ЅУЎЈ ЛµГч ¶ФКФСй°еЅшРРИОєОёьёДЦ®З°Ј¬И·±Ј№Ш±Х№М¶Ё5 VµзФґЎЈФЪОЮєёКФСй°еЙПЈ¬Ѕ«Нј2ЦРµДµзВ·ЦШРВЕдЦГОЄНј3ЦРµДµзВ·ЎЈИ·±ЈґтїЄ№М¶Ё5 VµзФґЎЈЦШёґПаН¬µДІЅЦиЈ¬Ѕ«AWG1Б¬ЅУµЅDКдИл¶ЛЈ¬Ѕ«AWG2Б¬ЅУµЅCLKКдИл¶ЛЎЈСйЦ¤ЛшґжЖчµД№¤ЧчЗйїцЈ¬ЛьЅ«ФЪКдИлК±ЦУµДККµ±±ЯСШЛшґжВЯј0єНВЯј1КдИлЎЈ ЧоєуЈ¬Ѕ«ОЮєёКФСй°еЙПµДµзВ·ЦШРВЕдЦГОЄНј4ЦРµДµзВ·ЎЈИ·±ЈґтїЄ№М¶Ё5 VµзФґЎЈЦШёґПаН¬µДІЅЦиЈ¬Ѕ«AWG1Б¬ЅУµЅDКдИл¶ЛЈ¬Ѕ«AWG2Б¬ЅУµЅCLKКдИл¶ЛЎЈСйЦ¤ЛшґжЖчµД№¤ЧчЗйїцЈ¬ЛьЅ«ФЪКдИлК±ЦУµДККµ±±ЯСШЛшґжВЯј0єНВЯј1КдИлЎЈ МжґъФЄјюСЎФс К№УГЛДёц¶АБўNMOSєНPMOSѕ§Ме№ЬЈЁZVN2110AєНZVP2110AЈ©№№ЅЁµД·ґПаЖч¶ФТІїЙТФУЙµЪ¶юёцCD4007 IC№№іЙЈ¬ТІїЙТФК№УГАэИз 74HC04 »т CD4049 µИБщ·ґПаЖч IC µД CMOS ·ґПаЖчЎЈ ОКМвЈє 1. ДъДЬЛµіцDРНЛшґжЖчµДЦчТЄУГНѕЈЁУ¦УГЈ©ВрЈї ДъїЙТФФЪС§ЧУЧЁЗшВЫМіЙПХТµЅОКМвґр°ёЎЈ №ШУЪЧчХЯ Doug MercerУЪ1977Дк±ПТµУЪВЧЛ№АХАн№¤С§Фє(RPI)Ј¬»сµзЧУ№¤іМС§КїС§О»ЎЈЧФ1977ДкјУИлADI№«ЛѕТФАґЈ¬ЛыЦ±ЅУ»тјдЅУ№±ПЧБЛ30¶аїоКэѕЭЧЄ»»ЖчІъЖ·Ј¬ІўУµУР13ПоЧЁАыЎЈЛыУЪ1995Дк±»ИОГьОЄADIСРѕїФ±ЎЈ2009ДкЈ¬ЛыґУИ«Ц°№¤ЧчЧЄРНЈ¬ІўјМРшТФГыУюСРѕїФ±Йн·ЭµЈИОADI№ЛОКЈ¬ОЄЎ°Цч¶ЇС§П°јЖ»®Ў±Ч«ёеЎЈ2016ДкЈ¬Лы±»ИОГьОЄRPI ECSEПµµДЧ¤РЈ№¤іМК¦ЎЈ Antoniu MiclausПЦОЄADI№«ЛѕµДПµНіУ¦УГ№¤іМК¦Ј¬ґУКВADIЅМС§ПоДї№¤ЧчЈ¬Н¬К±ОЄCircuits from the Lab®ЎўQAЧФ¶Ї»ЇєНБчіМ№ЬАнїЄ·ўЗ¶ИлКЅИнјюЎЈЛыУЪ2017Дк2ФВФЪВЮВнДбСЗїЛВ¬ИХ-ДЙІЁїЁјУГЛADI№«ЛѕЎЈЛыДїЗ°КЗ±ґ±МЛј±«Т®ґуС§Инјю№¤іМЛ¶КїПоДїµДАнС§Л¶КїЙъЈ¬УµУРїЛВ¬ИХ-ДЙІЁїЁїЖјјґуС§µзЧУУлµзРЕ№¤іМС§КїС§О»ЎЈ |

НшУСЖАВЫ