并行SRAM显示缓存实现方案

发布时间:2021-2-22 16:21

发布者:英尚微电子

|

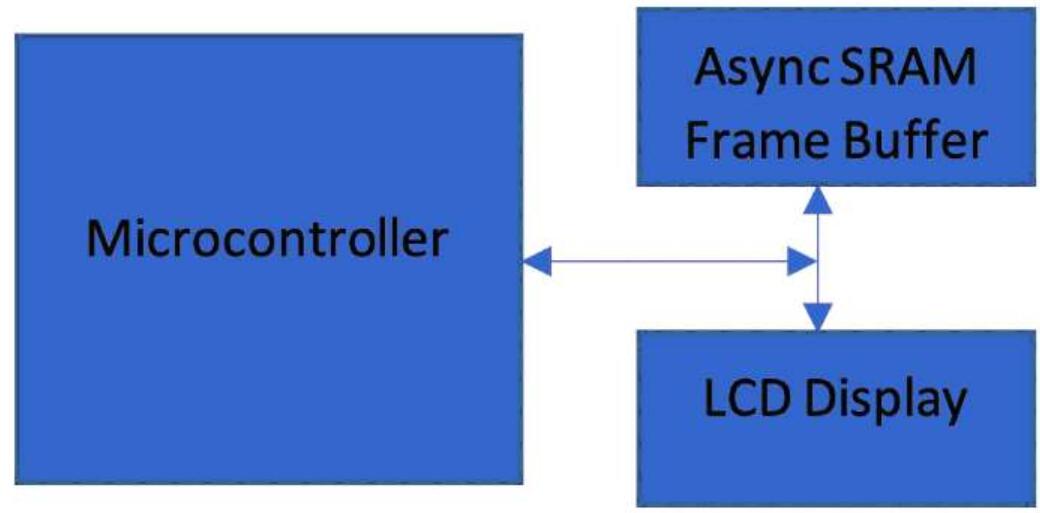

可穿戴设备应用中的显示屏消耗了大部分电池电力。解决方法之一是直接提高电池容量,但是大容量电池会加大尺寸和重量,对可穿戴设备不合适,尤其是在市场不断追求更小型化的新款产品时更是如此。更具挑战性的是电池技术的发展跟不上日益增长的系统需求…… 在可穿戴设备中电池使用寿命对于良好的用户体验至关重要。可穿戴设备应用中的显示屏消耗了大部分电池电力。解决方法之一是直接提高电池容量,但是大容量电池会加大尺寸和重量,对可穿戴设备不合适,尤其是在市场不断追求更小型化的新款产品时更是如此。更具挑战性的是,电池技术的发展跟不上日益增长的系统需求。因此最大限度降低显示屏功耗成为可穿戴设备市场的关键设计因素。 人类的视觉感知非常精确,推动了制造商在可穿戴设备中使用更高分辨率的显示屏。虽然有多种节能方案可供使用,但任何视觉质量下降都会直接影响设备的整体体验。因此在为显示屏考虑节能方案时必须谨慎小心。要想提高显示器分辨率就需要提高存储器带宽,因此为了延长电池使用寿命,降低存储器在待机模式和工作模式下的功耗变得更有实际意义。 显示系统架构 显示屏由像素阵列构成。每个像素的驱动值决定显示的颜色。基于ram的帧缓存保存了显示屏上每个像素的颜色信息。大部分常用的并行显示屏需要周期刷新,从帧缓存读取数据,然后在屏上显示。如果显示屏的分辨率和色彩深度不高,控制器的内部RAM也可以用作帧缓存。 随着显示屏尺寸增大,分辨率和色彩深度提高,内部SRAM将无法提供足够的容量或性能。为了避免画面撕裂,也有必要采用双缓存。在这些系统中通常在外部存储器中实现帧缓存。在刷新周期中,从外部帧缓存读取数据,并连同控制信号输出给显示控制器数据总线。图1所示的是采用外部帧缓存的典型显示框图。 图1:并行SRAM显示缓存实现方案(来源:赛普拉斯) 有多种方法能够降低显示器功耗。 将显示控制器集成到主微控制器内部。市场上常见的显示器模块都有内置控制器。完成上述集成后,有助于充分利用主微控制器的低功耗特性。 使用低功耗存储器作为帧缓存。因为帧缓存始终处于开启状态,所以应采用待机电流低的存储器。 减少对帧缓存的频繁更新。使用容量足够大的存储器并加载多个帧可降低CPU工作电流。如果将最经常访问的帧加载到存储器中,就无需从帧缓存加载和卸载数据。将帧缓存切换到不同的存储器地址就能切换显示器上显示的图像。 我们一直将并行异步SRAM用作外部显示缓存,因为控制器和显示器能够轻松地为他们提供支持。然而这种类型的存储器封装尺寸大、引脚数量多。而串行存储器引脚数量少、封装尺寸小,可以减少所需的控制器引脚数,节省PCB成本。在以Quad SPI模式工作在108MHz下时,串行存储器的性能可与并行异步SRAM存储器媲美。例如赛普拉斯Excelon F-RAM就是一款最大密度高达8Mbit,并采用低引脚数小型GQFN封装的串行非易失性存储器。为了优化功耗可支持四种功耗模式。在典型的Quad SPI模式下以108MHz运行时,工作电流为16mA。当存储器不工作时,待机模式耗电102μA。深度待机模式可进一步将耗电降至0.8μA,休眠模式下只需要0.1μA的最低耗电。 |

网友评论