SOI工业协会组织宣告FDSOI晶体管制造用晶圆产业已整装待发

发布时间:2011-6-29 23:03

发布者:Liming

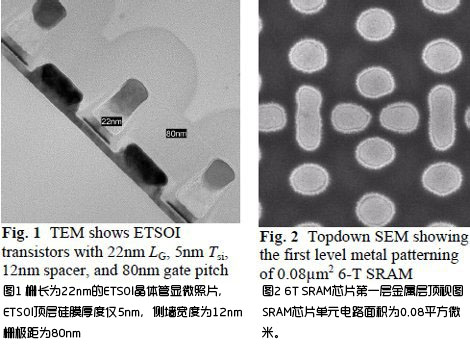

Intel,台积电等巨头企业已经决定先后在22/14nm节点走上Finfet之路,这样一来,另一条路--FDSOI方面的进展状况便显得格外引人注目。最近,在日本东京召开了2011年半导体技术国际会议(Symposium on VLSI Technology),会上,由IBM,意法半导体,GlobalFoundries,瑞萨和东芝等公司组成的半导体技术联盟展示了基于FDSOI技术的22nm制程技术,相比28nm制程体硅结构,这种器件的运行频率提升了25%,并可用于制造单元面积仅0.08平方微米的SRAM和模拟器件.

注:上图的ETSOI和FDSOI以及下面提及的UTB-SOI其实指的都是同样的意思 如上图所示,会上展示的器件采用了面状抬升型漏-源极结构(faceted raised source-drain,简单说就是漏源极不再采用离子注入方法将杂质注入硅衬底中生成,而是在硅衬底上淀积或外延生长一层就地掺杂(in-situ doping)杂质的结构作为漏源极),这种结构可以减小器件的寄生电容。介绍这项技术的研发人员称,器件中的ETSOI沟道区没有掺杂杂质,这样的设计可以避免沟道掺杂浓度的波动,而后者则是器件性能变差的主要根源。 图中左侧的晶体管的SOI硅层厚度仅5nm。右侧的图片则显示了采用这种FDSOI技术制作的SRAM芯片的第一层金属层显微图像。图片来源半导体技术国际会议(Symposium on VLSI Technology) 另外,包括MEMC, SEH以及Soitec等在内的许多SOI晶圆供应商则表示他们已经可以大批量生产UTB-SOI晶圆。为了满足制造全耗尽型晶体管的要求,SOI晶圆上层的硅层厚度必须控制在10nm或以下尺度水平,而且各块晶圆间的硅层厚度变化必须严格控制。因此FDSOI器件制造用UTB-SOI晶圆的成本相对较高,不过据SOI组织声称,由于UTB-SOI晶圆在进行器件隔离处理时,所耗费的成本相对较低,因此两相抵消之后,采用UTB-SOI晶圆制作FDSOI芯片的成本与传统的体硅制程并没有太大的区别。 UTB-SOI晶圆的提供商在会上集体反驳了Intel院士Mark Bohr在今年五月份早些时候对FDSOI“晶圆成本过高”的批评,当时Mark Bohr在Intel 22nm制程Finfet技术新闻发布会上表示,Finfet技术的生产成本仅比Intel以往的平面型晶体管制造技术“多出了几个百分点”,相反“虽然具备超薄SOI层的晶圆也已经被制造出来,但是其成本极高,而且制造的难度很大。”他并表示,根据Intel估计,采用UTB-SOI晶圆会造成器件最终成本提高10%左右。 这些批判之词明显激怒了一众SOI晶圆厂商,这些厂商已经为量产UTB-SOI晶圆投入了大量资金,这些晶圆将可满足半导体厂商生产智能手机及其它移动设备用芯片的要求。 Soitec公司微电子事业部的总经理Christophe Maleville表示,Soitec公司已经在其位于法国Bernin,以及新加坡的两间300mm规格SOI晶圆厂中安装了两套年产量200万片的UTB-SOI晶圆生产产线。“我们已经准备好拓展我们的SOI晶圆产能,以满足消费电子应用对使用FD-SOI技术芯片的大量需求。” 他并表示,Soitec公司生产的UTB-SOI晶圆的硅层厚度一致性水平可控制在埃级尺度,而制造这种晶圆所使用的技术平台则与现有其它大批量SOI晶圆产品的相同。“ Soitec的Smartcut技术原理图 Soitec已经将其用于生产UTB-SOI的Smart Cut工艺技术授权给了另外一家晶圆生产企业信越半导体(Shin-Etsu Handotai (SEH)),后者是全球最大的晶圆供应商,而信越半导体也已经完成了UTB-SOI衬底制造部分的技术研发。信越半导体公司SOI项目主管Noburo Katsuoka称:”我们很高兴能按客户的需求供货。“ MEMC则是IBM SOI芯片的另外一家PD-SOI用SOI晶圆供应商。MEMC公司总裁Shaker Sadasivam表示:”MEMC已经做好了应用FD-SOI适用产品的准备,我们建议客户加快启用FD-SOI技术的步伐。大批量生产是FD-SOI降成本的关键,而MEMC则具备满足业界量产要求的产能。“ 他补充说:”我们已经制定出了一套将FD-SOI用晶圆的产能提升到每月约45000片的计划。“ SOI工业协会组织的执行总裁Horacio Mendez则表示(此君曾经在飞思卡尔公司负责MPU产品的设计),部分产量较高的移动设备用IC芯片厂商可能会在14/15nm节点前启用FD-SOI技术,而FD-SOI则会在14nm节点”全面开花“。 不过,出于降低晶圆采购价格等方面的考虑,移动用芯片厂商仍希望能有更多家厂商具备量产FD-SOI用晶圆的能力。根据Soitec的报价,他们的FD-SOI用晶圆的批量采购价将控制在500美元/片的水平。 Mendez还表示,SOI工业协会组织目前已经在进行一项与包括ARM等公司的设计工程师在内的庞大工程师队伍合作,验证FDSOI技术在22nm节点制程优越性的工作。有关这个项目的更详细进展状况,则会在今年夏天公布于众。 Mendez表示,他非常不赞同Bohr有关FDSOI会增加10%成本的说法,他的理由是在SOI衬底晶圆上的离子注入和器件隔离工序相比体硅衬底的晶圆在加工时处理起来要简单许多,因此SOI工业协会组织认为,SOI芯片产品的最终成本要比体硅低约6%左右。 他还宣称:“在20nm节点,FDSOI晶体管的性能可以达到相当高的水平,以至于有些公司认为不需要考虑采用应变工程技术,这样就可以进一步节约生产成本。” Mendez表示,虽然Intel也许具备应用三栅晶体管(Intel所谓的三栅技术严格说来也算是Finfet的一种,不过为了体现Intel特色,故又冠以三栅之名)技术的半导体制造实力,但是其它半导体制造公司却很难控制采用Finfet技术制造的芯片的良率水平。“Finfet的产品良率是很难控制的,因此在应用这种技术的初期,制造商们将需要频繁改进其工艺,而且产品的良率也无法达到平面型晶体管产品的水平。” 最后,他表示,不论是SOI工业协会,还是Intel,双方在一件事情上的看法是基本一致的,那就是体硅CMOS技术很难超越22nm节点障碍。 |

网友评论