东芝20nm级体硅CMOS工艺获突破

发布时间:2009-12-10 10:03

发布者:李宽

东芝公司今天在美国马里兰州巴尔的摩市举行的IEDM半导体技术会议上宣布,其20nm级CMOS工艺技术获得了重大突破,开启了使用体硅CMOS工艺制造下一代超大规模集成电路设备的大门,成为业界首个能够投入实际生产的20nm级CMOS工艺。东芝表示,他们通过对晶体管沟道的掺杂材料进行改善,实现了这次突破。

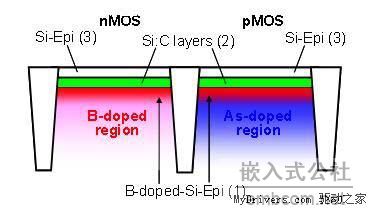

在传统工艺中,由于电子活动性降低,通常认为体硅(Bulk)CMOS在20nm级制程下已经很难实现。但东芝在沟道构造中使用了三层材料,解决了这一问题,成功实现了20nm级的体硅CMOS。这三层材料中,最顶层为外延硅,中间硅层掺杂碳,底层则掺杂硼(nMOS)或砷(pMOS)。 东芝宣称,这种新工艺在性能上比传统沟道结构提升了15%到18%,并且通过简单的工艺改进即可实现,不需要使用成本更高的SOI工艺或3D栅极结构。 来源:驱动之家 |

网友评论