ДЙГЧИнјю»щУЪDSPөДКэЧЦЖөВКјЖЙијЖ

·ўІјКұјдЈә2020-1-13 17:18

·ўІјХЯЈәnamisoft

|

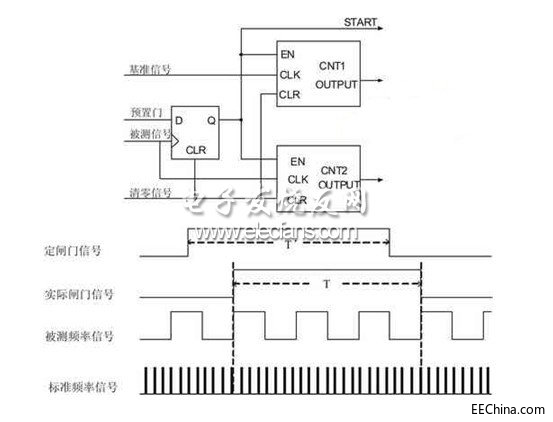

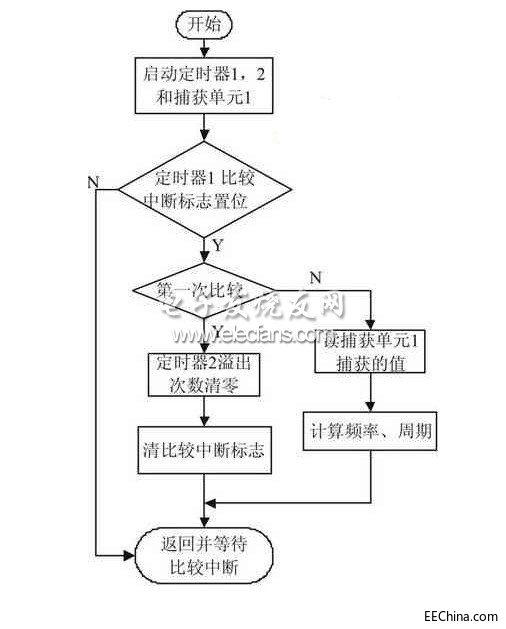

ЛжЧЕОўөзЧУјјКхәНјЖЛг»ъјјКхөД·ЙЛЩ·ўХ№, ёчЦЦөзЧУІвБҝТЗЖчФЪФӯАнЎў№ҰДЬЎўҫ«¶Иј°ЧФ¶Ҝ»ҜЛ®ЖҪөИ·ҪГж¶ј·ўЙъБЛҫЮҙуөДұд»Ҝ, МШұрКЗDSPјјКхө®ЙъТФәуЈ¬өзЧУІвБҝјјКхёьКЗВхҪшБЛТ»ёцИ«РВөДКұҙъЎЈҪьДкАҙЈ¬DSPЦрҪҘіЙОӘёчЦЦөзЧУЖчјюөД»щҙЎЖчјюЈ¬ЦрҪҘіЙОӘ21КАјНЧоҫЯ·ўХ№ЗұБҰөДіҜСфРРТөЈ¬ЙхЦБұ»УюОӘРЕПў»ҜКэЧЦ»ҜКұҙъёпГьЖмКЦЎЈФЪөзЧУІвБҝјјКхЦРЈ¬ЖөВККЗЧо»щұҫөДІОКэЦ®Т»Ј¬ЛьУлРн¶аөзІОБҝәН·ЗөзБҝөДІвБҝ¶јУРЧЕК®·ЦГЬЗРөД№ШПөЎЈАэИзЈ¬Рн¶аҙ«ёРЖчҫНКЗҪ«Т»Р©·ЗөзБҝЧӘ»»іЙЖөВКАҙҪшРРІвБҝөДЈ¬ТтҙЛЖөВКөДІвБҝҫНПФөГёьОӘЦШТӘЎЈКэЧЦЖөВКјЖКЗУГКэЧЦАҙПФКҫұ»ІвРЕәЕЖөВКөДТЗЖчЈ¬ұ»ІвРЕәЕҝЙТФКЗХэПТІЁЎў·ҪІЁ»тЖдЛьЦЬЖЪРФұд»ҜөДРЕәЕЎЈ КэЧЦЖөВКјЖ№г·әІЙУГБЛёЯЛЩјҜіЙөзВ·әНҙу№жДЈјҜіЙөзВ·Ј¬К№өГТЗЖчөДМе»эёьРЎЎўәДөзёьЙЩЎўҫ«¶ИәНҝЙҝҝРФёьёЯЎЈ¶шҙ«НіөДЖөВКјЖІвБҝОуІоҪПҙуЈ¬·¶О§ТІҪПХӯЈ¬ТтҙЛЦрҪҘұ»РВРНөДКэЧЦЖөВКјЖЛщҙъМжЎЈ»щУЪDSPөДөИҫ«¶ИЖөВКјЖТФЖдІвБҝЧјИ·Ўўҫ«¶ИёЯЎў·ҪұгЎўјЫёсұгТЛөИУЕКЖҪ«өГөҪ№г·әөДУҰУГЎЈ ОТГЗЙијЖөДјтТЧКэЧЦЖөВКјЖФЪОҙІЙУГИОәОГЕҝШЖчјюҝШЦЖөДЗйҝцПВЈ¬ФЪәЬҝнөД·¶О§ДЪКөПЦБЛөИҫ«¶ИЖөВКІвБҝЈ¬0.5Hz~10MHzөД·¶О§ДЪІвБҝ·ҪІЁөДЧоҙуПа¶ФОуІоРЎУЪ2e-6Ј¬ІвБҝХэПТІЁөДЧоҙуПа¶ФОуІоРЎУЪ3.5e-5Ј»Ҫб№ыНЁ№эRS232НЁС¶ПФКҫФЪјЖЛг»ъЙПЈ¬ҝЙТФәЬ·ҪұгөШјаІвКэҫЭЎЈ ҙ«НіөДөИҫ«¶ИІвЖө·ЁК№УГГЕҝШЖчјюІъЙъГЕҝШРЕәЕЈ¬ҙУ¶шКөПЦКөјКГЕХўРЕәЕУлұ»ІвРЕәЕН¬ІҪЈ¬Пыіэ¶Фұ»ІвРЕәЕјЖКэІъЙъөДТ»ёцВціеөДОуІоЈ¬ЖдФӯАнНјИзНј1ЛщКҫЎЈ

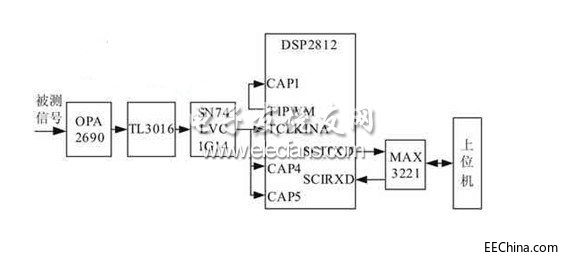

УЙУІјюҝШЦЖјЖКэөДГЕХўКұјдЈ¬өұФӨЦГГЗРЕәЕ(јҙ¶ЁХўГЕРЕәЕ)ОӘёЯөзЖҪКұЈ¬»щЧјРЕәЕјЖКэЖчCNT1әНұ»ІвРЕәЕјЖКэЖчCNT2ІўІ»Жф¶ҜЈ¬¶шКЗөИұ»ІвРЕәЕөДЙПЙэСШАҙөҪКұІЕН¬КұҝӘКјјЖКэЈ»өұФӨЦГГЗРЕәЕОӘөНөзЖҪКұЈ¬БҪёцјЖКэЖчІўІ»ВнЙП№ШұХЈ¬Н¬СщТӘөИөҪұ»ІвРЕәЕЙПЙэСШАҙөҪәуФЩ№ШұХЈ»УЪКЗЈ¬КөјКХўГЕКұјдҫНКЗұ»ІвРЕәЕЦЬЖЪөДХыКэұ¶Ј¬ҙУ¶шКөПЦБЛХўГЕУлұ»ІвРЕәЕөДН¬ІҪЎЈө«КЗЈ¬КөјКөДГЕХўКұјдІўІ»№М¶ЁЈ¬Улұ»ІвРЕәЕөДЖөВКУР№ШЎЈҙЛНвЈ¬ОЮВЫКЗІЙУГјЖКэЖч»№КЗөҘЖ¬»ъЈ¬ФЪКөПЦөИҫ«¶ИІвБҝКұЧЬКЗАлІ»ҝӘГЕҝШЖчјюЎЈ ЎЎЎЎұҫЙијЖ»щУЪDSP·бё»өДИнјюЧКФҙЈ¬ҫӯ№эЕР¶ПәНҙҰАнЈ¬НкіЙБЛ¶Фұ»ІвРЕәЕЖөВКөДөИҫ«¶ИІвБҝЎЈУІјюЙПОЮРиИОәОГЕҝШЖчјюЈ¬јт»ҜБЛөзВ·ЎЈПөНіҝтНјИзНј2ЛщКҫЈ¬РЕәЕҙҰАнІҝ·ЦТФTMS320F2812 DSPРҫЖ¬ЧчОӘҝШЦЖәНІвБҝөДәЛРДЈ»РЕәЕөчАнІҝ·ЦЦчТӘКЗНкіЙ¶ФРЕәЕөД·ЕҙуЎўХыРОәНПЮ·щЈ»ұкЧјЖөВКРЕәЕУЙ30MHzУРФҙҫ§ХсІъЙъЈ¬ЧчОӘёЯЖөұкЧјМоідВціеЈ»НЁ№эDSPөДSCIДЈҝйУлЙПО»»ъКөПЦНЁРЕЈ¬Ҫб№ыПФКҫФЪЙПО»»ъЙПЎЈ

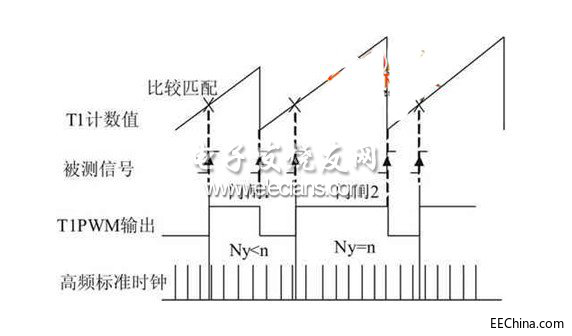

ЖөВК/ЦЬЖЪІвБҝ ЎЎЎЎФЪ¶Фұ»ІвРЕәЕЖөВКәНЦЬЖЪөДІвБҝЦРЈ¬өИҫ«¶ИІвБҝКЗ»щУЪDSPұИҪПЖҘЕдКұT1PWMТэҪЕКдіцөзЖҪөДМшұдЧчОӘГЕХўРЕәЕөДҝӘЖфәН№ШұХЈ¬УЙУЪұИҪПЖҘЕд·ўЙъФЪұ»ІвРЕәЕөДЙПЙэСШЈ¬ҙУ¶шКөПЦБЛГЕХўКұјдУлұ»ІвРЕәЕөДН¬ІҪЎЈФӯАнНјИзНј3ЛщКҫЎЈ

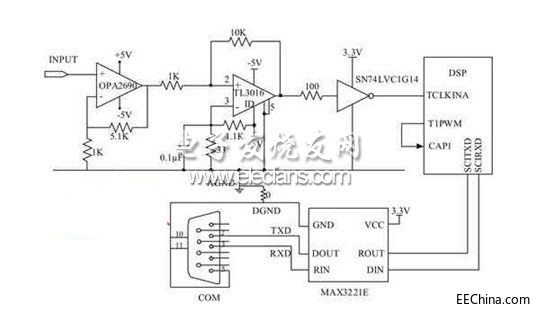

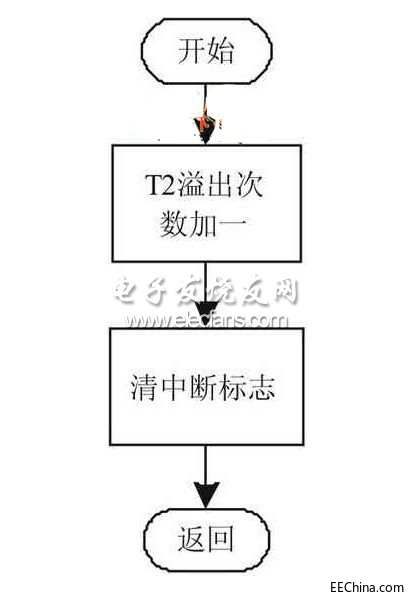

НЁУГ¶ЁКұЖчT1КұЦУКдИлСЎФсНвІҝ¶ЁКұЖчКұЦУЈ¬ҙЛҙҰУГөчАнәуөДұ»ІвРЕәЕЧчОӘ¶ЁКұЖчT1өДКұЦУКдИлЈ¬¶ЁКұЖчT2КұЦУКдИлСЎФсДЪІҝCPUКұЦУЈ¬УГАҙІъЙъёЯЖөұкЧјМоідВціеЎЈF2812Ж¬ЙПEVAЦРНЁУГ¶ЁКұЖчT1ФЪ·ўЙъұИҪПЖҘЕдКВјюКұЈ¬ЖдұИҪПКдіцТэҪЕT1CMPКдіцРЕәЕ»бЧФ¶ҜёДұдөзЖҪЧҙМ¬Ј¬ІъЙъPWMІЁЎЈІ¶»сөҘФӘCAP1ЙиЦГОӘЙПЙэСШІ¶»сЈ¬T1PWMКдіцөДPWMІЁЙПЙэСШұ»CAP1І¶»сөҪЈ¬¶БИЎҙЛКұ¶ЁКұЖчT2өДјЖКэЦөЈ¬Н¬АнФЪПВТ»ҙОұИҪПЖҘЕдКұФЩҙО¶БИЎ¶ЁКұЖчT2өДјЖКэЦөЎЈНЁ№эБҪҙОT2CNTЦөөДПајхЈ¬јҙҝЙ»сөГёГГЕХўКұјдДЪұкЧјМоідВціеөДёцКэЈ¬И»әуЗуіцұ»ІвРЕәЕЖөВКЎЈ ЎЎЎЎ»щУЪDSPұИҪПЖҘЕдКұT1PWMТэҪЕКдіцөзЖҪөДМшұдЧчОӘГЕХўРЕәЕөДҝӘЖфәН№ШұХЈ¬УЙУЪұИҪПЖҘЕд·ўЙъФЪұ»ІвРЕәЕөДЙПЙэСШЈ¬ҙУ¶шКөПЦБЛГЕХўКұјдУлұ»ІвРЕәЕөДН¬ІҪЎЈБҪёцПаБЪөДұИҪПЖҘЕдІъЙъөДPWMІЁөДЙПЙэСШ·ЦұрЧчОӘГЕХўРЕәЕөДҝӘЖфәН№ШұХРЕәЕЈ¬ЖдЦРұ»ІвРЕәЕөДёцКэОӘХыКэЈ¬ІўЗТКЗУЙОТГЗЧФјәИОТвЙи¶ЁөДЎЈ¶ЁКұЖчT2КұЦУКдИлСЎФсДЪІҝCPUКұЦУЈ¬УГАҙІъЙъұкЧјМоідВціеЎЈЙи¶ЁІ¶»сөҘФӘCAP1ОӘЙПЙэСШІ¶»сЈ¬өұЖдІ¶»сөҪЙПЙэСШКұ¶БИЎ¶СХ»CAPFIFOДЪөДЦөЈ¬ФЪПВТ»ҙОІ¶»сөҪКұФЩ¶Б¶СХ»ДЪөДЦөЈ¬јЖЛгіцұкЧјМоідВціеөДёцКэNyЈ¬ұЈЦӨNyөДёцКэІ»РЎУЪТ»¶ЁөДЦөЈ¬јҙҝЙұЈЦӨГЕХўКұјдҙуУЪТ»¶ЁөДЦөЎЈјЩЙиПЦФЪПЈНыТ»ёцГЕХўКұјдДЪёЯЖөМоідВціеөДЧЬКэІ»РЎУЪnЈ¬өұNy>nКұЈ¬ҫНФцҙу¶ЁКұЖчT1өД¶ЁКұЦЬЖЪЈ¬јҙФцҙу¶ЁКұЖчT1ЦЬЖЪјДҙжЖчTIPRөДЦөЎЈҙжФЪ№«КҪT1PR+1=n/NyЈ¬УЙУЪn/NyІ»Т»¶ЁОӘХыКэЈ¬јЩa ЎЎЎЎЦЬЖЪІвБҝУлЖөВКІвБҝөД»щұҫФӯАнНкИ«ПаН¬Ј¬ІвіцРЕәЕЖөВКЈ¬ёщҫЭ№«T=1/fјҙҝЙөГіцұ»ІвРЕәЕөДЦЬЖЪЎЈ ЎЎЎЎОуІо·ЦОц ЎЎЎЎ¶ЁКұЖчT1јЖКэөДЖфНЈКұјд¶јКЗУЙёГРЕәЕөДЙПЙэСШҙҘ·ўөДЈ¬ФЪТ»ҙОІвБҝКұјдДЪ¶Фұ»ІвРЕәЕөДјЖКэОЮОуІоЈ»ФЪҙЛКұјдДЪұкЧјЖөВКВціеөДјЖКэёцКэNyЈ¬Чо¶аПаІоТ»ёцВціеЈ¬№КАнВЫОуІоОӘЈә ЎЎЎЎ|d|ЎЬ1/Ny ЎЎЎЎПФИ»Ј¬ІвБҝҫ«¶ИҪцҪцУлNyУР№ШЈ¬Ц»ТӘNyЦөЧг№»ҙуЈ¬ҫНДЬұЈЦӨҫ«¶ИЎЈ ЎЎЎЎУІјюЙијЖ ЎЎЎЎИзНј4ЛщКҫЈ¬Ҫ«ұ»ІвРЕәЕҫӯ№эёЯЛЩФЛ·ЕOPA2690ҪшРР·ЕҙуЈ¬ФЪҫӯ№эёЯЛЩұИҪПЖчTL3016ҪшРРХыРО[3]Ј¬УЙУЪұИҪПЖчФЪ¶ФөНЖөХэПТІЁРЕәЕҪшРРХыРОКұЈ¬КдіцІЁРОөДұЯСШУРұИҪПСПЦШөД¶¶¶ҜЈ¬У°ПмІвБҝЎЈҪвҫц°м·ЁКЗ¶ФұИҪПЖчјУИлХэ·ҙАЎЈ¬јУЛЩРЕәЕұЯСШЈ¬Н¬КұРОіЙЦН»·Ј¬ҝЙУРР§Пыіэ¶¶¶ҜЎЈХыРОәуөДРЕәЕҫӯ№эёЯЛЩК©ГЬМШҙҘ·ўSN74LVC1G14ҪшРРПЮ·щәНҪшТ»ІҪХыРОЎЈІвБҝІҝ·ЦЦчТӘК№УГDSP2812РҫЖ¬ЙП¶ЁКұЖчT1өДКұЦУКдИлТэҪЕTCLKINAЎў¶ЁКұЖчT1өДұИҪПКдіцТэҪЕT1PWMәНІ¶»сөҘФӘCAP1өДКдИлТэҪЕCAP1Ј¬јҙҝЙНкіЙЖөВКІвБҝЎЈНЁС¶Іҝ·ЦСЎФсMAX3221ЧчОӘRS-232өзЖҪЧӘ»»ЖчјюЈ¬НЁ№э9РҫұкЧјRS-232ҝЪУлЙПО»»ъҪшРРҙ®РРНЁРЕЎЈЦчТӘК№УГБЛDSPөДҙ®РРНЁРЕ·ўЛНТэҪЕSCIRXDәНҙ®РРНЁРЕҪУКХТэҪЕSCITXDЎЈ

ИнјюЙијЖІҝ·ЦЦчТӘ°ьАЁТФПВЛДІҝ·ЦЈә ЎЎЎЎЎӨіхКј»ҜЈә¶ФұдБҝІОКэЎўПөНіКұЦУЎўPIEЎўEVЎўFlashЎўGPIOөИҪшРРЕдЦГЎЈ ЎЎЎЎЎӨЦР¶ПДЈҝйЈәSCIЦР¶ПәН¶ЁКұЖчT2ЎўT3ЙПТзЦР¶ПЎЈ ЎЎЎЎЎӨКэҫЭҙҰАнДЈҝйЈә·Ц¶О+ИЎЛгКхЖҪҫщЦөЎЈ ЎЎЎЎЎӨКдіцІЩЧчДЈҝйЈәКэҫЭҫӯRS-232ҙ«ёшЙПО»»ъЎЈ ЎЎЎЎНј5ОӘІвЖөВКЎўЦЬЖЪИнјюБчіМНјЈ¬Нј6ОӘ¶ЁКұЖч2өДТзіцЦР¶ПБчіМНјЎЈ

ФЪёГІҝ·ЦіхКј»ҜКұЈ¬ТӘҪшРРТФПВЕдЦГЈәНЁУГ¶ЁКұЖчT1КұЦУКдИлОӘНвІҝ¶ЁКұЖчКұЦУЈ¬НЁУГ¶ЁКұЖчT2КұЦУКдИлОӘДЪІҝКұЦУКдИлЈ¬УГАҙ¶ФұкЧјВціеҪшРРјЖКэЈ¬ёГұкЧјВціеУЙНвІҝ30MHzөДУРФҙҫ§ХсМṩЈ»І¶»сөҘФӘ1ЙиЦГОӘЙПЙэСШІ¶»сЈ¬УГАҙІ¶»сT1PWMТэҪЕКдіцPWMІЁөДЙПЙэСШЈ¬ФЪГҝҙОұИҪПЖҘЕдКұ¶БИЎ¶ЁКұЖчT2өДјЖКэЦөT2CNTЈ¬ёГЦөұЈҙжФЪCAP1FIFOДЪЎЈіхКј»ҜКұТӘҪ«І¶»сөҘФӘ1өДЧҙМ¬јДҙжЖчЦРөДFIFO¶СХ»ЧҙМ¬ЙиЦГіЙҝХ¶СХ»Ј»Ҫ«¶ЁКұЖчT1өД¶ЁКұЦЬЖЪЙиЦГОӘ4ёцұ»ІвРЕәЕөДЦЬЖЪіӨ¶ИЈ¬НЁ№эІвөГөД¶ЁКұЖчT1өДТ»ёц¶ЁКұЦЬЖЪДЪөДұкЧјВціеөДёцКэЈ¬јЖЛгіцұ»ІвРЕәЕЖөВКЈ¬И»әу¶Фұ»ІвРЕәЕҪшРР·Ц¶ОЈ¬·ЦұрОӘөНЖө¶О(РЎУЪ46.875Hz)Ј¬ЦРЖө¶О(ҙуУЪ46.875HzЈ¬РЎУЪ2343.75KHz)Ј¬ТФј°ёЯЖө¶О(ҙуУЪ2343.75 KHz)Ј¬ЖдЦР·Ц¶ОөДТАҫЭКЗ¶ЁКұЖчөДјЖКэұҘәНЦөОӘ65536әНјЖКэёцКэУҰҙуУЪөИУЪ1ЎЈИфРЕәЕЖөВКОӘЦРёЯЖө¶ОФтЦШРВЕдЦГ¶ЁКұЖчT1Ј¬¶ЁКұЖчT2өДјДҙжЖчЈ¬АҙёДұд¶ЁКұЦЬЖЪТФј°ГҝёцГЕХўКұјдДЪөДёЯЖөМоідВціеөДёцКэЎЈФЪ¶ЁКұЖчT1өДПВТ»ёц¶ЁКұЦЬЖЪДЪјЖЛгіцЖөВКәНЦЬЖЪЎЈБнНвЈ¬¶ЁКұЖчT2өДТзіцҙОКэТӘФЪөЪТ»ҙО·ўЙъұИҪПЖҘЕдКұЗеБгЈ¬¶шКЗ·сКЗөЪТ»ҙО·ўЙъұИҪПЖҘЕдФтНЁ№эЙиЦГТ»ёцұкЦҫАҙЕР¶ПЎЈөұТзіцҙОКэЗеБгәуІЕҝӘКјјЗТзіцҙОКэЈ¬ЦұөҪөЪ¶юҙО·ўЙъұИҪПЖҘЕдЎЈ ёГ·Ҫ·ЁөДІвБҝОуІоЦчТӘАҙЧФУІјюІҝ·ЦЈ¬ХыРОөзВ·өДУЕБУЦұҪУ№ШПөөҪІвБҝҫ«¶ИөДёЯөНЎЈЛщТФОТГЗПВТ»ІҪөД№ӨЧчҫНКЗёДҪшХыРОөзВ·өДХыРОР§№ыәНҝ№ёЙИЕРФДЬЈ¬ҫЎЧоҙуҝЙДЬјхРЎРЕәЕХыРОҙшАҙөДОуІоЎЈ УЙУЪDSP¶ЁКұЖчФЪјЖКэКұҙжФЪјЖКэұҘәНөДЗйҝцЈ¬ТтҙЛФЪКөПЦёГөИҫ«¶ИІвБҝКұҙжФЪЙППЮЈ¬јҙөұұ»ІвРЕәЕЖөВКёЯУЪёЯЖөМоідВціеөДЖөВККұЈ¬ёГ·Ҫ·ЁҫНІ»ДЬКөПЦөИҫ«¶ИБЛЎЈҝЙТФФЪёГ·Ҫ°ёөД»щҙЎЙПҪшРРТФПВҙҰАнЈәСЎФс¶ЁКұЖчT1¶ЁКұЦЬЖЪДЪұ»ІвРЕәЕөДёцКэ№М¶ЁЈ¬ҝЙЙиЦГT1PRОӘ65529Ј¬Н¬КұҪ«¶ЁКұЖчT2өДКұЦУРЮёДОӘ75MHzЈ¬ХвСщҫНДЬұЈЦӨГҝёцГЕХўКұјдДЪёЯЖөМоідВціеөДёцКэЈ¬ҙУ¶шФЪ¶ФёЯЖөРЕәЕКөПЦЖөВКәНЦЬЖЪІвБҝКұұЈЦӨБЛҫ«¶ИЎЈ ө«СЎФс¶ЁКұЖчT1КұЦУКдИлОӘНвІҝКұЦУКұ¶Фұ»ІвРЕәЕөДКдИл·¶О§ҙжФЪПЮЦЖЈ¬Из№ыТӘҪшТ»ІҪМбёЯІвБҝөДРЕәЕөД·¶О§Ј¬К№өГ·¶О§ҙпөҪЙП°ЩХЧ»тЙПGәХЧИЈ¬ҝЙТФҝјВЗПаО»ІвБҝөД·Ҫ·ЁЈ¬Ҫ«ұ»ІвРЕәЕЙиОӘ360¶ИЈ¬ёщҫЭұ»ІвРЕәЕУлұкЧјРЕәЕЦ®јдөДX¶ИПаО»ІоЈ¬јЖЛгұ»ІвРЕәЕЖөВКЎЈ |

НшУСЖАВЫ