ЭцзЊZynqСЌди31ЁЊЁЊ[ex53] ЛљгкZynq PSЕФEMIOПижЦ

ЗЂВМЪБМфЃК2019-10-12 17:44

ЗЂВМепЃКrousong1989

|

ЭцзЊZynqСЌди31ЁЊЁЊ[ex53] ЛљгкZynq PSЕФEMIOПижЦ ИќЖрзЪСЯЙВЯэ ЬкбЖЮЂдЦСДНгЃКhttps://share.weiyun.com/5s6bA0s АйЖШЭјХЬСДНгЃКhttps://pan.baidu.com/s/1XTQtP5LZAedkCwQtllAEyw ЬсШЁТыЃКld9c

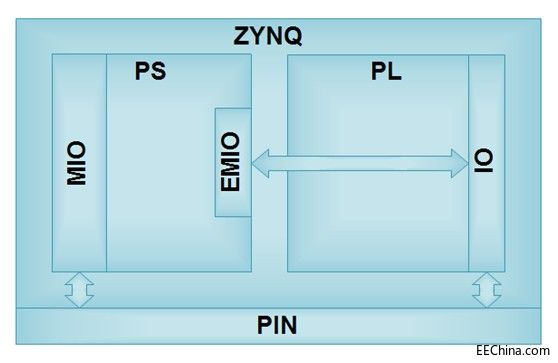

ВЮПМЮФЕЕЁЖЭцзЊZynq-ЛљДЁЦЊЃКZynq PSЕФGPIOЭтЩш.pdfЁЗЁЃ ЙигкEMIOКЭMIOЃЌетРяЖрЊрТСНОфЁЃМђЕЅЕФРэНтЃЌMIOЪЧPSЯЕЭГдЩњЕФЃЌКЭPLУЛЩЖЙиЯЕЃЛЕЋЪЧEMIOЪЧPSНшPLЕФв§НХгУЃЌЫљвдЫќУЧОЭгаЧЇЫПЭђТЦЕФЙиЯЕЃЌPLЕФЙЄГЬРяУцЪЦБивЊзіЕуЪВУДЁЃMIOдкPSЯЕЭГРяУцЗжХфКУЖдгІЕФаХКХЙІФмКѓЃЌдкPLЕФДњТыРяУцОЭВЛашвЊаДШЮКЮЕФТпМЃЌЩѕжСв§НХЗжХфЖМВЛашвЊЃЈЩњГЩЕФPSЯЕЭГЛсздЖЏЗжХфЃЉЁЃЕЋЪЧEMIOОЭвЊдкPSЕФЯЕЭГжав§ГіЃЌШЛКѓдкPLЖЅВудДТыжаЩъУїЖЫПкРраЭЃЌзів§НХЗжХфЃЈвђЮЊEMIOгУЕФОЭЪЧPLЕФв§НХЃЉЁЃ ЙигкMIOКЭEMIOЕФЙиЯЕЃЌИќаЮЯѓжБНгЕФПЩвдЪОвтШчЭМЫљЪОЁЃMIOКЭEMIOЖМЪЧPSЕФвЛВПЗжЃЌЕЋЪЧMIOПЩвджБНгСЌНгЕНZynqаОЦЌЕФв§НХЩЯЃЌКЭPLЮоЙиЃЛЖјEMIOашвЊЭЈЙ§PLЕФIOВХФмСЌНгЕНZynqаОЦЌЕФв§НХЩЯЁЃEMIOЕФДцдкЃЌЦфЪЕЪЧИјгУЛЇИќДѓЕФPSЕФGPIOРЉеЙЕФСщЛюадЃЌетвВЪЧFPGA+ARMЖРгаЕФМмЙЙЁЃвђДЫЃЌEMIOдѕУДгУЃЌКмгаБивЊКУКУЭцЭцЁЃ

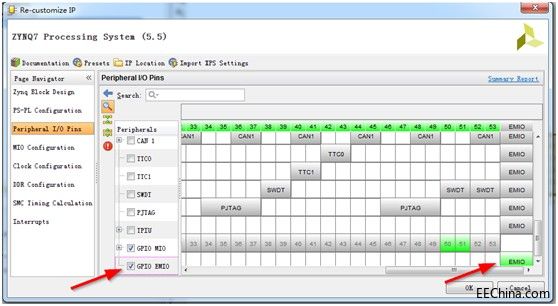

ДђПЊZYNQ7 Processing SystemЕФХфжУвГУцPeripheral I/O PinsЃЌЙДбЁGPIO EMIOбЁЯюЃЌВщПДPeriperalsзюгвВрЕФEMIOСаЃЌЖдгІЕФEMIOЯдЪОАДХЅБфТЬСЫЃЌдђБэЪОИУEMIOЙІФмПЊЦєЃЌEMIOв§НХНЋЛсв§ГіЕНPSЯЕЭГЁЃ

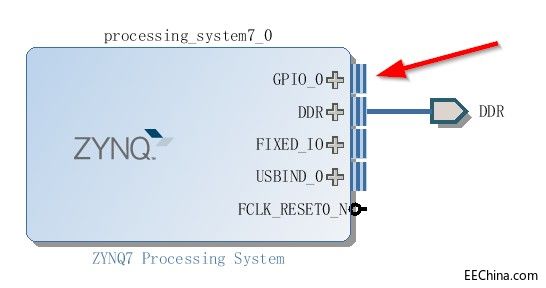

ЭъГЩХфжУКѓЃЌЛиЕНZYNQ7ЯЕЭГПђЭМжаЃЌПЩвдПДЕНЖрСЫвЛИіУћЮЊGPIO_0ЕФНгПкЁЃ

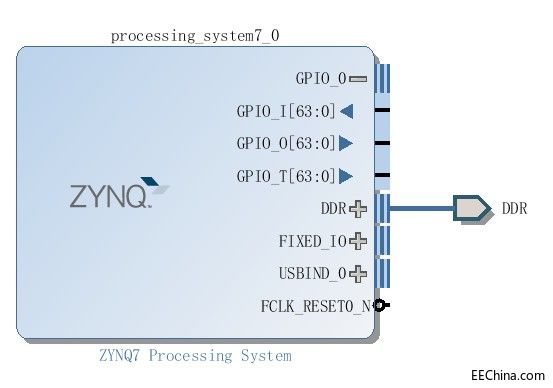

еЙПЊGPIO_0НгПкЃЌЪЕМЪЩЯга3зщ64bitЕФаХКХЃЌЗжБ№ДњБэinputЃЈGPIO_IЃЉЁЂoutputЃЈGPIO_OЃЉКЭinoutЃЈGPIO_TЃЉЁЃдкЪЕМЪЪЙгУжаЃЌИљОнЮвУЧЕФв§НХЗНЯђЃЌСЌНгЖдгІЮЛЕФв§НХМДПЩЁЃР§ШчЃЌGPIO_I[0]ЁЂGPIO_O[0]КЭGPIO_T[0]ЪЕМЪЩЯЖдгІЕФЖМЪЧвЛИіEMIOЃЌШчЙћЮвжЛгУетИіEMIOСЌНгвЛИізїЮЊoutputЕФLEDЃЌФЧУДЮвдкPLЩЯжЛвЊв§ГіGPIO_O[0]ВЂзїв§НХЗжХфОЭПЩвдСЫЁЃ

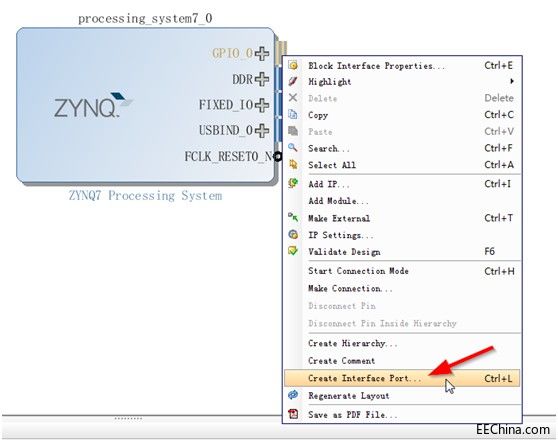

бЁжаGPIO_0ЃЌгвМќЕЅЛїЃЌЕЏГіВЫЕЅжаЕуЛїCreate Interface Port...ЃЌв§ГівЛИіportгУгкPLЙЄГЬЕФЖЅВуСЌНгЁЃ

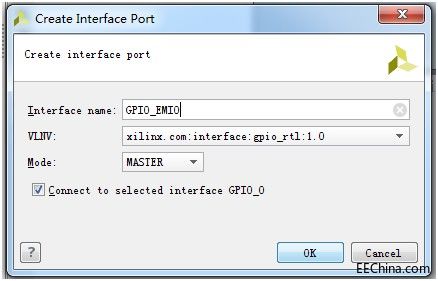

ПЩвдУќУћЮЊGPIO_EMIOЁЃ

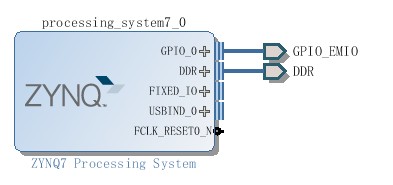

ЭъГЩGPIO_EMIOв§ГіКѓШчЭМЫљЪОЁЃ

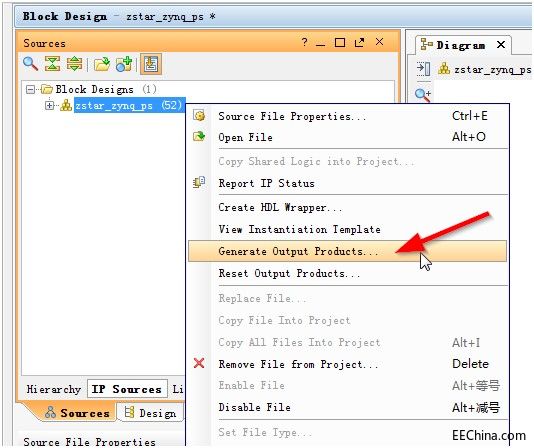

дкSources --> IP SourcesжабЁдёBlock Designs -->zstar_zynq_psЃЌЕЅЛїгвМќЃЌЕЏГіВЫЕЅжабЁжаGenerate Output Products...ЁЃ

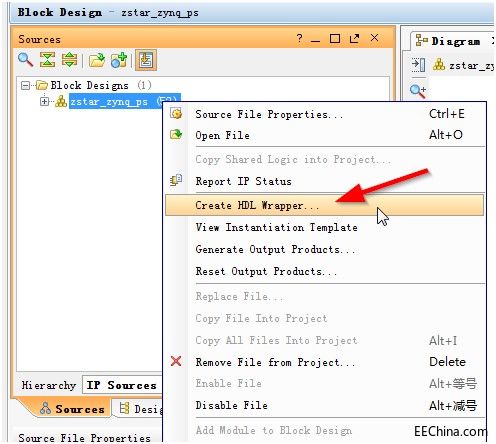

НгзХЮвУЧПЩвддйДЮВйзїЃЌЕЅЛїгвМќВЫЕЅЕФCreate HDL Wrapper...бЁЯюЁЃ

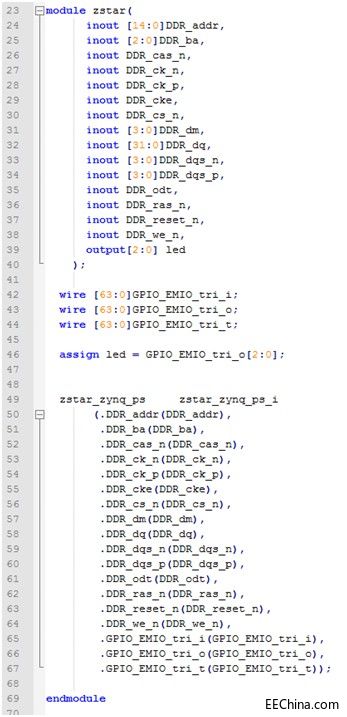

ДђПЊКѓЃЌПДЕНPSЯЕЭГЕФР§ЛЏВПЗжШчЭМЫљЪОЃЌПЩвдИДжЦЕНЮвУЧЕФаТНЈЕФЖЅВудДТыжаЃЌдкЖЅВудДТыжажиаТЩшжУНгПкгГЩфЁЃ

дкЪЕР§zstar_ex52жаЃЌЮвУЧжБНгЪЙгУPSЯЕЭГЩњГЩЕФzstar_zynq_ps_wrapper.vФЃПщзіЖЅВуФЃПщЃЌЕЋЪЧетбљЕФЗНЪНЦфЪЕЖдгкКЌгаPLДњТыЕФЙЄГЬРДЫЕСщЛюадВЛЙЛКУЁЃЮвУЧИќНЈвщДѓМвАбетИіzstar_zynq_ps_wrapper.vФЃПщРяУцР§ЛЏЕФPSЯЕЭГР§ЛЏЕНЮвУЧздМКЮЊPLЙЄГЬзЈУХаТНЈЕФЖЅВудДТыжаЃЌдкетИіЖЅВудДТыжаЃЌЮвУЧвВПЩвдР§ЛЏЦфЫќЕФPLТпМФЃПщЁЃ ЗЯЛАЫЕСЫЃЌЯШаТНЈвЛИіzstar.vЕФVerilogФЃПщЃЌШЛКѓзіШчЯТБрМЁЃ

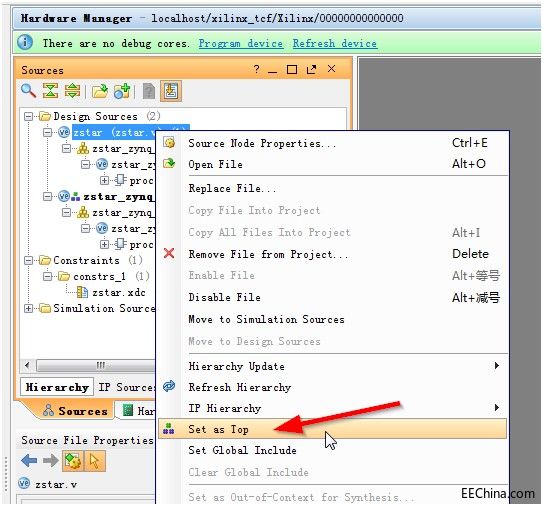

ШєвЊНЋаТНЈЕФzstar.vФЃПщзїЮЊPLЙЄГЬЕФЖЅВуФЃПщЃЌашвЊЯШбЁжаzstar.vФЃПщЃЌгвМќЕЅЛїбЁжаВЫЕЅЯюSet as TopЁЃ

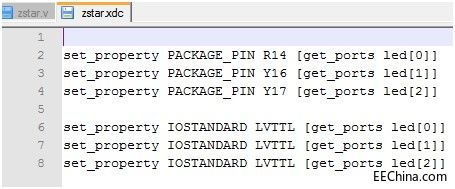

ЭЌЪБашвЊДђПЊSources --> Constraints - constrs_1ЯТЕФдМЪјЮФМўzstar.xdcЃЌдіМгled[2:0]ЕФв§НХдМЪјЁЃ

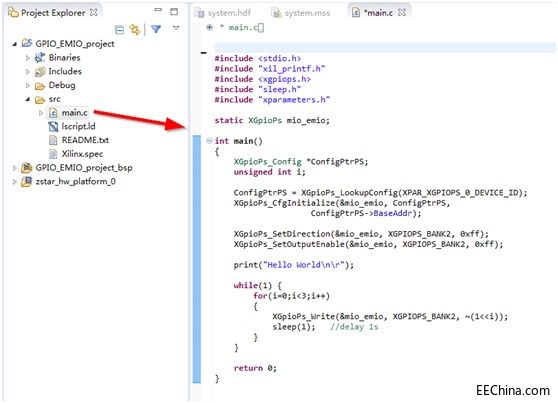

ВЮПМЮФЕЕЁЖЭцзЊZynq-ЙЄОпЦЊЃКЕМГіPSгВМўХфжУКЭаТНЈSDKЙЄГЬ.pdfЁЗЁЃ SDKжаЃЌаТНЈEmptyЕФФЃАхЙЄГЬЃЌУћГЦЮЊGPIO_EMIO_projectЁЃ еЙПЊаТНЈЕФЙЄГЬGPIO_EMIO_projectЃЌбЁжаЮФМўМаsrcЃЌЕЅЛїгвМќЃЌЕЏГіВЫЕЅжабЁдёNew --> Source FileЁЃ аТНЈвЛИіУћЮЊmain.cЕФDefault C source templateдДЮФМўЁЃ ЪфШыEMIOПижЦЕФbit2-0в§НХЕФГЬађЃЌГЬађжаЪЕЯжEMIO0ЁЂEMIO1КЭEMIO2бЛЗРИпЃЌж№ДЮЕуСС3ИіLEDжаЕФ1ИіЁЃ

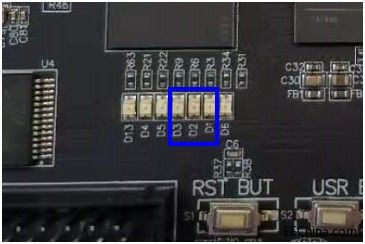

дкZstarАхзгЩЯЃЌЩшжУЬјЯпУБP3ЮЊJTAGФЃЪНЃЌМДPIN2-3ЖЬНгЁЃ СЌНгКУДЎПкЯпЃЈUSBЯпСЌНгPCЕФUSBЖЫПкКЭZstarАхЕФUARTНгПкЃЉКЭXilinxЯТдиЯпЃЈЯТдиЦїСЌНгPCЕФUSBЖЫПкКЭZstarАхЕФJTAGВхзљЃЉЁЃЪЙгУ5VЕчдДИјАхзгЙЉЕчЁЃ НгзХВЮПМЁЖЭцзЊZynq-ЙЄОпЦЊЃКSDKдкЯпдЫааТуХмГЬађ.pdfЁЗНЋzstar.bitЮФМўКЭGPIO_EMIO_project.elfЮФМўЩеТМЕНZynqжадЫааЦ№РДЁЃ ГЬађдЫааЦ№РДКѓЃЌЮвУЧОЭПЩвдПДЕНZstarАхЩЯPLВрЕФ3ИіLEDжИЪОЕЦD3ЁЂD2КЭD1ж№ИіЩСЫИЦ№РДЁЃ

ЬкбЖЮЂдЦСДНгЃКhttps://share.weiyun.com/5s6bA0s АйЖШЭјХЬСДНгЃКhttps://pan.baidu.com/s/1XTQtP5LZAedkCwQtllAEyw ЬсШЁТыЃКld9c |

ЭјгбЦРТл