|

ЙцдђвЛЃКИпЫйаХКХзпЯпЦСБЮЙцдђ

ЁЁЁЁШчЩЯЭМЫљЪОЃК

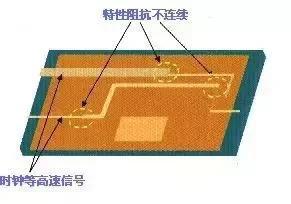

ЁЁЁЁдкИпЫйЕФPCBЩшМЦжаЃЌЪБжгЕШЙиМќЕФИпЫйаХКХЯпЃЌзпашвЊНјааЦСБЮДІРэЃЌШчЙћУЛгаЦСБЮЛђжЛЦСБЮСЫВПЗжЃЌЖМЪЧЛсдьГЩEMIЕФаЙТЉЁЃ

ЁЁЁЁНЈвщЦСБЮЯпЃЌУП1000milЃЌДђПзНгЕиЁЃ

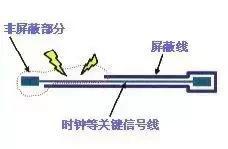

ЁЁЁЁЙцдђЖўЃКИпЫйаХКХЕФзпЯпБеЛЗЙцдђ

ЁЁЁЁгЩгкPCBАхЕФУмЖШдНРДдНИпЃЌКмЖрPCB LAYOUTЙЄГЬЪІдкзпЯпЕФЙ§ГЬжаЃЌКмШнвзГіЯжетжжЪЇЮѓЃЌШчЯТЭМЫљЪОЃК

ЁЁЁЁЪБжгаХКХЕШИпЫйаХКХЭјТчЃЌдкЖрВуЕФPCBзпЯпЕФЪБКђВњЩњСЫБеЛЗЕФНсЙћЃЌетбљЕФБеЛЗНсЙћНЋВњЩњЛЗаЮЬьЯпЃЌдіМгEMIЕФЗјЩфЧПЖШЁЃ

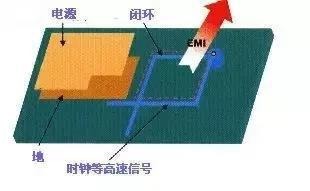

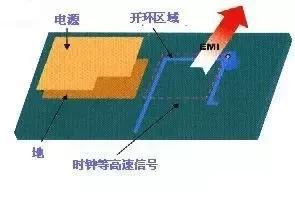

ЁЁЁЁЙцдђШ§ЃКИпЫйаХКХЕФзпЯпПЊЛЗЙцдђ

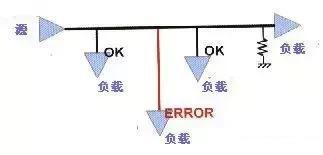

ЁЁЁЁЙцдђЖўЬсЕНИпЫйаХКХЕФБеЛЗЛсдьГЩEMIЗјЩфЃЌЭЌбљЕФПЊЛЗЭЌбљЛсдьГЩEMIЗјЩфЃЌШчЯТЭМЫљЪОЃК

ЁЁЁЁЪБжгаХКХЕШИпЫйаХКХЭјТчЃЌдкЖрВуЕФPCBзпЯпЕФЪБКђВњЩњСЫПЊЛЗЕФНсЙћЃЌетбљЕФПЊЛЗНсЙћНЋВњЩњЯпаЮЬьЯпЃЌдіМгEMIЕФЗјЩфЧПЖШЁЃдкЩшМЦжаЮвУЧвВвЊБмУтЁЃ

ЁЁЁЁЙцдђЫФЃКИпЫйаХКХЕФЬиадзшПЙСЌајЙцдђ

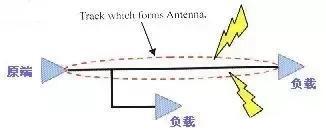

ЁЁЁЁИпЫйаХКХЃЌдкВугыВужЎМфЧаЛЛЕФЪБКђБиаыБЃжЄЬиадзшПЙЕФСЌајЃЌЗёдђЛсдіМгEMIЕФЗјЩфЃЌШчЯТЭМЃК

ЁЁЁЁвВОЭЪЧЃКЭЌВуЕФВМЯпЕФПэЖШБиаыСЌајЃЌВЛЭЌВуЕФзпЯпзшПЙБиаыСЌајЁЃ

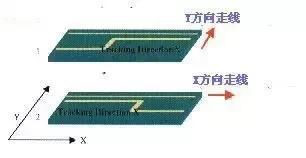

ЁЁЁЁЙцдђЮхЃКИпЫйPCBЩшМЦЕФВМЯпЗНЯђЙцдђ

ЁЁЁЁЯрСкСНВуМфЕФзпЯпБиаызёбДЙжБзпЯпЕФддђЃЌЗёдђЛсдьГЩЯпМфЕФДЎШХЃЌдіМгEMIЗјЩфЃЌШчЯТЭМЃК

ЁЁЁЁЯрСкЕФВМЯпВузёбКсЦНЪњДЙЕФВМЯпЗНЯђЃЌДЙжБЕФВМЯпПЩвдвжжЦЯпМфЕФДЎШХЁЃ

ЁЁЁЁЙцдђСљЃКИпЫйPCBЩшМЦжаЕФЭиЦЫНсЙЙЙцдђ

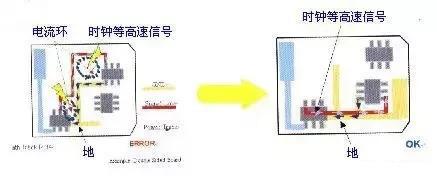

ЁЁЁЁдкИпЫйPCBЩшМЦжагаСНИізюЮЊживЊЕФФкШнЃЌОЭЪЧЯпТЗАхЬиадзшПЙЕФПижЦКЭЖрИКдиЧщПіЯТЕФЭиЦЫНсЙЙЕФЩшМЦЁЃдкИпЫйЕФЧщПіЯТЃЌПЩвдЫЕЭиЦЫНсЙЙЕФЪЧЗёКЯРэжБНгОіЖЈЃЌВњЦЗЕФГЩЙІЛЙЪЧЪЇАмЁЃ

ЁЁЁЁШчЩЯЭМЫљЪОЃЌОЭЪЧЮвУЧОГЃгУЕНЕФОеЛЈСДЪНЭиЦЫНсЙЙЁЃетжжЭиЦЫНсЙЙвЛАугУгкМИMhzЕФЧщПіЯТЮЊвцЁЃИпЫйЕФЭиЦЫНсЙЙЮвУЧНЈвщЪЙгУКѓЖЫЕФаЧаЮЖдГЦНсЙЙЁЃ

ЁЁЁЁЙцдђЦпЃКзпЯпГЄЖШЕФаГеёЙцдђ

ЁЁЁЁМьВщаХКХЯпЕФГЄЖШКЭаХКХЕФЦЕТЪЪЧЗёЙЙГЩаГеёЃЌМДЕБВМЯпГЄЖШЮЊаХКХВЈГЄ1ЃЏ4ЕФЪБКђЕФећЪ§БЖЪБЃЌДЫВМЯпНЋВњЩњаГеёЃЌЖјаГеёОЭЛсЗјЩфЕчДХВЈЃЌВњЩњИЩШХЁЃ

ЁЁЁЁЙцдђАЫЃКЛиСїТЗОЖЙцдђ

ЁЁЁЁЫљгаЕФИпЫйаХКХБиаыгаСМКУЕФЛиСїТЗОЖЁЃНќПЩФмЕФБЃжЄЪБжгЕШИпЫйаХКХЕФЛиСїТЗОЖзюаЁЁЃЗёдђЛсМЋДѓЕФдіМгЗјЩфЃЌВЂЧвЗјЩфЕФДѓаЁКЭаХКХТЗОЖКЭЛиСїТЗОЖЫљАќЮЇЕФУцЛ§ГЩе§БШЁЃ

ЁЁЁЁЙцдђОХЃКЦїМўЕФЭЫёюЕчШнАкЗХЙцдђ

ЁЁЁЁЭЫёюЕчШнЕФАкЗХЕФЮЛжУЗЧГЃЕФживЊЁЃВЛКЯРэЕФАкЗХЮЛжУЃЌЪЧИљБОЦ№ВЛЕНЭЫёюЕФаЇЙћЁЃЭЫёюЕчШнЕФАкЗХЕФддђЪЧЃКППНќЕчдДЕФЙмНХЃЌВЂЧвЕчШнЕФЕчдДзпЯпКЭЕиЯпЫљАќЮЇЕФУцЛ§зюаЁЁЃШчашСЫНтИќЖрPCBЩшМЦжЊЪЖПЩвдЕЧТНwww.jiepei.com/g590

|

ЭјгбЦРТл