гТИвЕФаОАщФуЭцзЊAltera FPGAСЌди66ЃКSRAMЖСаДВтЪд

ЗЂВМЪБМфЃК2018-5-3 21:09

ЗЂВМепЃКrousong1989

|

гТИвЕФаОАщФуЭцзЊAltera FPGAСЌди66ЃКSRAMЖСаДВтЪд ЬиШЈЭЌбЇЃЌАцШЈЫљга ХфЬзР§ГЬКЭИќЖрзЪСЯЯТдиСДНгЃК http://pan.baidu.com/s/1i5LMUUD

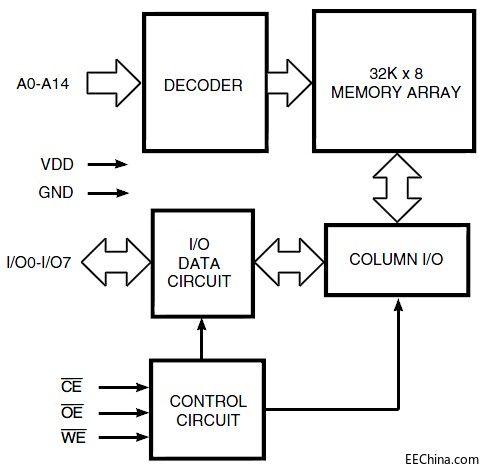

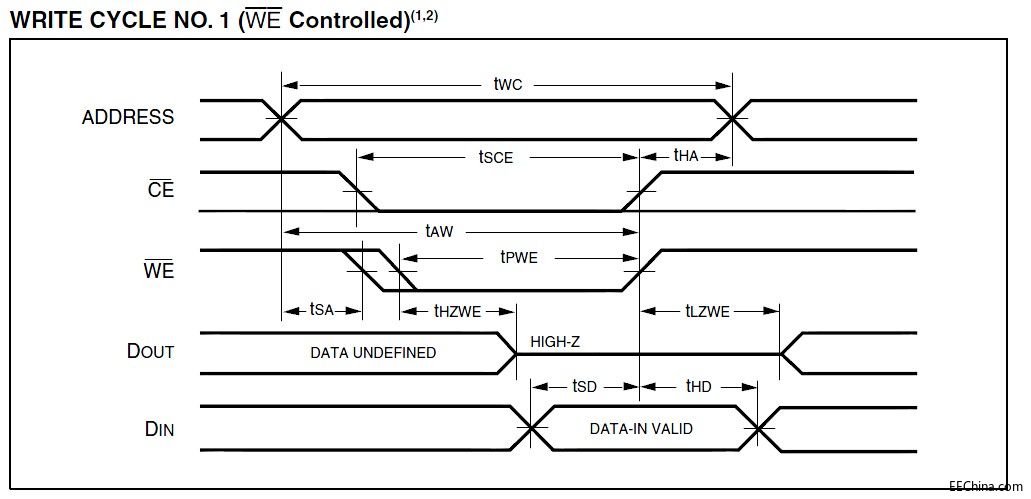

ДцДЂЦїЦЬЬьИЧЕиЃЌВЂЧвЪЧИїИіДѓаЁМЦЫуЛњЯЕЭГЃЈАќРЈЧЖШыЪНЯЕЭГЃЉБиВЛПЩЩйЕФВПЗжЁЃПЩвдКСВЛПфеХЕФНВЃЌгаЪ§ОнДЋЪфДІРэЕФЕиЗНБиЖЈгаДцДЂЦїЃЌВЛЙмЪЧCPUФкЧЖЕФЛђЭтЙвЕФЃЌдкзіДњТыДцДЂЛђГЬађдЫааЕФЪБКђвВБиЖЈЩйВЛСЫЫќЁЃЖјБОНкЕФЪЕбщЖдЯѓSRAMЃЈStatic RAMЃЉЪЧвЛжжвьВНДЋЪфЕФвзЪЇДцДЂЦїЃЌЫќЖСаДДЋЪфНЯПьЃЌПижЦЪБађвВВЛИДдгЃЌвђДЫФПЧАгазХЗЧГЃЙуЗКЕФгІгУЁЃ ФуевРДШЮКЮвЛПХSRAMаОЦЌЕФdatasheetЃЌЛсЗЂЯжЫќУЧЕФЪБађВйзїДѓЭЌаЁвьЃЌдкетРязмНсвЛаЉЫќУЧЙВадЕФЖЋЮїЃЌвВЬсвЛаЉгУVerilogМђЕЅЕФПьЫйВйзїSRAMЕФММЧЩЁЃSRAMФкВПЕФНсЙЙШчЭМ8.34ЫљЪОЃЌвЊЗУЮЪЪЕМЪЕФMomoryЧјгђЃЌFPGAБиаыЫЭЕижЗЃЈA0-A14ЃЉКЭПижЦаХКХЃЈCE#\OE#\WE#ЃЉЃЌSRAMФкВПгагыДЫЖдгІЕФЕижЗвыТыЃЈdecoderЃЉКЭПижЦДІРэЕчТЗЃЈcontrol circuitЃЉЁЃетбљЃЌЪ§ОнзмЯпЃЈI/O0-I/O7ЃЉЩЯЕФЪ§ОнОЭПЩвдЯргІЕФЖСЛђаДСЫЁЃ

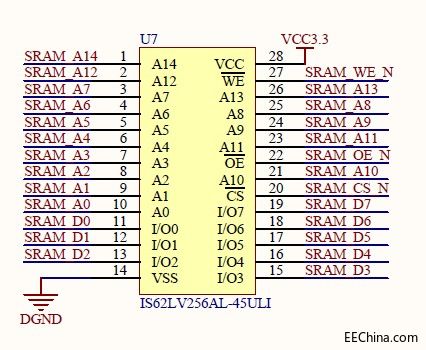

ЭМ8.34 SRAMЙІФмПђЭМ етРяОЭвдБОЪЕбщЪЙгУЕФIS62LV256-45UЮЊР§НјааЫЕУїЁЃЦфЙмНХЖЈвхШчБэ8.3ЫљЪОЁЃ Бэ8.3 SRAMНгПкЖЈвх

БОЩшМЦЕФгВМўдРэЭМШчЭМ8.35ЫљЪОЁЃ

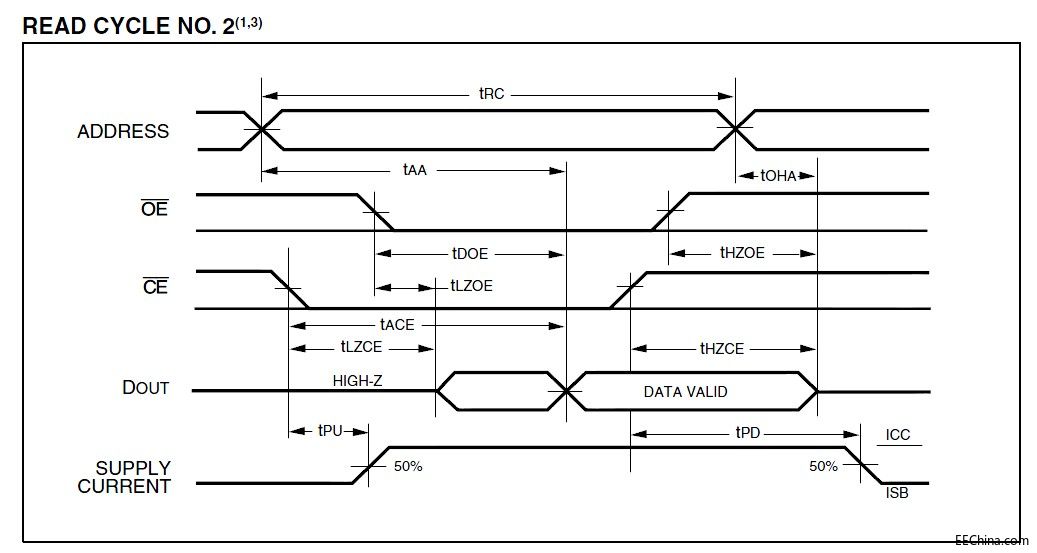

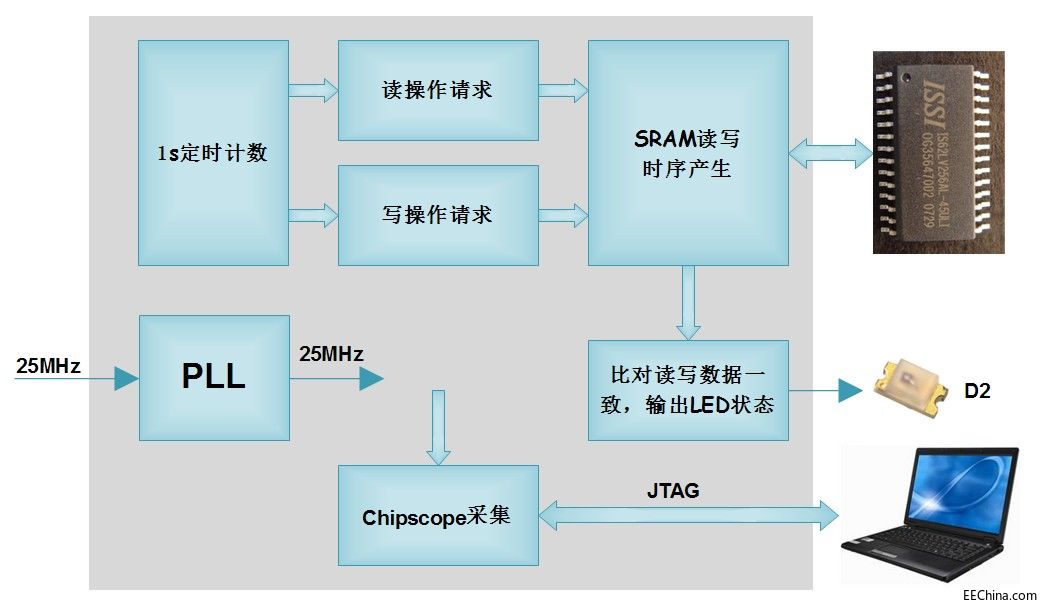

ЭМ8.35 SRAMНгПк ЖдгкSRAMЕФЖСВйзїЪБађЃЌЦфВЈаЮШчЭМ8.36ЫљЪОЁЃ

ЭМ8.36 SRAMЖСЪБађ ЖдгкSRAMЕФаДВйзїЪБађЃЌЦфВЈаЮШчЭМ8.37ЫљЪОЁЃ

ЭМ8.37 SRAMаДЪБађ ОпЬхВйзїЪЧетбљЕФЃЌвЊаДЪ§ОнЪБЃЌЃЈетРяЪЧЯрЖдгкгУFPGAВйзїSRAMЖјбдЕФЃЌШэМўЖСаДПЩФмгаЪБМфЫГађЕФЮЪЬташвЊзЂвтЃЉЃЌБШНЯИпаЇТЪЕФВйзїЪЧЫЭЪ§ОнКЭЕижЗЃЌАбCE#КЭWE#РЕЭЁЃШЛКѓбгЪБfile:///C:/Users/ADMINI~1/AppData/Local/Temp/msohtmlclip1/01/clip_image012.gifЪБМфдйАбCE#КЭWE#РИпЃЌетЪБОЭАбЪ§ОнаДШыСЫЯргІЕижЗСЫЃЌОЭетУДМђЕЅЁЃЖСЪ§ОнОЭИќМђЕЅСЫЃЌжЛвЊАбашвЊЖСГіЕФЕижЗЗХЕНSRAMЕФЕижЗзмЯпЩЯЃЌАбCE#КЭOE#РЕЭЃЌШЛКѓбгЪБfile:///C:/Users/ADMINI~1/AppData/Local/Temp/msohtmlclip1/01/clip_image014.gifЪБМфКѓОЭПЩвдЖСГіЪ§ОнСЫЁЃЪБађЭМжаСаГіЕФЯрЙиЪБМфВЮЪ§ШчБэ8.4ЫљЪОЁЃ Бэ8.4 SRAMЖСаДЪБађБэ

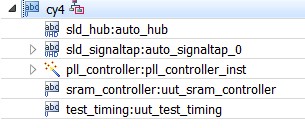

ШчЭМ8.38ЫљЪОЃЌБОЪЕР§УПУыжгЖЈЪБНјаавЛИіSRAMЕижЗЕФЖСКЭаДВйзїЁЃЖСаДЪ§ОнБШЖдКѓЃЌЭЈЙ§D2 LEDзДЬЌНјаажИЪОЁЃгыДЫЭЌЪБЃЌвВПЩвдЭЈЙ§SignalTap IIдкQuartus IIжаВщПДЕБЧАВйзїЕФSRAMЖСаДЪБађЁЃ

ЭМ8.38 SRAMЪЕР§ЙІФмПђЭМ ИУЪЕР§ЕФЙЄГЬФЃПщЛЎЗжВуДЮШчЭМ8.39ЫљЪОЁЃ

ЭМ8.39 SRAMЪЕР§ФЃПщВуДЮ |

ЭјгбЦРТл