基于FPGA的软件无线电平台设计

发布时间:2010-11-8 15:14

发布者:eetech

|

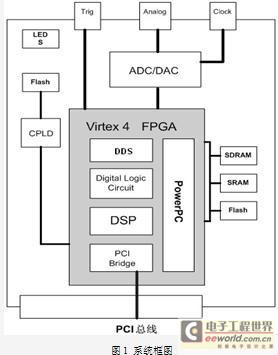

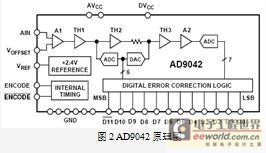

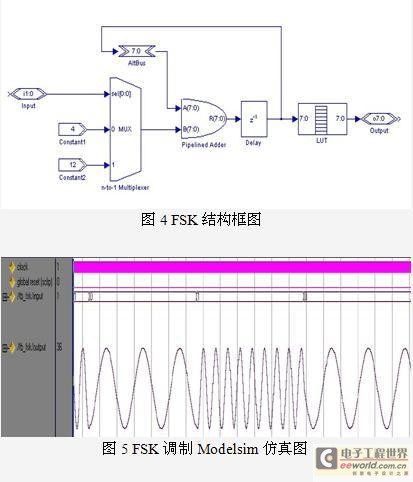

软件无线电的出现,是无线电通信从模拟到数字、从固定到移动后,由硬件到软件的第三次变革。简单地说,软件无线电就是一种基于通用硬件平台,并通过软件可提供多种服务的、适应多种标准的、多频带多模式的、可重构可编程的无线电系统。软件无线电的关键思想是,将AD(DA)尽可能靠近天线和用软件来完成尽可能多的无线电功能。 蜂窝移动通信系统已经发展到第三代,3G系统进入商业运行一方面需要解决不同标准的系统间的兼容性;另一方面要求系统具有高度的灵活性和扩展升级能力,软件无线电技术无疑是最好的解决方案。用ASIC(Application Specific Intergrated Circuits)和DSP(Digital Singnal Processor)芯片搭建软件无线电平台是目前系统设计的主要方法,这种方法有两个突出缺点:一是系统速度跟不上高速动态实时数字信号处理,二是系统体积大功耗高。这两个突出缺点制约了软件无线电在高速实时通信领域的应用前景。本文运用目前基于FPGA(Field Programmable Gate Array)的SoPC (System on Programmable Chip)技术构建软件无线电平台。大大提高了数字信号处理的能力和速度,并且降低了系统功耗,缩小了系统体积,为更高层次的3G无线通信要求提供了解决方案。 1 无线通信系统设计 1.1 系统设计 软件无线电使得无线电具有更多的个性化特点,它以软件方式定义多个频段及多种调制波形接口。软件无线电系统包括信号发射和接收两部分,本文重点以接收流程进行论述。软件无线电的RF(Radio Frequency)部分是一个多波束天线阵,可同时接收多个频段、多个方向的射频信号,并将射频转换为中频信号[6"9]。如图1所示,系统中包括Virtex-4 FX系列FPGA,模拟信号输入端口,同步触发端口,外接时钟源,Flash(加载FPGA配置程序),CPLD,SDRAM,PCI接口,LED信号灯等部分。 提取用户窄带信号进行抽取由专用ADC芯片完成,数字下变频部分由FPGA中的IP(Intellectual Property)模块完成。用专用芯片进行模数转换可以提高系统的稳定性和可靠性;用IP模块完成数字下变频功能可以降低功耗,提高速率。 数字下变频后进行解调,经过解调后的信号为一个比特流序列,比特流处理部分需要完成信息的加密解密、编码译码等。如图1所示,这部分功能可以用Verilog-HDL语言编写DSP处理模块完成,也可以用Matlab的FDATool进行设计后自动生成Verilog-HDL源代码和PowerPC指令程序;本文采用Verilog-HDL直接编写DSP模块的办法,这样可以对硬件处理流程进行更好的掌控,并且获得更高的信号处理性能。由于将DSP模块嵌入FPGA中,通过增加或减少DSP逻辑电路可以使得设计更加灵活,例如可以将2FSK调制解调,FIR滤波和FFT分别封装成为单元模块,编写地址驱动后PowerPC程序执行时可直接进行调用,相比DSP专用处理器仅调用乘法器和移位寄存器的方法可以节省上百个指令周期,大大提高了实时信号处理的能力,具有在高端领域广阔的应用前景。 比特流序列处理完成后,可将数据传入主机磁盘阵列经行储存,PowerPC通过PCI桥控制本系统和主机的数据传输,以满足未来数据回放和可视化界面要求。  1.2 ADC模数转换 软件无线电要求ADC,DAC尽可能的靠近天线,这需要很高的ADC的采样率,采样精度,动态范围等特征[11"13]。AD9042是一款高性能高速ADC芯片,采用的是两级子区式转换结构,这种设计既保证了所需的转换精度和转换速度,又降低了功耗,同时也减小了芯片尺寸,AD9042系统原理如图2所示[10]。AD9042可以保证的最小采样率可达41MHZ, 12bit精度,80dB无寄生动态范围。  1.3 DDS直接频率合成 由于数字信号处理的处理速度有限,往往难以对A/D采样得到的高速率数字信号直接进行各种类别的实时处理。为了解决这一矛盾,需要采用数字下变频技术,将采样得到的高速率信号变成低速率基带信号,以便进行下一步的信号处理。数字下变频技术在软件无线电和各类数字化接收机中得到了广泛应用。宽带数字下变频器基于外差接收机的原理,包括数字混频、低通滤波、抽取三个环节[12]。抽取后得到和信号带宽匹配的基带抽样信号,实现从宽频带中提取窄带信号的目的。Xilinx提供的专用DDS(Direct Digital Synthesizer) IP模块用以实现数字下变频功能。 1.4 CPU控制单元 Virtex-4 FX系列FPGA集成了运行速度高达450 MHz的双32位嵌入式PowerPC,每个处理器可提供超过700 Dhrystone MIPS的性能,是普通FPGA中处理器性能的三倍。两个完全集成的UNH认证的10/100/1000 Ethernet MAC进一步提升了Virtex-4 FX处理平台的性能,从而提高了FPGA资源的可用性。本系统以PowerPC作为该系统的指令处理和控制单元,可以避免纯硬件设计复杂,通用性差和不容易协调控制的缺点。PowerPC是本系统SoPC架构的核心组成部分,担负算法实现和中央控制两部分任务。Virtex-4 FX内部有大量乘法器可供调用,能够充分满足各种数字信号处理要求;PowerPC与前文提到用Verilog-HDL 设计的DSP模块连接,使整个系统具有实时动态信号的处理能力。PowerPC作为控制器的状态流程如图3所示。  2 FSK设计实例及仿真结果 在现代通信中,调制器的载波信号几乎都是正弦信号,数字基带信号通过调制器改变正弦载波频率,产生移频键控(FSK)信号。FSK时域表达式为  用本系统实现FSK调制结构框图如图4所示,用Verilog-HDL语言编写实现的FSK调制模块,相对于传统软件无线电的实现方式,省去了读取指令周期的时间,总运算时间缩短了一半。FSK调制的ModelSim波形仿真结果如图5所示。  3 结 论 改进的基于FPGA的嵌入式软件无线电系统,可更好地满足通信、雷达、数字电视等高科技领域对信号处理实时性的要求。运用软件无线电和SoPC技术,极大的提高了系统动态实时信号的处理能力。在节约资源方面,以节省芯片数量计算,该系统相对于目前常规系统,节省功耗和体积可达30%以上。40MHZ时钟频率, 12bit精度,80dB无寄生动态范围,该系统可以应用于Cellular / PCS基站,多通道多模式接收机,GPS抗干扰接收机,相控阵接收机,频谱分析,3G无线通信等领域。 |

网友评论