ЛљгкGB3442-82ЕФМЏГЩдЫЗХВЮЪ§ВтЪдвЧЩшМЦ

ЗЂВМЪБМфЃК2010-10-28 09:46

ЗЂВМепЃКtechshare

|

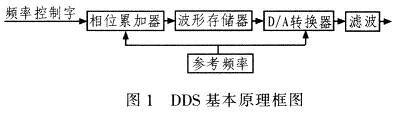

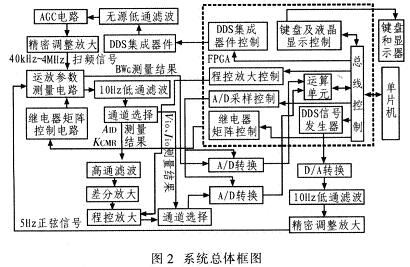

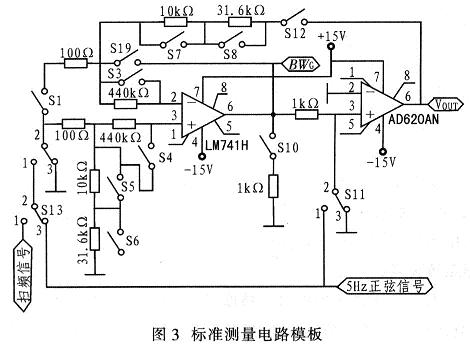

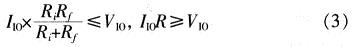

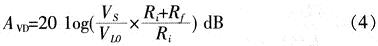

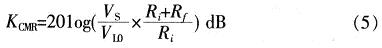

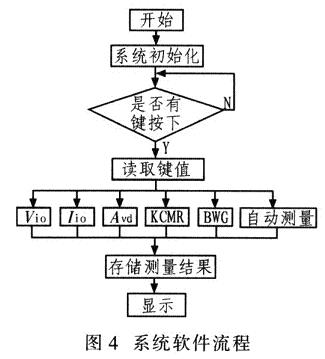

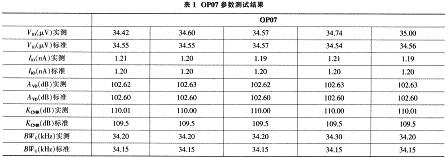

1 в§бд МЏГЩдЫЗХвдЦфМлИёЕЭСЎЁЂадФмгХдНЕШЬиЕудкИіШЫЪ§ОнжњРэЁЂЭЈаХЁЂЦћГЕЕчзгЁЂвєЯьВњЦЗЁЂвЧЦївЧБэЁЂДЋИаЦїЕШСьгђЕУЕНЙуЗКгІгУЁЃЫцзХЪ§зжММЪѕЕФВЛЖЯНјВНКЭМЏГЩЕчТЗЪаГЁЕФЗЂеЙЃЎМцгаФЃФтКЭЪ§зжМЏГЩЕчТЗЕФSOCЛђЛьКЯМЏГЩЕчТЗНЋдНРДдНЪмжиЪгЁЃгыДЫЭЌЪБЃЌМЏГЩдЫЗХВЮЪ§ЕФВтЖЈвВНЋЖдбаЗЂШЫдБКЭММЪѕвЧЦїЬсГіИќИпЕФвЊЧѓЃЌДЋЭГЕФдЫЗХВтЪдвЧаЃзМЗНАИвбВЛФмТњзуЪаГЁЬиБ№ЪЧЙњЗРОќЙЄЕФвЊЧѓЃЎдЫЗХВтЪдвЧЕФаЃзМУцСйбЯОўЬєеНЁЃвђДЫЃЌЬсИпдЫЗХВтЪдвЧЕФВтЪдОЋЖШЃЌБЃжЄдЫЗХЦїМўЕФзМШЗадЪЧФПЧАгІНтОіЕФЙиМќЮЪЬтЁЃ 2 ЯЕЭГЗНАИТлжЄ 2ЃЎ1 аХКХЗЂЩњЦїЗНАИТлжЄ ПМТЧЕНЕЅЦЌКЏЪ§ЗЂЩњЦїЕФЭтНгЕчзшЕчШнЖдВЮЪ§гАЯьКмДѓЃЌвђЖјВњЩњЕФЦЕТЪЮШЖЈЖШНЯВюЁЂОЋЖШЕЭЁЂПЙИЩШХФмСІЕЭЃЌЧвВЛвзПижЦЃЛЖјВЩгУЪ§зжЫјЯрЛЗЦЕТЪКЯГЩММЪѕЃЌгЩгкЫјЯрЛЗБОЩэЪЧвЛИіЖшадЛЗНкЃЌЫјЖЈЪБМфГЄЃЌЫљвдЦЕТЪзЊЛЛЪБМфвВЛсдіМгЃЌЭЌЪБЦЕТЪЪмVCOПЩБфЦЕТЪЗЖЮЇЕФгАЯьЃЌЦЕДјВЛФмзіЕУКмПэЁЃетРяВЩгУжБНгЪ§зжЦЕТЪКЯГЩММЪѕ(Direct Digital Frequency SynthesisЃЌМђГЦDDFSЛђDDS)ЁЃDDSвдNyquistЪБгђВЩбљЖЈРэЮЊЛљДЁЃЌдкЪБгђжаНјааЦЕТЪКЯГЩЃЌЭМ1ЮЊЦфЛљБОдРэПђЭМЁЃDDSЛљгкЯрЮЛРлМгКЯГЩММЪѕЃЌдкЪ§зжгђжаЪЕЯжЦЕТЪКЯГЩЃЌПЩЪфГіИпОЋЖШЕФЦЕТЪаХКХЃЌЦЕТЪЗЖЮЇДѓЁЂОЋЖШИпЁЂПижЦадФмКУЧввзЪЕЯжЁЃDDSзЈгУМЏГЩЦїМўЛљгкDDSдРэЃЌОпгазЊЛЛЫйЖШПьЁЂЗжБцТЪИпЁЂЦЕДјПэЕШЬиЕуЃЌПЩЪфГіЮШЖЈЕФИпЦЕаХКХЃЌЕЋВЛЪЪКЯВњЩњЕЭЦЕаХКХЁЃвђДЫЯЕЭГжа5HzЕЭЦЕаХКХгЩFPGAФкВПЕФDDSЬсЙЉЁЃ  2ЃЎ2 ВтСППижЦЕчТЗЗНАИТлжЄ ЮЊдкЭЌвЛЕчТЗжаЪЕЯжВЛЭЌВЮЪ§ЕФЗжВНВтСПМАздЖЏСПГЬзЊЛЛЃЌашЩшМЦЭЈЖЯПижЦЕчТЗЁЃвђДЫЃЌетРяВЩгУФЃФтПЊЙиЁЃвђДцдкЕМЭЈЕчзшЃЌдкбЁЭЈЪБИУЕчзшМггкЕчТЗЃЌЛсДјРДВтСПЮѓВюЃЛМЬЕчЦїЕМЭЈЕчзшНЯаЁЃЌЕЋЯрЖдгкФЃФтПЊЙиЙцФЃДѓЁЂЕчТЗЗжВМВЮЪ§ЃЌШнвзв§Ц№БеЛЗВтЪдЕчТЗЕФМФЩњеёЕДЃЛПМТЧЕНОЋЖШЃЌЯЕЭГбЁгУМЬЕчЦїПижЦВЛЭЌВЮЪ§ВтЪдЕчТЗЕФздЖЏзЊЛЛЃЌЭЈЙ§ЬэМгВЙГЅЕчШнРДБмУтеёЕДЃЌЮЊБмУтЪфГіВЈаЮЪЇецЃЌЯЕЭГЛЙВЩгУШ§МЋЙмЙВЗЂЩфМЋЕчТЗЖдМЬЕчЦїНјааПижЦЁЃ2ЃЎ3ЗљжЕМьВтЗНАИТлжЄЗНАИ1ЃКЪ§зжЗНЗЈЁЃгЩAЃЏDзЊЛЛЦїВЩбљКѓНЋЪ§ОнЫЭШыFPGAНјааЗхжЕМьВтЛђгааЇжЕМьВтЃЌИУЗНЪНПЩЬсИпОЋЖШКЭЮШЖЈЖШЃЌЧвБмУтСЫФЃФтЦїМўВЛЮШЖЈЛђЦЏвЦЕШвђЫиЕФгАЯьЃЌЕЋЪм AЃЏDзЊЛЛЦїВЩбљЫйТЪЕФЯожЦЃЌЫљДІРэЕФаХКХЦЕТЪДяВЛЕНКмИпЁЃЗНАИ2ЃКФЃФтЗНЗЈЁЃАќРЈЗхжЕМьВЈКЭгааЇжЕМьВЈЁЃЧАепЭЈЙ§ПижЦЕчШнГфЗХЕчЫйЖШЪЕЯжЃЌКѓепЛљгкНЛСїаХКХгааЇжЕЖЈвхЪНЃЌВЩгУФЃФтЕчТЗЪЕЯжЃЌЕфаЭгааЇжЕМьВтЦїМўШчAD637ЁЃЯЕЭГдкВтСПAVDЁЂKCMRЪБЃЌЪфГіаХКХЕФНЛСїЗжСПЦЕТЪЮЊ5 HzЃЌЙЪВЩгУЗНАИ1ЃЛВтСПдівцДјПэЛ§BWGЪБЃЌЪфГіЦЕТЪЗЖЮЇЮЊ40 kHzЁЋ4 MHzЃЌЙЪВЩгУЗНАИ2ЁЃ ИљОнвдЩЯЗНАИТлжЄЃЌЯЕЭГзмЬхПђЭМШчиш2ЫљЪОЁЃЯЕЭГжївЊгЩаХКХЗЂЩњЁЂВЮЪ§ВтЪдЁЂВтЪдЕчТЗПижЦКЭШЫЛњНЛЛЅЕШФЃПщзщГЩЃЌЕЅЦЌЛњКЭFPGAЙВЭЌПижЦФЃПщЁЃ5 HzаХКХгЩFPGAФкВПDDSВњЩњЃЌЩЈЦЕаХКХгЩAD9851ВњЩњЃЛВтСПЕчТЗЕФЪфГіНсЙћОКѓМЖТЫВЈЁЂЗХДѓДІРэКѓгЩAЃЏDзЊЛЛЦїВЩбљЫЭжСFPGAНјаадЫЫуЃЛЕЅЦЌЛњКЭFPGAЭЈЙ§МЬЕчЦїбЁдёвдВтСПЕчТЗКЭВтСПСПГЬЃЛFPGAЬсЙЉМќХЬКЭЯдЪОЦївдЪЕЯжШЫЛњНЛЛЅЃЛВтСПНсЙћДцДЂдкRAMжаЃЌВЂФмЭЈЙ§ЮЂаЭДђгЁЛњДђгЁГіРДЁЃ  3 РэТлЗжЮігыжївЊЕчТЗЩшМЦ 3ЃЎ1 аХКХдДЕФЪЕЯж 5 HzаХКХВњЩњЕФВЮПМЦЕТЪЮЊfCLK=1 MHzЃЌЯрЮЛРлМгЦїЕФЮЛЪ§ЪЧ32ЃЌЦЕТЪПижЦзжЮЊ21 475ЃЌЦфЪфГіЦЕТЪдђЮЊ(106ЃЏ232)ЁС21475Ёж5ЃЎ000 038 1 HzЃЌЖјЯрЖдЮѓВюЕФОјЖджЕЮЊ(5ЃЎ000 038 1-5)ЃЏ5ЁС100ЃЅЁж0ЃЎ000 762ЃЅЁЃ5 HzаХКХЖдDЃЏAзЊЛЛЫйТЪвЊЧѓВЛИпЃЌЮЊЬсИпОЋЖШЃЌЯЕЭГбЁгУ12ЮЛDЃЏAзЊЛЛЦїМўMX7541ЁЃ 40 kHzЁЋ4 MHzЩЈЦЕаХКХгЩDDSзЈгУЦїМўAD9851ВњЩњЁЃЭЈЙ§ЖдЪфГіе§ЯвВЈЕФЦЕТЪНјааВННјПижЦПЩЪЕЯжЩЈЦЕЪфГіЁЃЦЕТЪЗжБцТЪЩшЮЊ1 kHzЃЌШчЙћвд1 kHzЮЊЦЕТЪВННјжЕЃЌдђашвЊВННј(4ЁС106-40x103)ЃЏ1 000=3 960ДЮЃЌЖјвЊЧѓЩЈУшЪБМфаЁгкЕШгк10 sЁЃЩЈУшЫйЖШгІДѓгкЕШгк10 sЃЏ3 960=2ЃЎ525ДЮЃЏmsЁЃПМТЧЕНЪЕВтЦїМўЕФЧщПіЃЌЮЊБЃжЄВтСПЕФПЩППадЃЌВЩгУЗЧЕШВНГЄВННјЃЌМДЫцзХЦЕТЪдіМгЃЌВННјСПдіМгЃЌдкНгНќНижЙЦЕТЪЕуЪБМѕаЁВННјЦЕТЪЃЌБЃжЄЦЕТЪЗжБцТЪЮЊ1 kHzЁЃ дкAD9851ЪфГіМЖНгНижЙЦЕТЪЮЊ15 MHzЕФЭждВТЫВЈЦїРДвжжЦИпЦЕаГВЈИЩШХЃЌВЂЭЈЙ§AD603ЙЙГЩЕФAGCЕчТЗКЭОЋУмЕїећЗХДѓЕчТЗЪЙЪфГігааЇжЕЮШЖЈдк2 VЁЃ 3ЃЎ2 дЫЗХВЮЪ§ВтЪдЕчТЗ ЯЕЭГВЩгУЁАБЛВтЦїМўвЛИЈжњдЫЗХЁБФЃЪНЙЙГЩЮШЖЈЕФИКЗДРЁЭјТчЁЃЪЙЪфГіЕчбЙѓщЮЛгкдЄжУЕчбЙЃЌДгЖјНЋаЁЕчбЙЁЂаЁЕчСїЕФВтСПзЊЛЛЮЊЗќЬиМЖЕчбЙЕФВтСПЁЃИљОнVIOЁЂIIOЁЂKCMRЁЂBWGЕШ5ИіВЮЪ§ВтСПЕчТЗЕФЯрЫЦадНЋЦфМђЛЏЮЊвЛИіБъзМВтСПЕчТЗФЃАхЃЎЭЈЙ§АДМќбЁдёВЛЭЌВЮЪ§ЕФВтСПЕчТЗЃЌШчЭМ3ЫљЪОЁЃ  3ЃЎ2ЃЎ1 ЪфШыЪЇЕїЕчбЙVIOЁЂЪфШыЪЇЕїЕчСїIIOЕФВтСП БеКЯS1ЁЂS3ЁЂS4ЁЂS12ЃЌS2Ёњ3ЁЂS11Ёњ3ЃЌВтЕУИЈжњдЫЗХЕФЪфГіЕчбЙЮЊVIOЃЌдђгаЃК  дкжиИДVIOВтСПВНжшЕФЛљДЁЩЯдйЖЯПЊS3ЁЂS4ЃЌВтЕУИЈжњдЫЗХЕФЪфГіЕчбЙЮЊVLIЃЌдђгаЃК  дкВтСПVIOЪБЃЌRi=100 ІИЃЌRj=61ЃЎ6 kІИЃЌЦфОЋЖШОљЮЊ0ЃЎ3ЃЅЃЌгЩRiКЭRFдьГЩЕФзюДѓЮѓВюаЁгк0ЃЎ6ЃЅЃЛдкВтСПIIOЪБЃЌгІТњзуЃК  ЯЕЭГбЁШЁR=436 kІИЃЌIIOЁЋ(0ЃЌ4ІЬA)ЃЌVIOЁЋ(0ЃЌ40 mV)ЃЌвдЩЯСНИіЬѕМўОљФмТњзуЁЃ 3ЃЎ2ЃЎ2 ВюФЃПЊЛЗНЛСїЕчбЙдівцAVDЕФВтСП БеКЯS1ЁЂS3ЁЂS4ЁЂS10ЁЂS12ЃЌS2Ёњ3ЁЂS11Ёњ1ЃЌЩшаХКХдДЪфГіЕчбЙЮЊVSЃЌВтЕУИЈжњдЫЗХЪфГіЕчбЙЮЊVLOЃЌдђгаЃК  AVDЕФВтСПЮѓВюдкКмДѓГЬЖШЩЯШЁОігкЕчТЗжаR1ЁЂR2ЕФЦЅХфОЋЖШЃЌШєЦЅХфЮѓВюЮЊІФ=(R1-R2)/R2ЃЌІФ1=(Rf-Ri)/RiЃЌдђЕЅДПгЩЕчзшЪЇХфв§Ц№ЕФЯрЖдЮѓВюЮЊЁїA VD="20" log(ІФ+1)ЃЌИУЯЕЭГеМЮЊ0ЃЎ6ЃЅЁЃ 3ЃЎ2ЃЎ3 ЙВФЃвжжЦБШKCMRЕФВтСП БеКЯS1ЁЂS3ЁЂS4ЁЂS10ЁЂS12ЃЌS2Ёњ1ЁЂS11Ёњ3ЁЂS13Ёњ1ЃЌЩшаХКХдДЪфГіЕчбЙЮЊVSЃЌВтЕУИЈжњдЫЗХЪфГіЕчбЙЮЊVIOЃЌдђгаЃК  KCMRЕФВтСПЮѓВюдкКмДѓГЬЖШЩЯШЁОігкЕчТЗжаД§ВтдЫЗХСНЪфШыЖЫЕчзшЕФЦЅХфОЋЖШЃЌШєЦЅХфЮѓВюЮЊІФ1ЃЌдђЕЅДПгЩЕчзшЪЇХфв§Ц№ЕФЯрЖдЮѓВюЮЊЁїKCMR=20log(ІФ1+1)ЃЌІФ1=ІФЁЃ  4 ЯЕЭГВтСПгыЗжЮі РћгУИУЯЕЭГВтСПOP07ЁЂІЬA741ЁЂLF256ЕШЃЌдЫЗХЦїМўЕФВЮЪ§ПЩдкFPGAЯдЪОЦїЩЯЯдЪОЃЌКѓЙћБэУїЃЌИУВтЪдвЧВтСПОЋЖШИпЃЌЗћКЯЩшМЦвЊЧѓЃЌЦфжаБэ1ЪЧВтСПOP07НсЙћЁЃ  5 НсЪјгя ИУЯЕЭГЭъГЩСЫЖддЫЗХВЮЪ§VIO(0ЁЋ40 mV)ЁЂIIO(0ЁЋ4ІЬA)ЁЂAVD(60ЁЋ120 dB)ЁЂKCMRЕФВтСПЃЌ(ЮѓВюЗжБ№ЮЊ1ЃЅКЭЁР2 dB)ЃЌЖјЧвЛЙЪЕЯжСЫBWCЕФВтСПКЭздЖЏСПГЬзЊЛЛЙІФмЃЌЦфжаЩЈЦЕаХКХЕФВННјЦЕТЪЮЊ1 kHzЃЌЕчбЙгааЇжЕЮЊ(2ЁР0ЃЎ1)VЁЃЯЕЭГЭЈЙ§FPGAЬсЙЉМќХЬКЭЯдЪОЦїЕШШЫЛњНЛЛЅНчУцЁЃФмзМШЗЪЕЯжЖдВтСПЗНЪНЕФПижЦМАЯрЙиаХЯЂЕФЯдЪОЃЌЧвдіМгДЅУўЦСПижЦКЭДђгЁВтСПНсЙћЙІФмЃЌОпгаНЯКУЕФПЩжиИДадКЭВЮПМадЁЃСэЭтЃЌдкЯЕЭГжаЭЈЙ§ЖдгВМўЕФДІРэЃЌЯћГ§СЫвђЪЙгУМЬЕчЦїгЩЛЗТЗе§ЗДРЁДјРДЕФздМЄаЇгІЃЌНјвЛВНЬсИпСЫЯЕЭГЮШЖЈадЁЃ |

ЭјгбЦРТл