基于PC机的模拟信号发生器的设计

发布时间:2010-10-24 11:33

发布者:analog_tech

|

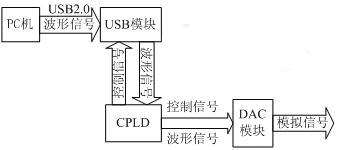

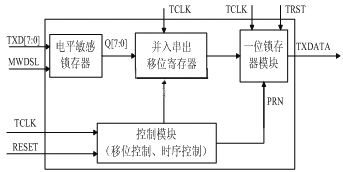

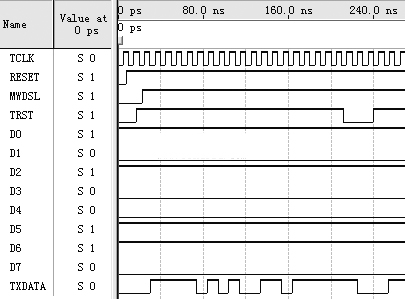

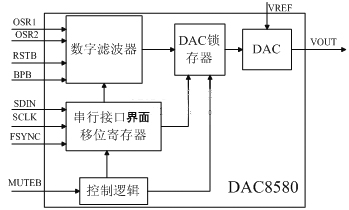

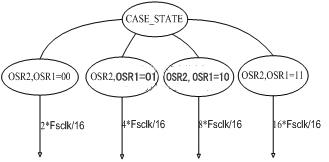

1 引言 在实际研发各种控制器、显示器等涉及到数据采集的电子仪器的时候,对这些产品进行性能测试是必不可少的。购买专用的信号发生器不但价格昂贵,而且可扩展性能较差;把研发的产品放到实际工作环境,不但不便于调试,而且很多工业现场也不允许。考虑到PC机的普及程度,可以利用现有的资源来设计一个模拟信号发生器,同时运用CPLD进行电路控制,可以方便的实现电路扩展。 2 模拟信号发生器设计与实现 2.1 设计思想 在PC机上产生波形信号通过USB2.0接口传入USB接收模块。USB接收模块将接收到的波形信号传输给CPLD。由于DAC8580是16位串行输入的DA转换器,CPLD需要对波形信号的数据格式进行并行到串行的转换。DAC8580对从CPLD传输过来的串行数据进行DA转换,输出所需的模拟信号。 模拟信号发生器整体框图如图一所示。  图一 整体框图 2.2 基于CPLD的数据并串行转换 DAC8580是串行输入的DA转换器,而从USB模块中传出的是并行数据,所以需要在CPLD中进行数据的并串行转换。数据转换器的工作原理图如图二所示,其中TXD[7:0]是并行数据输入信号,TCLK是数据转换器的时钟信号,RESET是数据转换器控制模块内部复位信号,MWDSL是电平敏感锁存器使能信号,TRST是一位锁存器模块复位信号,TXDATA是串行数据输出信号。当数据转换器开始工作的时候,电平敏感锁存器使能信号(MWDSL)有效,并行数据被送入锁存器,之后,控制模块产生并入串出移位寄存器装入信号(STLD),以在时钟信号(TCLK)的作用下,将并行数据装入并入串出移位寄存器,然后,控制模块再产生并入串出移位寄存器移位信号(STLD),并在时钟信号(TCLK)的作用下,将并行数据移出。  图二 数据并串行转换器工作原理图 本设计中采用Altera的CPLD(FLEX EPF10K20RC240)来实现数据转换器的硬件电路功能,并用Quartus Ⅱ软件进行源文件设计。在电路顶层,我们采用原理图和结构图的形式进行数据转换器的整体框架设计。Quartus Ⅱ为实现不同的逻辑功能提供了大 量的基本单元符号和宏功能模块,这些符号与模块的管脚定义与功能一般都是默认的,而在结构图输入方式中,我们可以根据自行定义模块的管脚与功能。结构图定义的模块上只是一些自行定义的方框和管脚符号, 没有涉及其内部具体逻辑, 因而这种模块称之为顶层模块。顶层模块的内部具体逻辑可以通过硬件描述语言来编写,也可以通过底层模块来充实和支持顶层模块。底层模块是与顶层模块相对的概念,一个源文件可以包涵多级模块,但是最底层的模块必然是一种由各种门和触发器等基本逻辑器件组成的基本原理图或者是用硬件描述语言描述的电路逻辑,可以说它是顶层原理图的内核所在。 电平敏感锁存器、一位锁存器模块以及控制模块部分调用系统库内的宏模块, 因为这一部分硬件电路已很成熟, 而且并不是很复杂。并入串出移位寄存器采用结构图方式输入,其内部具体逻辑通过VHDL硬件描述语言来实现,其VHDL 源文件如下: LIBRARY ieee; USE ieee.std_logic_1164.all; ENTITY parrial IS PORT ( STLD : IN STD_LOGIC; CLK : IN STD_LOGIC; Q1 : IN STD_LOGIC; Q2 : IN STD_LOGIC; Q3 : IN STD_LOGIC; Q4 : IN STD_LOGIC; Q5 : IN STD_LOGIC; Q6 : IN STD_LOGIC; Q7 : IN STD_LOGIC; Q8 : IN STD_LOGIC; shiftout : OUT STD_LOGIC ); END parrial; ARCHITECTURE parrial_architecture OF parrial IS signal latch : std_logic_vector (7 downto 0) ; begin process (CLK,STLD,Q1 ,Q2 ,Q3,Q4 ,Q5 ,Q6 ,Q7,Q8) begin if (CLK’event and CLK=‘1’) then if (STLD =‘1’) then latch(7) <= Q8; latch(6) <= Q7; latch(5) <= Q6; latch(4) <= Q5; latch(3) <= Q4; latch(2) <= Q3; latch(1) <= Q2; latch(0) <= Q1; else latch(0) <= latch(1) ; latch(1) <= latch(2) ; latch(2) <= latch(3) ; latch(3) <= latch(4) ; latch(4) <= latch(5) ; latch(5) <= latch(6) ; latch(6) <= latch(7) ; latch(7) <= ‘1’; end if ; end if ; end process; shiftout<=latch(0); END parrial_architecture; 通过调试、编译,最后得出仿真结果,接收的并行数据为:D0=‘1’,D1=‘0’,D2=‘1’,D3=‘0’,D4=‘0’,D5=‘1’,D6=‘1’,D7=‘0’,仿真图如图三所示。  图三 数据转换器仿真图 2.3 基于CPLD的DA转换 DAC8580是16位串行输入、电压输出,高速低噪声DA转换器,可以实现2~16倍内部插值。最高数据更新率为16MSPS。其内部逻辑电路如图四所示。  图四 DAC8580内部逻辑电路 DAC8580通过3条信号线与CPLD进行通信,这3跟信号线分别是:FSYNC(字节时钟信号)、SLCK(位时钟信号)、SDIN(串行数据输入)。输入数据在SCLK的上升沿被锁存在输入移位寄存器中(最高有效位最先输入),FSYNC的下降沿将最后一次接收到的一个16位的输入数据(被认证为有效的数据)从移位寄存器锁存到暂时存储器。暂时存储器可以通过管脚控制来选择连接到数字滤波器或者连接到DAC锁存器。在FSYNC的下降沿后的第二个SCLK的上升沿,数据被转移到DAC锁存器(数字滤波器关闭),或是转移到数字滤波器(数字滤波器开启)。数字滤波器的工作也需要一个持续的SCLK信号。 CPLD通过控制OSR2、OSR1、BPB、RSTB四个管脚的信号值,可以实现对DAC8580中的数字滤波器的设置。可以通过在CPLD中集成一个CASE结构来实现多频率的DA转换,串行数据输入频率与经过DAC内部数字滤波器插值后的数据频率关系如图五所示。  图五 插值后数据频率与输入频率的关系图 3 结束语 本文利用CPLD的逻辑控制技术和DAC8580高效的DA转换能力,完成了对PC机内产生的数字波形到模拟信号的转换。最后,通过软件仿真,得到了预期目标。 本文的创新点在于对传统的模拟信号发生器进行了创造性重构, 利用PC机和数模转换技术实现了模拟信号发生器的基本功能;并且由于CPLD可以以任意位宽实现运算,所以该设计可以方便的进行扩展,实现更高的系统精度。 |

网友评论