14位串行A/D转换器MAX194的特性及应用

发布时间:2010-10-10 21:30

发布者:eetech

|

在一些实时数据采集与信息处理电路中,要满足数据采集的精度和速度要求,以必须采用分辨率高,转换速度快的AD转换器。MAX194是一种性能优越的高精度、带采样保持的高速度十四位串行AD转换器。笔者在课题实践中应用了MAX194芯片取得了很好的效果。由于MAX194的输出方式是串行输出而与一般的并行输出方式不同,因此,在与MC51系列单片机通信时有一些需要注意的事项。在此笔者把在应用中遇到的问题及解决方法作以介绍。 1 工作原理及结构 MAX194 的工作原理框图如图1所示。它主要由主DAC、控制逻辑、比较器和校准DAC组成。主DAC用于产生与输入模拟信号进行比较的模拟信号,它的内部结构与一般模数转换器内部的DAC不同,它没有采用T型电阻网络,而是由带二进制权值的电容阵列组成(见图2).模拟电子开关受数字量的数字代码控制,代码为0时开关接地,代码为1时开关接到参考电压上。这样,d13为1而其它为0时,VA=VREF/2;当d12为1而其它为0时,VA=VREF/2 2;依次类推,直到当d0=1而其它为0时,VA=VREF/2 14。根据叠加原理,总的等效电势为: VA=d13VREF/2+d12VREF/2 2……+d0VREF/2 14   以单极性输入为例,其具体的转换过程如下: (1)将电容的自由端均接在AIN,以使电容充电得到电压VAIN。 (2)将最高位电容接参考电压,其它电容的自由端接地,以使VA=VAIN,即d13=1而其它位为0,这时,VA=VREF/2-VAIN,当VA<0 即VAIN<VREF/2时,比较器的输出为1,并通过控制逻辑使d13=0,反之使d13=1。在最高位确定后,如果使d12=1而其余为0,则 VA="d13VREF/2"+d12VREF/2 2-VAIN。 (3)要通过比较器和控制逻辑来确定次高位,依次向下类推,经过16次比较以可以使转换结束(包括两位附加位)。需要说明的是:图中的DUMMY电容是为了使它前面的电容具有权值而设置的,其本身没有权值。而由电容组成DAC将使MAX194具有采样保持功能,也就是电路不需加采样保持部分。 另外,MAX194自身具有校准功能,可在上电时进行校准。当外部环境改变时(如温度变化,电源电压改变等),还可以人为地置RESET为0时进行校准。 2 管脚排列及功能 MAX194的管脚排列如图3所示。它采用16脚DIP封装,各管脚的功能如下:

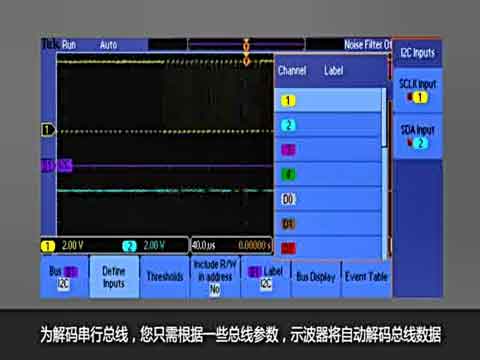

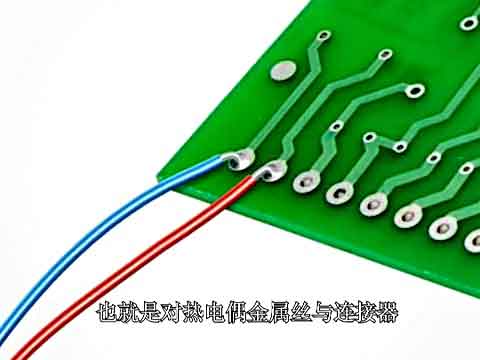

3 MAX194的应用电路 MAX194可广泛应用于工业控制,测量,数字信号处理等方面。 图4为笔者在锅炉测温系统中用MAX194与单睡机进行接口的接口电路,该接口将CS接P2.7脚,并由软件发出片选信号。用于转换的时间脉冲CLK由89C51的ALE脚产生。89C51的TXD经非门接SCLK,以用做读取数据的时钟。  读出转换结果有两种方式,一种是在转换的过程中以CLK的时钟频率读出,另一种是在转换结束后以SCLK的时钟频率读出。笔者选择在转换结束后读取结果的方式(第二种)。该方式在转换结束以后,当EOC变低并且在CS也为低时,在DOUT上输出最高位,之后在SCLK的下降沿依次输出其它位。SCLK允许的最高频率是5MHz。图5为其时序图。  图中,tCONV为转换时间;tCSS为CS下降模沿的时间;tCSH为SCLK最后一个下降沿至CS上升沿的时间。 4 注意事项 采用图4电路进行接口设计时,应注意以下几点; (1)Tcss必须大于75μs,应在程序中先置CS为零,然后再发转换开始信号。 (2)转换开始脉冲必须与转换时钟同步,为此在P1.0和ALE之间应加一个或门后再接至CONV,以确保同步。 (3)在TXD直接至SCLK相连时,由于89C51在TXD的下降沿读数,而TXD(SCLK)的第一个下降沿以开始输出次高位,这样以会丢失最高位。为此,可在TXD与SCLK之间接一个反相器,这样在TXD的下降沿读入数据时,即可在TXD的上升沿(SCLK的下降沿)使DOUT输出数据。由于读入数据和输出数据是分时进行的,因而保证了这种先读出最高位,再输出次高位的全数据输出方式。 (4)由于在收缓冲器SBUF中,数据的存储顺序为: d6 d7 d8 d9 d10 d11 d12 d13 所以要在程序中重新排列其顺序,图6为其程序框图,具体的程序如下: ADZHUAN:CLR PSW CLR C CLR P2.7 MOV P0,#02H MOV R1,#03H SETB P1.0 CLR P1.0 SETB P1.0 SETB P3.2 HERE:JB P3.2,HERE LOOP:MOV SCON,10H WAIT1:JNB RI,WAIT1 MOV A,SBUF MOV @R1,A INC R1 DJNZ R0,LOOP SETB P2.7 LCALL EXCH RET EXCH:MOV R1,30H MOV A,#00H CLR C MOV R7,#08H LOOP0:XCH A,R1 RRC A XCH A,R1 RLC A DJNZ R7,LOOP0 MOV 32H,A MOV R1,31H MOV A,#00H CLR C MOV R7,#08H LOOP1:XCH,A,R1 RRC A XCH A,R1 RLC A DJNZ R7,LOOP1 MOV 33H,A RET  |

网友评论