用户可定制的处理器

发布时间:2009-4-23 18:28

发布者:贾延安

|

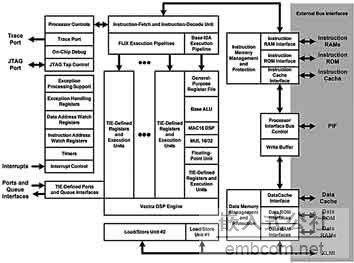

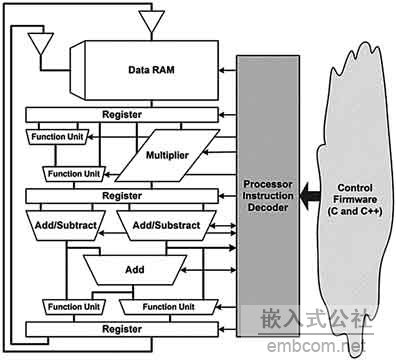

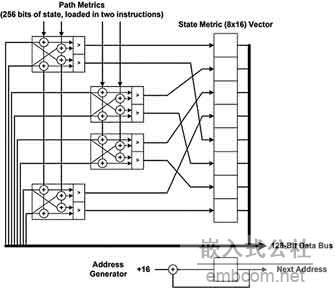

随着130nm和90nm工艺的成熟,每平方毫米的硅片面积上可以集成大约100K~200K的逻辑门,一颗面积大约50mm2的低成本芯片可以容纳5M~10M逻辑门。越来越多的SoC设计者正在试图将整个系统集成在一颗芯片上,但是他们也面临着严峻的挑战,因为传统的基于RTL的SoC硬件设计方法的缺点正日益显现出来: ● 设计能力——以前,硅片容量和自动化设计工具的能力将一个RTL模块的规模限制在100K左右,如今在一个硅片上即使是500K逻辑门的模块也不会受到这些限制,但是设计方法却没能跟上硅片容量增长的脚步。 ● 验证困难——一个典型逻辑模块的内部设计复杂度以及潜在的出错可能性随着其逻辑门数的增加而迅速增大,这导致了验证的难度不成比例的增加。许多SoC设计团队声称他们90%的工作量花在了验证工作上。 ● 修复成本——修复SoC设计中错误的成本正在增加。人力成本和NRE费用都在不断增加,与此同时利润率及市场份额却在不断下降,这使得设计错误变得越来越无法忍受。因此可以减少错误或降低修复成本的设计方法迅速发展起来。 ● 软硬件整合——所有的嵌入式系统中都有大量的软件和固件程序,一般来说,整合软件只能放在系统开发的最后,并且往往被认为是拖累开发进度的罪魁祸首。 ● 标准变化与灵活性——通信协议的标准正在迅速变化中。为了充分利用有限的频带资源,协议设计者们提出了很多创新性的协议标准,如IPv6、 G.729、JPEG2000、MPEG4和AES等。这些新标准需要的计算性能比以前的标准要高得多。 指令集固定且固件可编程的通用嵌入式处理器仍然非常具有吸引力,因为它们可以处理很多任务,但通常这类处理器缺乏复杂数据处理的能力,如网络应用中的包处理,视频以及加密应用中的数据处理等。为了满足类似的性能需求,芯片设计者不得不回过头来求助于RTL硬逻辑。随着设计复杂度和运算性能的不断提高,设计的规模也在不断增大,SoC设计人员需要有更多的资源才能完成芯片设计。同时,他们还面临着以下两个挑战: ● SoC设计者如何保证芯片的规格真正符合客户的需要。 ● SoC设计者如何保证芯片符合当初的设计规格。 在SoC设计中使用微处理器 解决上面两个问题的办法是赋予SoC设计足够的灵活性,从而使一颗芯片能够应用于10个、100个甚至 1000个不同的系统设计,这种需求推动了通用SoC设计的出现,从而分摊了大量芯片设计的成本。大多数的嵌入式系统都需要高速处理外部复杂的实时数据,通用微处理器需要运行在极高的频率上才能满足这些数据处理任务的要求。在个人电脑市场上正是如此,价值数百美元的PC处理器消耗几十瓦的功耗来完成用户任务。但是对于嵌入式应用来说,昂贵且耗电的芯片是没有市场的,于是设计者们转而使用RTL硬逻辑来执行高速数据处理任务。过去10年中,在逻辑综合等 ASIC设计工具的帮助下,RTL硬逻辑得到了广泛使用,这种方法已经被证明能够合理且有效的并行完成高速数据处理任务,其性能可以达到通用微处理器性能的几十甚至上百倍。与基于RTL的设计类似,可扩展处理器技术针对特殊应用定制的高速逻辑模块也需要使用逻辑综合工具。不同之处在于,RTL设计中的状态机只能通过硬件控制,而可扩展处理器中逻辑模块的状态则可以通过软件控制,这就大大提高了设计的灵活性。  图1 Xtensa可配置处理器模块图 可扩展处理器的优势 完整的可配置与可扩展处理器技术包括了处理器本身以及相应的设计工具和软件开发环境,从而使设计者通过改变或增减功能模块,设计出与特定的应用需求相匹配的处理器。典型的配置方法包括对存储器的增减修改,外部总线宽度及握手协议的设置以及常用的处理器外设的配置。除此之外,还可以对处理器进行扩展——SoC设计者可以扩展处理器的功能,特别是其指令集——为基本处理器增加原设计者从未想到过的功能。配置处理器的概念是通过参数来选择或裁剪处理器的功能,配置后的处理器可以通过多种方式硬件实现,包括耗费数周时间的ASIC方式或仅需几分钟的FPGA方式。扩展处理器的概念是设计人员为处理器增加原设计者从未考虑到的功能,是可配置处理器的一个超集。对于可配置与可扩展处理器来说,在提供处理器硬件实现的同时,还必须能够自动生成相应的软件开发环境。没有编译器,汇编器,仿真器,调试器,实时操作系统以及其他软件工具的支持,可配置与扩展处理器所提供的高性能与灵活性也就无从谈起,因为只有让软件人员能够方便的编程,才能将处理器的性能与灵活性发挥出来。 以Tensilica的可配置与可扩展处理器Xtensa为例,其模块图如图1所示。它包括了基本指令集架构、通用寄存器文件、存储器接口、可选的处理器外设、DSP协处理器以及集成用户定制指令的机制。 处理器的可扩展能力可以看做可配置的高级形式,因为它的应用更为广泛。系统设计者和应用专家可以直接探索应用的性能需求以及什么样的处理器架构和指令集才能满足这样的需求。 微处理器的应用将SoC设计与板级设计区分开来 RTL硬逻辑有许多优势——面积小、功耗低、性能强大。但是在大规模的SoC设计中,采用 RTL硬逻辑的不利因素(设计周期长、验证困难、不够灵活)正在逐渐大过其优势。而保留了大多数RTL硬逻辑的优点,又能够缩短开发时间并降低风险的设计方法正在流行起来,这就是针对特殊应用进行优化以取代复杂RTL设计的可配置处理器。 针对应用进行优化的处理器与相应的RTL设计拥有相近的数据通路,它在基本处理器核的流水线上增加额外的运算单元,新的寄存器或寄存器文件以及芯片架构师定义的其他功能模块来实现特定的应用。 在 Xtensa处理器中,这些扩展功能是利用一种名为TIE语言的类Verilog语言来描述的。TIE语言经过优化,适用于描述数据处理指令的功能并对其进行编码。用TIE语言来进行描述比RTL要简洁得多,因为它去掉了所有时序逻辑,包括状态机描述、流水线寄存器以及初始化顺序。对于固件程序员来说,处理器中用TIE语言扩展的新指令和寄存器都可以通过编译器和汇编器来进行调用。利用处理器中取指、译码、执行的流水线机制,通过C或C++高级语言编程,可以由固件程序来控制处理器数据通路上的操作。用来替代RTL模块的可扩展处理器与传统的RTL设计在结构上大同小异:更深的流水线、并行的执行单元、特殊的状态寄存器、比片内外存储器间更宽的数据接口等。这些扩展后的处理器保留了原来RTL设计强大的运算能力和数据接口格式。 可扩展处理器对数据通路的控制机制则与RTL设计中依靠硬件状态机切换状态大为不同。实际上,操作的顺序完全由处理器上运行的固件程序控制,如图2所示。用跳转指令来实现控制操作,load/store指令来实现内存操作,通用和专用计算指令来实现数据运算操作。  图2 可编程的功能模块:数据通路+处理器+软件程序 移动电话领域中的Viterbi解码的例子可以很好地说明可扩展处理器可以替代RTL硬逻辑。 GSM标准利用Viterbi解码将信息从包含噪声的信道中提取出来。解码过程中会用到包括8次逻辑计算(4次加法、2次比较、2次选择)的蝶形运算,从接收到的数据流中每解码一个符号需要 8次蝶形运算。如果采用通用RISC处理器,需要50~80个指令周期完成一次Viterbi蝶形运算,即使在TI高端的超长指令字DSP 320C64xx上,也需要1.75个周期。  图3 Viterbi蝶形算法硬件模块 利用TIE语言,设计者可以为Xtensa处理器增加一条专门完成Viterbi蝶形运算的指令,使用处理器的128位宽I/O总线一次取 8个符号数据,如图3所示为处理器添加运算单元和地址产生逻辑,这样完成一次Viterbi蝶形运算只需要0.16个周期。在未扩展的Xtensa处理器上执行Viterbi蝶形运算需要42个周期,也就是说,通过增加蝶形运算的专用硬件(大约11000门电路),就获得了250倍的性能提升。 结论 如今,软件模块硬逻辑化的现象非常普遍。在开发协议标准的早期,通常采用基于处理器的实现方法,一些常见的标准,如视频领域的 MPEG2算法,3G通信领域的W-CDMA算法、安全加密领域的SSL和triple-DES算法,都是由处理器实现逐渐过渡到RTL硬逻辑实现。但是这种过渡正在被软硬件实现方法间巨大的性能与设计难度差别所限制。可配置与可扩展处理器的出现带来了一种新的设计方法,既可以方便快速的进行芯片开发,灵活适应新的协议标准,又具有足够小的芯片面积和功耗,从而可以进行大规模的生产。 |

网友评论