»щУЪVHDLµДНјПсґ«ёРЖчTCD1206µДЗэ¶ЇЙијЖ

·ўІјК±јдЈє2010-8-19 17:28

·ўІјХЯЈєlavida

|

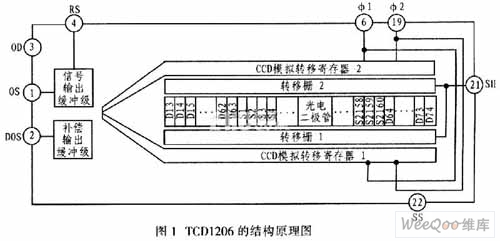

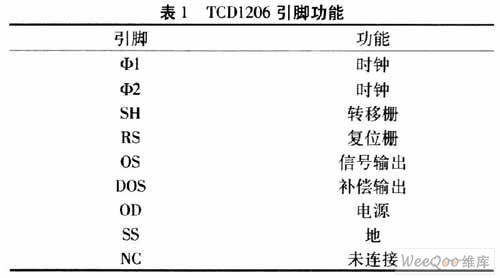

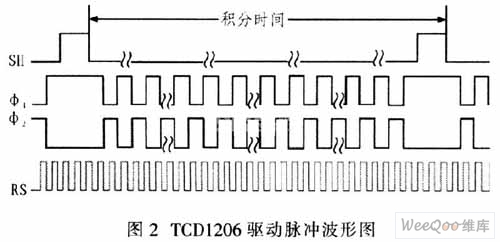

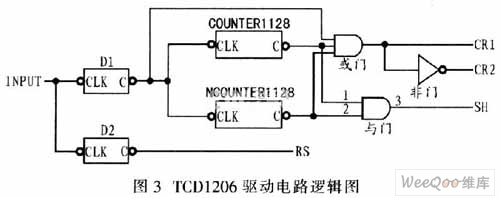

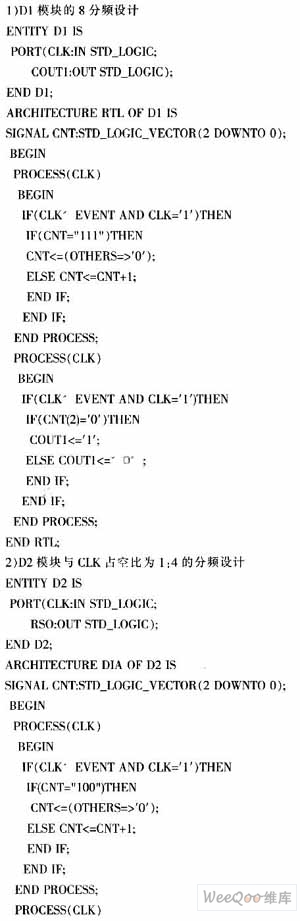

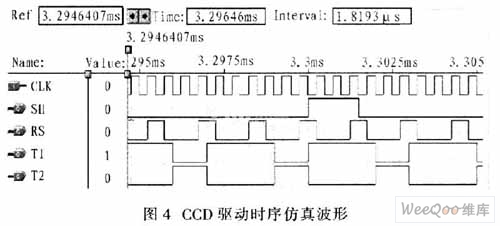

µзєЙсоєПЖчјюCCD(Charge Couple Device)КЗјЇ№вµзЧЄ»»ЎўµзєЙґўґжЎўµзєЙЧЄТЖОЄТ»МеµДРВРН№вµзґ«ёРЖчјюЎЈёГЖчјюµДЦчТЄ№¦ДЬКЗЅ«№вС§НјПсЧЄ»»ОЄµзРЕєЕЎЈµ±¶ФЖдК©јУМШ¶ЁК±РтВціеК±Ј¬ЖдґжґўµзєЙДЬФЪCCDДЪЧч¶ЁПтТЖ¶ЇЈ¬ґУ¶шКµПЦЧФЙЁГиЈ®КдіцµзС№РЕєЕµДґуРЎУлCCDµҐФЄґжґўµДµзєЙ¶аЙЩіЙХэ±ИЈ¬CCDµҐФЄґжґўµзєЙ¶аЙЩУл№вµДЗї¶ИєНCCDµҐФЄ№в»э·ЦК±јдіЙХэ±ИЎЈУлґ«НіµД№вµзґ«ёРЖчПа±ИЈ¬CCDНјПсґ«ёРЖчѕЯУРКдіцФлЙщРЎЈ¬¶ЇМ¬·¶О§ґуЈ¬№вЖЧПмУ¦·¶О§їнЈ¬·Ц±жВКёЯЈ¬КдіцРЕєЕПЯРФ¶ИєГЈ¬№¦єДµНЈ¬Ме»эРЎЈ¬КЩГьі¤µИУЕµгЎЈ¶шCCDУ¦УГµД№ШјьѕНКЗ»сИЎЗэ¶ЇВціеЈ¬ХвАп·ЦОцПЯХуCCD-TCD1206µД№¤ЧчФАнєН¶ФЗэ¶ЇК±РтµДТЄЗуЈ¬ФЪґЛ»щґЎЙПЙијЖєПАнµДВціеІъЙъ·Ѕ°ёЎЈёГЙијЖІЙУГёґФУїЙ±аіМВЯјЖчјюCPLDЧчОЄУІјюЙијЖЖЅМЁЈ¬НЁ№эі¬ёЯЛЩУІјюГиКцУпСФVHDLГиКцЗэ¶Ї·Ѕ°ёЈ¬ІЙУГAltera№«ЛѕµД·ВХжИнјюQUARTUS II¶ФЖдЗэ¶ЇВціеЅшРР·ВХжЎЈ 1 TCD1206µДЦчТЄМШµг TCD1206КЗТ»їоёЯБйГф¶ИЎўµН°µµзБчЎў2 160ПсФЄµДЛ«№µµАПЯХуCCDНјПсґ«ёРЖчЎЈУЙ2 236ёцPNЅб№вµз¶юј«№Ь№№іЙ№вГфФЄХуБРЈ¬ЖдЦРЗ°64ёцєНєу12ёцКЗУГЧч°µµзБчјмІв¶ш±»ХЪ±ОµДЈ¬ЦРјд2 160ёц№вµз¶юј«№ЬКЗЖШ№вПсГфµҐФЄЈ¬Гїёц№вГфµҐФЄµДіЯґзОЄі¤14¦МmЎўёЯ14¦МmЈ¬ЦРРДѕаТаОЄ14¦МmЎЈ№вГфФЄХуБРЧЬі¤ОЄ30Ј®24 mmЎЈ TCD1206µДЦчТЄМШРФУРЈє1)№вГфПсФЄКэОЄ2 160ПсФЄЈ»2)ПсГфµҐФЄОЄЈє14¦Мmxl 414¦Мm(ПаБЪПсФЄЦРРДѕаОЄ14¦Мm)Ј»3)№вЖЧ·¶О§ОЄ250Ў«l 100 nmЈє4)№вГфЗшУтІЙУГёЯБйГф¶ИPNЅбЧчОЄ№вГфµҐФЄЈ»5)К±ЦУОЄ¶юПа(5 V)Ј»6)ДЪІїµзВ·°ьє¬ІЙСщ±ЈіЦµзВ·Ј¬КдіцФ¤·ЕґуµзВ·Ј»7)ІЙУГ22ТэЅЕDIP·вЧ°ЎЈ 2 TCD1206µДЅб№№ФАнєНТэЅЕ№¦ДЬ 2Ј®1Ѕб№№ФАн TCD1206КЗ¶юПаµзј«µДЛ«№µµАПЯРНCCDЈ¬ЖдЅб№№ФАнИзНј1ЛщКѕЎЈЦРјдТ»ЕЕКЗУЙ¶аёц№вГф¶юј«№Ь№№іЙµД№вГфХуБРЈ¬УРР§µҐФЄОЄ2 160О»Ј¬ЖдЧчУГКЗЅУКХХХЙдµЅCCD№иЖ¬µД№вЈ¬ІўЅ«ЖдЧЄ»ЇіЙµзєЙРЕєЕЈ¬№вГфФЄБЅІаКЗґжґўЖдµзєЙµДMOSµзИЭБРТ»ґжґўХ¤ЎЈMOSµзИЭБРБЅІаКЗЧЄТЖХ¤µзј«SHЎЈЧЄТЖХ¤µДБЅІаОЄCCDДЈДвТЖО»јДґжЖчЈ¬ЖдКдіцІї·ЦУЙРЕєЕКдіцµҐФЄєНІ№іҐµҐФЄ№№іЙЎЈ  2Ј®2ТэЅЕ№¦ДЬ TCD1206ЖчјюІЙУГDIP·вЧ°Ј¬ёчТэЅЕ№¦ДЬИз±н1ЛщКѕЎЈ  3 Зэ¶ЇК±Ртј°Зэ¶ЇЙијЖ 3Ј®1Зэ¶ЇК±Рт·ЦОц TCD1206ФЪНј2ЛщКѕµДЗэ¶ЇВціеЧчУГПВ№¤ЧчЎЈµ±SHВціеёЯµзЖЅµЅАґК±Ј¬¦Х1ВціеОЄёЯµзЖЅЈ¬ЖдПВРОіЙЙоКЖЪеЈ¬Н¬К±SHµДёЯµзЖЅК№¦Х1µзј«ПВµДЙоКЖЪеУлMOSµзИЭґжґўКЖЪе№µНЁЎЈMOSµзИЭЦРµДРЕєЕµзєЙ°ьНЁ№эЧЄТЖХ¤ЧЄТЖµЅДЈДвТЖО»јДґжЖчµД¦Х1µзј«ПВµДКЖЪеЦРЎЈµ±¦ХSHУЙёЯ±дµНК±Ј¬¦ХSHµНµзЖЅРОіЙµДЗіКЖЪеЅ«ґжґўХ¤ПВµДКЖЪеУл¦Х1µзј«ПВµДКЖЪеёфАлїЄЎЈґжґўХ¤КЖЪеЅшИл№в»э·ЦЧґМ¬Ј¬¶шДЈДвТЖО»јДґжЖчЅ«ФЪ¦Х1Ул¦Х2ВціеµДЧчУГПВЗэК№ЧЄТЖµЅ¦Х1µзј«ПВµДКЖЪеЦРµДРЕєЕµзєЙПтЧуЧЄТЖЈ¬ІўѕКдіцµзВ·УЙOSµзј«КдіцЎЈDOS¶ЛКдіцІ№іҐРЕєЕЎЈ  УЙУЪЅб№№ЙПµД°ІЕЕЈ¬OS¶ЛКЧПИКдіц 13ёцРйЙ赥ԪРЕєЕЈ¬ФЩКдіц51ёц°µРЕєЕЈ¬И»єуІЕБ¬РшКдіцSlµЅS2160µДУРР§ПсЛШµҐФЄРЕєЕЎЈµЪS2160РЕєЕКдіцєуЈ¬УЦКдіц9ёц°µРЕєЕЈ¬ФЩКдіц2ёцЖжЕјјмІвРЕєЕЈ¬ТФєуКЗїХЗэ¶ЇЎЈїХЗэ¶ЇµДКэДїїЙТФКЗИОТвµДЎЈУЙУЪёГЖчјюКЗБЅБРІўРР·ЦЖжЕјґ«КдµДЈ¬ЛщТФФЪТ»ёцSHЦЬЖЪЦРЦБЙЩТЄУР1 118ёц¦Х1ВціеЎЈRSОЄёґО»ј¶µДёґО»ВціеЈ¬ёґО»Т»ґОКдіцТ»ёцРЕєЕЎЈ 3Ј®2Зэ¶ЇµзВ·ЙијЖ Зэ¶ЇµзВ·µДЧчУГКЗёшCCDМṩХэіЈ№¤ЧчЛщРиТЄµДВЯјК±РтВціеєНЖ«ЦГ№¤ЧчµзС№Ј®ІўФЪCCDµДКдіц¶Л°С№вµзЧЄ»»µГµЅµДµзєЙБїЧЄ±діЙµзС№БїКдіцЎЈЗэ¶ЇВціеРЕєЕµДІЁРОЎўПаО»ЎўЗ°єуСШК±јдµИ¶ФЖчјю№¤ЧчУРєЬґуУ°ПмЎЈ ОЄБЛ±ЈЦ¤CCD№¤ЧчОИ¶ЁїЙїїЈ®±ШРлЙијЖ·ыєПCCDХэіЈ№¤ЧчТЄЗуµДК±РтВціеєНЗэ¶ЇїШЦЖµзВ·Ј¬Зэ¶ЇїШЦЖВціеУлCCDБјєГЕдєПЈ¬ІЕДЬід·Ц·ў»УCCDµД№вµзЧЄ»»ЎўµзєЙґжґўєНµзєЙЧЄТЖµИ№¦ДЬЎЈІ»Н¬РНєЕµДCCDТЄЗуµД№¤ЧчІОКэІ»Н¬Ј¬єЬДСЙијЖТ»ЦЦЗэ¶ЇїШЦЖµзВ·Н¬К±ВъЧг¶аЦЦCCD№¤ЧчРиТЄЈ¬јґК№КЗПаН¬ПсФЄКэµДCCDЖчјюЈ¬ИфРНєЕІ»Н¬ТІІ»ѕЯУР»Ґ»»РФЎЈ TCD1206ґ«ёРЖчµДЗэ¶ЇВціе¶јОЄЦЬЖЪРФ·ЅІЁЈ¬µ«ЦЬЖЪєНХјїХ±ИІ»Н¬ЎЈЖд4В·Зэ¶ЇВціеЦ®јдРиТЄВъЧгМШ¶ЁµДК±Рт№ШПµЈєёщѕЭЗэ¶ЇВціеК±РтНјїЙЦЄФЪ1ёцSHЦЬЖЪЦРЦБЙЩУРl 118ёц¦Х1ВціеЎЈјґTSH>l 118T1Ј¬T1ОЄЗэ¶ЇВціе¦Х1µДЦЬЖЪЎЈХвАпСЎФсTSH=1 128T1ЎЈФЪSHОЄёЯµзЖЅЖЪјдЈ¬ТЄЗу¦Х1lУл¦Х2УРТ»ёцґуУЪSH=1іЦРшК±јдµДїнВціеЈ¬ХвКЗУЙУЪґЛК±ПсФЄЦРµДµзєЙХэФЪПтБЅБРјДґжЖчЦРЧЄТЖЈ¬Из№ыФЪґЛЖЪјд¦Х1Ул¦Х2УРЙПЙэ»тПВЅµСШіцПЦЈ¬Фт»бФміЙµзєЙЧЄТЖІ»НкИ«µДЗйїцЎЈК±ЦУВціе¦Х1Ј¬¦Х2ЖµВКµДЧоґуЦµКЗl MHzЈ¬µдРНЦµКЗ0Ј®5 MHzЎЈёґО»ВціеRSЖµВКµДЧоґуЦµКЗ2 MHzЈ¬µдРНЦµКЗ1 MHzЎЈ±ѕЙијЖЦР¶јСЎУГµдРНЦµЎЈ¶шЗТ¦Х1Ўў¦Х2±ШРл·ґПаЈ¬ХјїХ±ИlЈєlЈ»SHµДёЯµзЖЅВціеїн¶ИТЄРЎУЪ¦Х1Ј¬¦Х2Ј»RSУлCLKК±ЦУµДХјїХ±ИОЄlЈє4ЎЈ 3Ј®2Ј®1ФАнНјЙијЖ И·¶ЁSHЎў¦Х1Ўў¦Х2єНRSµДІОКэєуЈ¬ФтїЙёщѕЭЛьГЗЦ®јдµДК±Рт№ШПµЙијЖУІјюВЯјНјЈ¬ИзНј3ЛщКѕЎЈ  ±ѕЙијЖАыУГCPLDЧчОЄУІјюЙијЖЖЅМЁЈ¬ЛьѕЯУРЅПёЯµДБй»оРФЈ¬µзЧУµзВ·ЙијЖНкіЙєуЈ¬Из№ыРиРЮёДК±РтВЯјЎЈЦ»РиЦШРґCPLDДЪІїВЯјµзВ·јґїЙЎЈТтґЛЈ¬CPLD·ЗіЈККєПУГУЪЙијЖCCDЗэ¶ЇµзВ·ЎЈ ёчёцДЈїйµДЙијЖІЙУГVHDLУпСФГиКцЎЈІЙУГ4 MHzµДК±ЦУCLKЧчОЄКдИлµДК±ЦУЈ¬DlДЈїйУГУЪЅ«К±ЦУРЕєЕЅшРР8·ЦЖµЈ¬Ѕ«4 MHzµДК±ЦУЖµВК·ЦіЙ0Ј®5 MHzЎЈD2ДЈїйКЗЅ«К±ЦУЖµВК·ЦіЙl MHzЈ¬ХјїХ±ИОЄlЈє4ЎЈCOUNTERll28ДЈїйєНNCOUNTERll28ДЈїй·Ц±рКЗЙПЙэСШєНПВЅµСШјЖКэЈ¬јЖКэ·¶О§ФЪ0Ў«1128Ц®јдС»·Ј¬ФЪЗ°БЅёцК±ЦУОЄёЯµзЖЅЈ¬ЖдУаК±јд¶јОЄµНµзЖЅЎЈ µзВ·КµПЦКЗПИУГD1ДЈїйЅ«4 MHzµДК±ЦУЖµВК·ЦіЙ0Ј®5 MHzЈ¬УГ0Ј®5 MHzµДВціеЧчОЄCOUNTERll28єНNCOUNTERll28µДКдИл¶ЛЈ¬Ѕ«COUNTERll28єНNCOUNTERll28µДКдіцПаУлЈ¬КдіцЅб№ыѕНКЗSHЈ¬Ѕ«D1єНCOUNTERll28ТФј°NCOUNTERll28µДКдіцЅшРРВЯј»тЈ¬ФтµГµЅ¦Х1Ј¬ФЩЅ«¦Х1·ґПаЈ¬µГµЅ¦Х2Ј¬УЙD2ДЈїйїЙЦ±ЅУµГµЅRSЎЈ 3Ј®2Ј®2ДЈїйµзВ·µДVHDLЙијЖ ГїёцДЈїйµДVHDLЙијЖ¶ј°ьАЁИзПВІї·ЦЈє1)¶ЁТеЛщРиµДївєЇКэЈ»2)¶ЁТеКдИлЎўКдіц¶ЛїЪЈ»3)¶ФЙијЖЛщРиФ¤ЦГКэіхКј»ЇЈ»4)Па№Ш№¦ДЬµДКµПЦУпѕдЎЈCCDЗэ¶ЇіМРтЦчМеІї·ЦЙијЖИзПВЈє  4 ЙијЖЅб№ы·ВХж Нј4КЗФЪAltem№«ЛѕµДQUARTUS IIїЄ·ўПµНіЦР·ВХжµДІЁРОЈ®ґУНјЦРїЙТФїґіцЈ¬ІъЙъµД4В·Зэ¶ЇВціеНкИ«ВъЧгTCD1206ЛщРиµДК±РтВціеЈ¬ґпµЅЗэ¶ЇТЄЗуЎЈ  5 ЅбКшУп VHDLКЗТ»ЦЦЧФЙППтПВЙијЖµДУІјюГиКцУпСФЈ¬Н¬К±УЦѕЯУРёЯј¶УпСФµДМШРФЈ¬ХвК№µГУГХвЦЦУІјюГиКцУпСФЙијЖµДВЯј№¦ДЬ±ИЅПИЭТЧКµПЦЎЈН¬К±VHDLУпСФѕЯУРєЬєГµДїЙЦШУГРФєНїЙТЖЦІДЬБ¦Ј¬ДЬ№»јхЗṤЧчБїЎЈАыУГVHDLЙијЖХыёцґ«ёРЖчµДЗэ¶ЇЈ¬ІўУлУІјюФАнНјПаЅбєПЈ¬І»Н¬УЪТФНщТФµҐґїµДУІјюЙијЖКµПЦЈ¬ХвСщІ»ЅцАыУЪРЮёД¶шЗТЙијЖЦЬЖЪ¶МЎЈТтґЛЈ¬»щУЪVHDL¶ФTCD1206Зэ¶ЇµзВ·µДЙијЖКЗТ»ЦЦЅПКµУГµДЙијЖ·Ѕ°ёЎЈ |

НшУСЖАВЫ