基于FPGA的高精度时差测量系统设计

发布时间:2010-8-17 13:26

发布者:lavida

|

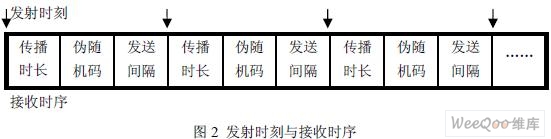

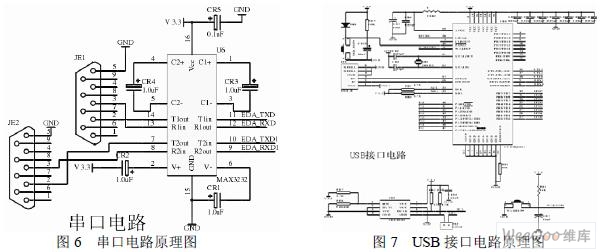

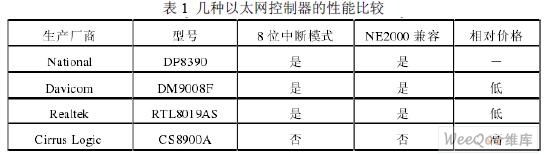

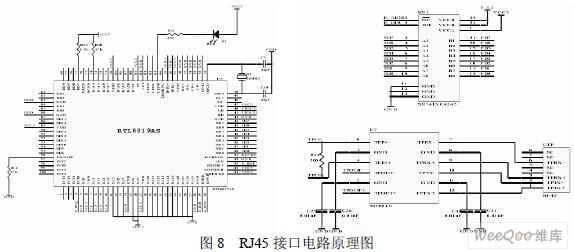

1 引言 随着无线技术的发展,无线定位系统的研究不断深入,无线定位的应用和服务也越来越 深入到生活中的每个细节,极大地改善和方便了人们的生活质量。在目前的无线定位技术中, 到达时间差定位(TDOA, Time Difference of Arrival)作为一种定位精度高、定位速度快和抗干 扰能力强的定位技术而越来越受到重视。这种定位方式的基础就是无线电测距,即通过测量 无线电信号到达某物体的传播时差,进而折算出到达此物体的距离,测距的实质正是测量时 差。由于通信设备逐步向数字化、智能化方向发展,本文充分利用了低端的FPGA 器件(Field Programmable Gate Array)的灵活性和快速性,实现提取通过不同路径的同一信号时间差。 2 总体方案设计 图 1 为总体方案设计图。基站接收机把解扩解调后的基带信号通过输入接口进入时差测 算单元,运算得到的结果通过输出接口连接到无线传输设备。为了适应各种不同接口的接收 机和无线传输设备,本系统设计了3 种常用的接口以备选择。  由于m 序列具有优良的周期自相关特性,因此经常利用它作为无线定位的测量信号。 m 序列码长越长,抗多径干扰能力越强;码速率越高,定位精度越高。时差测量单元中事先 存储了和发射端完全相同的m 序列,与接收到的m 序列进行比对。发射时刻与接收时序的 关系如图2 所示,相邻传播时长之差即为所测时差,目前该系统只能测算出不同路径的传播 时长,而差值则需要把每个传播时长传回到数据处理中心后通过软件计算得到。  本系统采用Altera 公司Cyclone 系列的EP1C3T144 芯片。它是一款基于1.5V(内核), 3.3V(I/O),0.13um 和SRAM 的FPGA,容量为2910 个LE,拥有13 个M4K RAM(4K 位+ 奇偶校验)块。除此之外,还提供了全功能的锁相环(PLL),用于板级的时钟网络管理和专用 I/O 口,这些接口用于连接业界标准的外部存储器器件,具有成本低和方便的特点。 3 时差测算单元设计 3.1 设计思想 FPGA 作为时差测算单元的核心器件,主要完成相关匹配、并/串转换、接口控制等功 能,经过VHDL 编程生成的内部结构和各个模块综合以后的整体结构如图3 所示。  其中,hxg 模块通过互相关的方法测算出不同路径的传播时长,采用8 位并行输出; serial_converter 模块把hxg 模块的结果转换成串行输出;load 模块作为serial_converter 模块 的使能输入,当load 有效时并行数据被存储到移位寄存器中。程序流程图如图4 所示。  3.2 实现结果 以 5 级的m 序列为例,反馈系数为45(八进制),初始状态为10000,得到31 位的m 序 列为1000010010110011111000110111010。码速率为1Mbps,固定发送间隔为100000 码元, 即100ms,总共发射4 组m 序列,因此参考图2 可知能够测得3 个传播时长。下图中的并行输出结果均用十进制显示。整体结果和局部放大结果如图5 所示,仿真结果表明并行结果 与串行结果完全一致。  4 主要接口设计 4.1 RS232 串口 由于本系统有两个串口,所以采用MAX3232 芯片可以简化电路[2-3]。MAX3232 是 MAXIM 公司的一种RS232 接口芯片,使用单一电源电压VCC,电压值从+3.0"+5.5V 都能 正常工作,额定电流为300μA,完成TTL 与RS232 两种电平之间的转换。它有两路收发器, 数据传输速率为250Kbps。原理图如图6 所示。  4.2 USB 接口 原理图如图7 所示,采用CY7C68013A 作为USB 接口芯片,此芯片具有以下优点: 1) 高性价比,通用USB2.0 接口芯片中全世界市场占有量最大,国外市场占用率最大。 2) 最大4K USB 端点缓冲区,可设置为双缓冲,三缓冲或四缓冲,全面支持USB2.0 高 速传输。 3) 内嵌增强型8051 内核,沿用传统8051 开发方法,固件开发工具为KEIL C51。 4) 时钟高达48MHz,单指令周期为83.3ns。 5) 双串口USART0 和USART1,支持230K 波特率。 6) 400K 高速I2C 接口。 7) 支持双数据指针。 8) 8KB 片内RAM,可存放数据和代码。 9) 五个复用数据端口PORTA,PORTB,PORTC,PORTD,PORTE。 10) 五个外部中断源。 11) 支持在线仿真和在线下载。 12) 端点缓冲区“FIFO”支持GPIF 和SLAVE FIFO 传输方式,实现端点FIFO 和外设“无 缝连接”,支持8 位/16 位总线。 13) 扩展接口IO CY7C68013A 是CY7C68013 的升级版本,完全兼容,CY7C68013 发 热量较大,CY7C68013A 为低功耗型,大容量16KB 片内RAM。  4.3 RJ45 接口 以太网的物理层有多种标准,这里使用10Base-T 标准,即数据通信速率为10Mb/s,传 输介质为双绞线。下表列出了目前市面上几种可供选择的以太网控制器及其主要特性。本系 统选择性价比较高且符合设计要求的RTL8019AS 作为以太网控制器,原理图如图8 所示。  RTL8019AS 是台湾Realtek 公司生产的10Mbps 以太网控制器,兼容Ethernet II 与IEEE 802.3;支持8 位或16 位数据总线;内置的16K 字节SRAM 用于收发缓冲;全双工,收发 可同时达到10Mbps;支持10Base-5、10Base-2、10Base-T,并能自动检测连接的介质,由 于其优良的性能、低廉的价格,使其在市场上10Mbps 网卡中占有相当的比例。 5 结束语 本系统充分利用了扩频测距原理和FPGA 的实时处理特性,具有定位精度高、扩展性强、 兼容性好等优点,通过对时差的测量,可以确定物体的运动轨迹,进而实现精确定位,同时 为飞行体的轨道测量提供基础技术,在高速落体目标测量方面具有很好的应用前景。 |

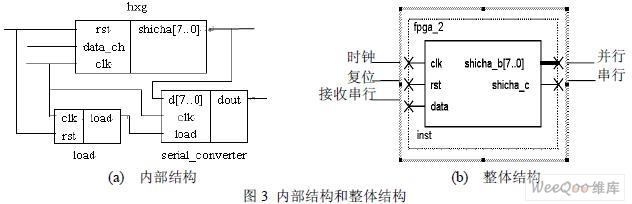

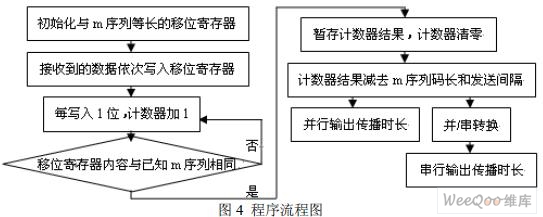

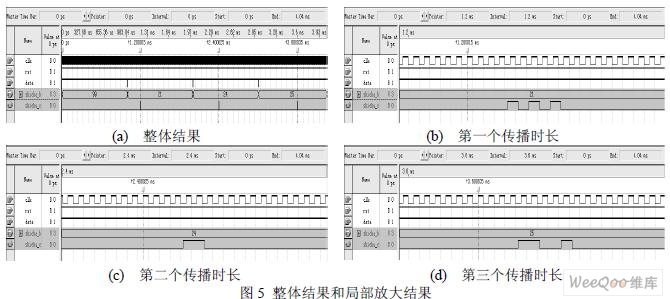

网友评论