ЛљгкLFSRгХЛЏЕФBISTЕЭЙІКФЩшМЦ

ЗЂВМЪБМфЃК2010-8-12 13:50

ЗЂВМепЃКlavida

|

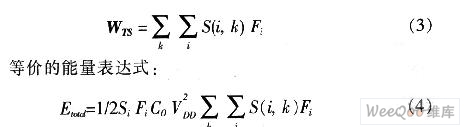

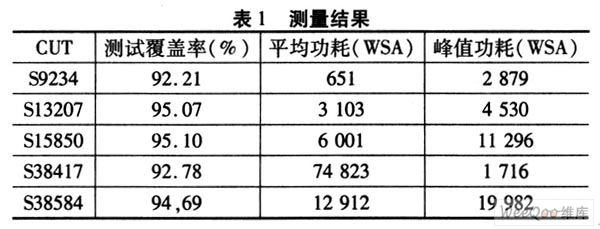

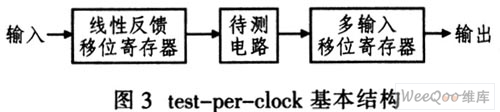

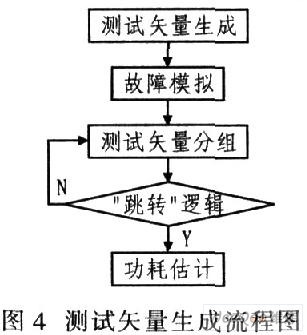

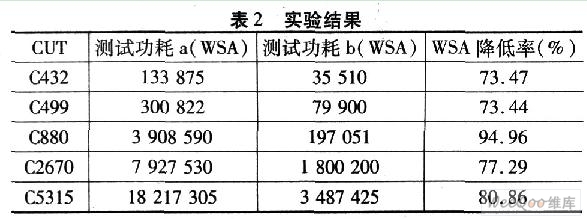

в§бд ЫцзХБуаЏЪНЩшБИКЭЮоЯпЭЈбЖЯЕЭГдкЯжЪЕЩњЛюжадНРДдНЙуЗКЕФЪЙгУЃЌПЩВтадЩшМЦ(DFT)ЕФЙІКФЮЪЬтв§Ц№СЫVLSIЩшМЦепдНРДдНЖрЕФЙизЂЁЃвђЮЊдкВтЪдФЃЪНЯТЕчТЗЕФЙІКФвЊдЖдЖИпгке§ГЃФЃЪНЃЌБиНЋДјРДШчЕчГиЪйУќЁЂаОЦЌЗтзАЁЂПЩППадЕШвЛЯЕСаЮЪЬтЁЃЫцзХМЏГЩЕчТЗЕФЗЂеЙЃЌФкНЈздВтЪд(BIST)вђЮЊОпБИСЫжюЖргХдНадФм(ШчНЕЕЭВтЪдЖдздЖЏВтЪдЩшБИдкадФмКЭГЩБОЩЯЕФвЊЧѓЁЂПЩвдНјааAtЁЊspeedВтЪдМАгажњгкБЃIPКЫЕФжЊЪЖВњШЈЕШ)ЃЌвбГЩЮЊНтОіSoCВтЪдЮЪЬтЕФЪзбЁПЩВтадЩшМЦЪжЖЮЁЃ дкBISTжаГЃгУЯпадЗДРЁвЦЮЛМФДцЦї(LFSR)зїЮЊВтЪдФЃЪНЩњГЩЦї(TPG)ЁЃLFSRБиаыВњЩњКмГЄЕФВтЪдЪИСПМЏВХФмТњзуЙЪеЯИВИЧТЪЕФвЊЧѓЃЌЕЋетаЉЪИСПЯћКФСЫДѓСПЕФЙІТЪЁЃ СэЭтЃЌдкЯЕЭГЙЄзїФЃЪНЯТЃЌгІгУгкИјЖЈЕчТЗЕФСЌајЙІФмЪфШыЪИСПОпгаживЊЕФЯрЙиадЃЌЖјгЩLFSRВњЩњЕФСЌајВтЪдФЃЪНжЎМфЕФЯрЙиадКмЕЭЁЃвђДЫЃЌдкздВтЪдЦкМфЛсдіМгЕчТЗжаНкЕуЕФЗзЊЛюЖЏЃЌЕМжТЙІКФдіДѓЁЃ 2 ЙІКФЗжЮіКЭWSAФЃаЭ CMOSЕчТЗ*КФЕФРДдДжївЊЗжЮЊОВЬЌЙІКФКЭЖЏЬЌЙІКФСНжжЁЃТЉЕчСїЛђДгЕчдДЙЉИјжаГжајСїГіЕФЦфЫќЕчСїЕМжТОВЬЌЙІКФЁЃЖЏЬЌЙІКФдђЪЧвђЮЊЖЬТЗЕчСїКЭИКдиЕчШнЕФГфЗХЕчЃЌДгЖјгЩЕчТЗе§ГЃЙЄзїЪБЕФЙІФмЬјБфЫљв§Ц№ЕФЃЌЫќАќРЈЙІФмЬјБфЁЂЖЬТЗЕчСїЁЂОКељУАЯеЕШЁЃЖдгкCMOSЙЄвеРДЫЕЃЌФПЧАЖЏЬЌЙІКФЪЧЕчТЗЙІКФЕФжївЊРДдДЁЃ ЖдгкНкЕуiЩЯУПДЮПЊЙиЩЯЕФЙІКФЮЊЃК  ЪНжаЃЌSiЪЧЕЅжмЦкФкЗзЊЕФДЮЪ§ЃЌFiЪЧНкЕуiЕФЩШГіЃЌC0ЪЧзюаЁЪфГіИКдиЕчШнЃЌVDDЪЧЕчдДЕчбЙЁЃ ДгЪН(1)ПДГіЃЌУХМЖЕФЙІКФЙРМЦгыSiКЭFiЕФГЫЛ§КЭНкЕуiЕФЗзЊДЮЪ§гаЙиЁЃНкЕуЕФЩШГігЩЕчТЗЭиЦЫОіЖЈЃЌЖјЫќЕФЗзЊДЮЪ§гЩТпМФЃФтЦїРДЙРМЦЁЃетИіГЫЛ§МДГЦЮЊНкЕуiЕФШЈжиЗзЊЛюЖЏ(Weighted Switching ActivityЃЌWSA)ЁЃдкВтЪдЙ§ГЬжаWSAЪЧНкЕуiЙІКФEiЕФЮЈвЛБфСПЃЌЫљвдWSAПЩзїЮЊИУНкЕуЕФЙІКФЙРМЦЁЃЖдгквЛЖдСЌајЕФЪфШыЪИСПTPk=(Vk-1ЃЌVk)ЃЌЕчТЗзмЕФWSAЮЊЃК  ЪНжаiЪЧЕчТЗжаЫљгаНкЕуЕФИіЪ§ЃЌS(iЃЌk)ЪЧгЩTPkЫљМЄРјНкЕуiЕФЗзЊДЮЪ§ЁЃ ИљОнЪН(2)ЃЌПМТЧГЄЖШЮЊLЕФВтЪдЪИСПTSзїЮЊЕчТЗЕФЪфШыЪИСПЃЌЕчТЗзмЕФWSAЮЊЃК  ИљОнвдЩЯЙІТЪКЭФмСПЯћКФЕФБэДяЪНЃЌдйИјЖЈвЛИіЕчТЗЩшМЦЮЊCMOSЕФЙЄвеКЭЙЉИјЕчдДЃЌПЩЕУвдЯТНсТлЃК (1)ЕчТЗжаНкЕуiЕФЬјБфЪ§ГЩЮЊЮЈвЛЕФгАЯьФмСПЁЂзюДѓЙІКФКЭЦНОљЙІКФЕФВЮЪ§ЁЃ (2)ВтЪджаЪБжгЕФЦЕТЪвВгАЯьзХЦНОљЙІКФКЭзюДѓЙІКФЁЃ (3)ВтЪдГЄЖШЃЌМДЪЉМгдкД§ВтЕчТЗ(CUT)ЩЯЕФВтЪдЯђСПЕФЪ§ФПвЛжЛгАЯьзмЕФФмСПЕФЯћКФЁЃ 3 LFSRгХЛЏЕФЕЭЙІКФЗНЗЈ ЭЈЙ§ЖдВтЪдЙ§ГЬЕФЙІКФЗжЮіПЩжЊЃЌбЁдёBISTЕЭЙІКФЕФЗНАИЪБЃЌвЛЗНУцПЩвдЭЈЙ§МѕЩйВтЪдађСаГЄЖШРДЪЕЯж(ЕЋИУЗНЗЈЭљЭљвдЮўЩќЙЪеЯИВИЧТЪЮЊДњМл)ЃЌСэвЛЗНУцНЕЕЭWSAжЕвВПЩЪЕЯжЯЕЭГЙІКФЕФНЕЕЭЁЃ дкBISTНсЙЙжаЃЌЯпадЗДРЁвЦЮЛМФДцЦї(LFSR)гЩгкНсЙЙЕФМђЕЅадЁЂЙцдђадЁЂЗЧГЃКУЕФЫцЛњВтЪдЪИСПЩњГЩЬиадЁЂгУРДбЙЫѕВтЪдЯьгІЪБЕФЛьЯ§ИХТЪЗЧГЃаЁЕШЬиЕуЃЌдкDFTЕФЩЈУшЛЗОГжаКмШнвзМЏГЩЃЌЫљвдЕБДгЩЈУшDFTЩшМЦЩ§МЖГЩBISTЩшМЦЪБЃЌLFSRвђЦфгВМўПЊЯњКмаЁЖјГЩЮЊBISTжагІгУзюЙуЕФЪИСПЩњГЩНсЙЙЁЃ ЛљгкLFSRгХЛЏЕФBISTНсЙЙПЩЗжЮЊtestЁЊper-вЛscanКЭtestЁЊperЁЊclockСНРрНсЙЙЁЃtestЁЊperЁЊscanММЪѕв§Ц№ЕФУцЛ§ПЊЯњНЯаЁЃЌВтЪдНсЙЙМђЕЅЃЌвзгкРЉеЙЃКЖјtestЁЊperЁЊclockдквЛИіжмЦкФкПЩЪЕЯжЪИСПЕФЩњГЩКЭЯьгІбЙЫѕЃЌФмЙЛЭъГЩПьЫйЕФВтЪдЁЃ 3ЃЎ1 ЛљгкЩЈУшЕФtestЁЊperЁЊscanЗНЪН 3ЃЎ1ЃЎ1 ЛљБОНсЙЙ testЁЊperвЛscanФкНЈздВтЪдЕФФПБъЪЧОЁПЩФмЕФНЕЕЭгВМўПЊЯњЁЃетжжНсЙЙдкУПИіЪфШыЪфГіЖЫПкДІЪЙгУLFSRгыМФДцЦїЕФзщКЯРДДњЬцLFSRЁЃЭМlЪЧtestЁЊper-scanФкНЈздВтЪдЕФЛљБОЕчТЗНсЙЙЁЃдкФкНЈздВтЪдЪИСПЯТЃЌLFSRЩњГЩВтЪдЪИСПВЂЧвЭЈЙ§ЩЈУшвЦЮЛМФДцЦї(shift register)НЋВтЪдЪИСПвЦЮЛЕНД§ВтЕчТЗ(CUT)ЕФЪфШыЖЫЃЌЭЌЪБЯьгІБЛвЦШыLFSRВЂбЙЫѕЁЃ  3ЃЎ1ЃЎ2 дРэ ШЋЩЈУшЛђВПЗжЩЈУшЩшМЦжагЩгквЦЮЛЛсВњЩњБШНЯДѓЕФЙІКФЁЃЛљгкЩЈУшЕФtestвЛper-scanЕЭЙІКФЩшМЦЗНЗЈашвЊаоИФБъзМЕФЩЈУшЩшМЦЃЌНЕЕЭзДЬЌзЊЛЛЛюЖЏТЪЁЃУЛМЦаоИФАќРЈдквЦЮЛЦкМфгУгкЦСБЮЩЈУшТЗОЖЛюЖЏЕФвЛаЉУХПиТпМЃЌвдМАЖдгУгквжжЦЫцЛњФЃЪНЕФИНМгТпМНјаазлКЯЕШЁЃ 3ЃЎ1. 3 ВПЗжЩЈУшЫуЗЈ ИљОнвдЩЯЩЈУшЩшМЦдРэЃЌдкЯћГ§ВтЪдађСажаЕФШпгрФЃЪНжЎКѓЃЌВЩгУЭМ2ЫљЪОЕФВПЗжЩЈУшЫуЗЈЖдД§ВтЕчТЗНјааВПЗжЩЈУшЩшМЦЁЃЦфВНжшШчЯТЃК  ЂйЪзЯШЩОГ§ЫљгаздЗДРЁЪБађТпМЖдгІЕФЖЅЕуЁЃ ЂкдкЪ§ОнСїЭМжаВщевЫљгаЕФЧПСЌЭЈЕЅдЊ(Strongly Connected ComponentsЃЌМђГЦSCC)ЁЃ ЂлвРДЮЩОГ§SCCЫљгаЖЅЕужазюДѓЕФЖЅЕуЁЃ ВЮПМЮФЯзВЩгУЩЯЪіЫуЗЈЖдISCA89ЛљзМЕчТЗЩЈУшBISTВтЪдЃЌВЂВЩгУATPGЙЄОпКЭЗТецЙЄОпVCSЙЪеЯФЃФтКЭЙІФмФЃФтЃЌБэ1СаГіВтЪдИВИЧТЪЁЂЦНОљЙІКФКЭЗхжЕЙІКФЪ§ОнЁЃ  гЩБэlЪ§ОнПЩМћЃЌВПЗжЩЈУшЖдД§ВтЕчТЗВтЪдИВИЧТЪгАЯьЗЧГЃаЁ(3ЃЎ2 ЛљгкЪБжгЕФtestЁЊper-clockЗНЪН 3ЃЎ2ЃЎ1 ЛљБОНсЙЙ вЛИіtest-per-clockФкНЈздВтЪдЛљБОНсЙЙШчЭМ3ЫљЪОЁЃУПвЛИіВтЪдЪБжгL2SRЩњГЩвЛИіВтЪдЪИСПЁЃЖрЪфШЫЬиеїМФДцЦї(Multiple-вЛInput Signature RegisterЃЌМђГЦMISR)бЙЫѕвЛИіЯьгІЪИСПЁЃ  3ЃЎ2ЃЎ2 дРэ дкЩЈУшВтЪджаЃЌжївЊЙІКФАќРЈТпМЙІКФЁЂЩЈУшЙІКФКЭЪБжгЙІКФЁЃЧАУцИјГіЕФЗНЗЈжївЊМЏжадкНЕЕЭТпМЙІКФЛђЩЈУшЙІКФЃЌЕЋУЛгаНЕЕЭЪБжгЙІКФЁЃЛљгкЪБжгЕФЕЭЙІКФtestЁЊperЁЊclockЗНЪНПЩвдЭЌЪБНЕЕЭет3жжЙІКФЁЃИУЗНЗЈВЩгУЕЭЙІКФЕФtestЁЊper-вЛclock BISTНсЙЙЁЃЖдLFSRНјаааоИФКѓЃЌгУзїTPGвдЩњГЩЕЭЙІКФЕФВтЪдЪИСПЁЃЪЙгУетжжОЙ§аоИФЕФЪБжгЗНАИЛсНЕЕЭБЛВтЕчТЗЁЂTPGКЭРЁИјTPGЕФЪБжгЪїЕФЬјБфУмЖШЁЃЭЈЙ§НЕЕЭБЛВтЕчТЗЁЂTPGКЭЪБжгЪїЕФзДЬЌзЊЛЛЛюЖЏТЪРДНЕЕЭBISTЦкМфЕФЙІКФЁЃ гЩгкРДдДгкБъзМЩЈУшНсЙЙЕФВтЪдФЃЪНПЩжБНггУгкЕЭЙІКФЩЈУшНсЙЙЃЌетжжЗНЗЈгыВЩгУДЋЭГЩЈУшНсЙЙЫљДяЕНЕФЙЪеЯИВИЧТЪКЭICВтЪдЪБМфЛљБОвЛжТЁЃгыДЋЭГЩЈУшНсЙЙЯрБШЃЌУцЛ§ПЊЯњКмаЁЃЌдкЕчТЗадФмЗНУцвВУЛгаЫ№ЪЇЁЃ 3ЃЎ2ЃЎ3 ЕЭЙІКФВтЪдЪИСПЩњГЩ ЖдгкtestЁЊperЁЊclockНсЙЙРДЫЕЃЌМѕЩйВтЪдЙІКФжївЊЭЈЙ§гХЛЏВтЪдЪИСПРДЪЕЯжЃЌЖјВтЪдЪИСПЩњГЩММЪѕЪЧжИВњЩњШЗЖЈадВтЪдЪИСПЕФММЪѕЁЃ ВтЪдЪИСПЩњГЩЗНЪНдкЩњГЩВтЪдФЃЪНЪБЃЌГ§СЫвЊДяЕНДЋЭГЕФATPGФПЕФЃЌЛЙашПМТЧНЕЕЭВтЪдЦкМфЕФЙІКФЁЃЛљгкATPGЕФЗНЗЈгжЗжЮЊ2жжЃКЂйМЏГЩЕФATPGгХЛЏЗНЗЈЃЌИУЗНЗЈЕФВтЪдФЃЪНдкВтЪдЩњГЩЦкМфНјааЕЭЙІКФгХЛЏЃЛЂкATPGжЎКѓЕФгХЛЏЗНЗЈЃЌИУЗНЗЈЕФВтЪдФЃЪНЪзЯШгЩДЋЭГЕФATPGЩњГЩЃЌШЛКѓдйНјааЙІКФгХЛЏЁЃ (1)гыФЃФтЭЫЛ№ЫуЗЈЯрНсКЯВтЪдЪИСПЩњГЩЕФВНжшЪЧЃКЪзЯШИљОнФЃФтЭЫЛ№ЫуЗЈНЋВтЪдФЃЪНЗжзщГЩШєИЩИігааЇВтЪдЪИСПзщгыЮоаЇВтЪдЪИСПзщСНВПЗжЃЛШЛКѓИљОнЫуЗЈдРэЃЌЩњГЩПижЦLFSRдЫааЕФПижЦТыЃЛдкетаЉПижЦТыЕФзїгУЯТЃЌLFSRОЭЬјЙ§ДѓСПЕФЮоаЇВтЪдЪИСПЃЌЩњГЩгЩгааЇВтЪдЪИСПЙЙГЩЕФОЋМђЕФВтЪдЪИСПађСаЁЃЦфЛљБОСїГЬШчЭМ4ЫљЪОЁЃ  (2)гыНјЛЏЫуЗЈЯрНсКЯвРОнВтЪдЪИСПЩњГЩММЪѕдРэЃЌВЩгУЛљгквХДЋЫуЗЈЕФВтЪдФЃЪНЩњГЩЦїЃЌгУгкМЦЫуШпгрЕФВтЪдФЃЪНЁЃдкШпгрВтЪдФЃЪНжаЃЌвЛИіЙЪеЯгЩМИИіВЛЭЌЕФађСаИВИЧЁЃШЛКѓЪЙгУвЛИігХЛЏЫуЗЈЃЌДгЧАУцвбМЦЫуЙ§ЕФВтЪдађСазщКЯжабЁдёвЛИізюМбзгМЏЃЌЪЙЦфЗхжЕЙІТЪзюаЁЃЌЖјВЛгАЯьЙЪеЯИВИЧТЪЁЃВЮПМЮФЯзВЩгУISCASЁЏ85BenchЁЊmarkжаЕФзщКЯЕчТЗзїЮЊЪЕбщЕчТЗЃЌдкБЃГжЙЪеЯИВИЧТЪВЛБфЕФЧщПіЯТЃЌЖдД§ВтЕчТЗЕФВтЪдЙІКФaгыЪЙгУФЃФтЭЫЛ№ЫуЗЈЕФBISTНсЙЙЕФВтЪдЙІКФbЯрБШНЯЃЌЕУЕНЕФНсЙћШчБэ2ЫљЪОЁЃ  гЩБэ2ПЩжЊЃЌТњзуЯрЭЌЙЪеЯИВИЧТЪЪБЃЌВЩгУФЃФтЭЫЛ№ЫуЗЈЗжзщВтЪдЪИСПКѓЃЌWSAДѓЗљНЕЕЭЃЌзмЕФWSAИФЩЦТЪдк73ЃЎ44ЃЅ"94ЃЎ96ЃЅжЎМфЁЃгЩгкМѕЩйВтЪдЪИСПЃЌВтЪдЪБМфвВДѓЮЊЫѕЖЬЁЃ 4 Нсгя ВЩгУЯпадЗДРЁвЦЮЛМФДцЦїЩњГЩВтЪдЪИСПЕФBISTНсЙЙПЩЗжЮЊtestЁЊperЁЊscanКЭtestЁЊperЁЊclockСНДѓРрЃЌЯргІЕФЪЕЯжЕЭЙІКФBISTВтЪдЗНЗЈвВЗжБ№еыЖдtestвЛperЁЊscanКЭtestЁЊperвЛclockНсЙЙЁЃЖдteslЁЊper-scanНсЙЙФЃЪНЃЌМѕЩйВтЪдЙІКФжївЊЭЈЙ§гХЛЏЩЈУшСДРДЪЕЯжЃЛЖдгкtestЁЊper-clockНсЙЙФЃЪНЃЌМѕЩйВтЪдЙІКФжївЊЭЈЙ§гХЛЏВтЪдЪИСПРДЪЕЯжЁЃtestЁЊperЁЊscanММЪѕв§Ц№ЕФУцЛ§ПЊЯњНЯаЁЃЌВтЪдНсЙЙМђЕЅЃЌвзгкРЉеЙЃЛЖјtestЁЊperЁЊclockдквЛИіжмЦкФкПЩЪЕЯжЪИСПЕФЩњГЩКЭЯьгІбЙЫѕЃЌФмЙЛЭъГЩПьЫйЕФВтЪдЁЃЕБШЛЃЌЫцзХВтЪдЙІКФбаОПЕФЩюШыЃЌНЋЛсгаИќКУЕФЗНЗЈЪЙЙІКФЁЂЙЪеЯИВИЧТЪЁЂЯЕЭГадФмЕШЮЪЬтДяЕНзюгХЁЃ |

ЭјгбЦРТл