ИпЫйздЖЏВтЪдЩшБИЕФЮДРД

ЗЂВМЪБМфЃК2010-8-30 21:52

ЗЂВМепЃКconniede

|

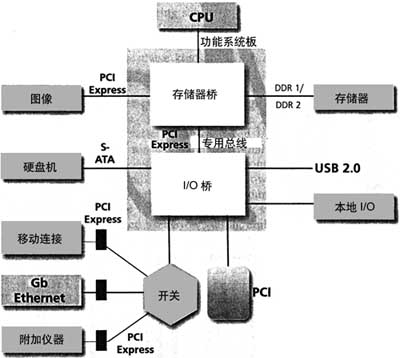

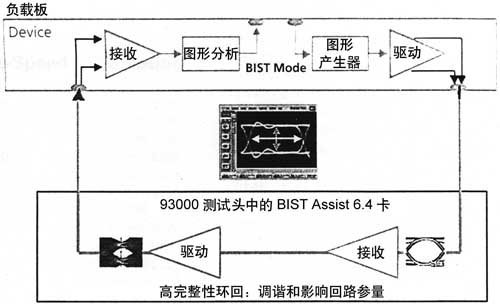

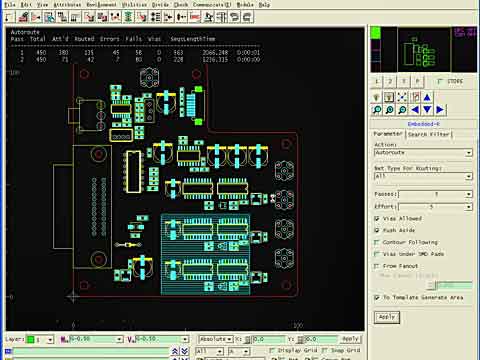

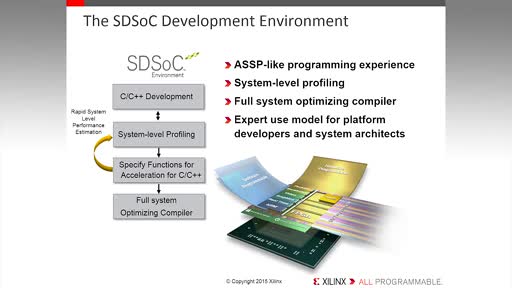

АыЕМЬхвЕе§дкж№НЅБфЛЛЕНФЩУзжЦдьЙЄвеЁЃФЩУзММЪѕДјРДОоДѓЕФКУДІЃКМИКѕПЩвдздгЩЕидіМгОЇЬхЙмЪ§ЁЃСэвЛЗНУцЃЌCMOSЙЄвевбЗЂЩњЯджјЕиБфЛЏЃЌвђДЫЃЌФЩУзSOCГіЯжаТаЭЕФжЦдьШБЯнЁЃЕквЛИіЮЪЬтЪЧдкИпЦЕЪБЛсдіМгЖЈЪБЪЇаЇЪ§ЁЃЦфЫћЮЪЬтЛЙАќРЈДЎШХЁЂЪБжгЭсаБКЭЭЌВНЁЂИпЫйI/OВЮСПЪЇаЇЃЌгЩгкЦфФЃФтЬиадЃЌЫќУЧЖдРДздЯрСкЪ§зжаОКЫЕФзЂШыдыЩљЬиБ№УєИаЁЃЮЊСЫНтОіЯрЙиЕФжЪСПКЭВтЪдГЩБОЮЪЬтЃЌе§дкбаОПаТЕФВтЪдЩшМЦЃЈDFTЃЉММЪѕКЭЦфЫћВтЪдЗНЗЈЁЃЬиБ№ЪЧACЩЈУшКЭФкзАздВтЪдЃЈBISTЃЉ/ЛЗЛиММЪѕЃЌе§дкШевцгУгкИФЩЦЦїМўИпЫйВПЗжгыЖЈЪБгаЙиЕФЪЇаЇЁЃ етаЉдіЧПНсЙЙЕФВтЪдПЊЗЂЃЌзюКѓЪЧЗёашвЊЧЇезКеЪ§ОнТЪИпЫйздЖЏВтЪдЩшБИЃЈATEЃЉЃПИпЫйATEЯЕЭГжаЕФИпЫйЙІФмКЭВЮСПВтЪдНЋРДММЪѕЩЯЪЧЗёМЬајашвЊЃПОМУЩЯЪЧЗёКЯРэЕШЮЪЬтЛсЫцжЎЖјВњЩњЁЃ ФЩУзжЦдьШБЯнМАКѓЙћ ИФБфШБЯнЬиадЕФвЛИіР§жЄЪЧДѓСПдіМггыЖЈЪБгаЙиЕФЙЪеЯЁЃетЭљЭљдкИпЦЕЕМжТЙЪеЯЃЌШчЙЬЖЈадЙЪеЯЁЃгыDCЙЪеЯБШНЯЃЌЯрЙиЕФЖЈЪБЮЪЬтжЛФмЭЈЙ§ИпЫйВтЪдРДМьВтЁЃ ЫцзХЦїМўГпДчЕФМѕаЁЃЌОЇЬхЙмЙиМќВЮСПЃЈШчеЄбѕЛЏВуКёЖШЁЂЗЇжЕЕчбЙЃЌгааЇОЇЬхЙмГЄЖШЃЌТЉЕчСїЃЉЫцжЎдіДѓОВЬЌБфТЪЁЃетЖМЛсгАЯьЖЈЪБЁЃ етдкБОжЪЩЯЛсЕМжТЦїМўМФЩњВЮСПЗЧРэЯыЖЈБъКЭЗЧРэЯыгЁЫЂАхзпЯпЕФБфТЪЁЃетаЉвђЫиЛсЪЙаОЦЌЫйЖШКЭЙІКФЕМжТДѓЕФБфЛЏЁЃ ЕчШнДЎШХаЇгІКЭRCФкСЌбгГйЛсНјвЛВНЖёЛЏаЁЙцФЃЦїМўЕФИпЫйадФмЁЃФкСЌв§Ц№ЕФДЋВЅбгГйжЇХфОЇЬхЙмеЄМЋбгГйЁЃетжжаЇгІЛсгАЯьЦїМўадФмЁЃ ЖдгкетаЉИДдгЕФФЩУзЦїМўЃЌЦфДЋЭГИпЫйЙІФмВтЪдЪЧеыЖдаХКХЭъећадЮЪЬтЃЈШчIRбЙНЕЃЌИаадИЩШХЃЌГФЕзёюКЯЃЌЕчвЦЃЉЃЌетаЉЮЪЬтВЛПЩФмгУЕчСїЗТецММЪѕеЙЪОЁЃИпЫйВтЪдвВПЩДяЕНЫљашЕФЖЈЪБЙиБеЁЃ аТФЩУзЩшМЦЕФВњЦЗжБЯпЩЯЩ§ЦкМфЃЌЕЭВњГіЭљЭљЪЧИіЮЪЬтЃЌвђЮЊШБЯнЖдгІгУБШДгЧАЕФММЪѕгаИќЧПЕФвРРЕадЁЃашвЊИќШЋУцЕФВтЪдРДДяЕНВњЦЗЦїМўЫљашЕФжЪСПЫЎЦНЁЃгыDFTФмСІвЛЦ№ЃЌИпЫйЙІФмВтЪдЮЊСЫНтаТжЦдьЙЄвеЙЬгаЕФЙЪеЯЛњЙЙЬсЙЉжївЊЕФЗДРЁЛЗТЗЁЃ SOCЩшМЦжаЕФЭЌВНЮЪЬт ЯЕЭГПэЪБжгЭЌВНЪЧДѓСПФЩУзЩшМЦЕФжївЊЮЪЬтжЎвЛЁЃЕБИпЫйЩшМЦЕФзюаЁЪБжгжмЦкМѕаЁЪБЃЌТуЦЌГпДчШдБЃГжДѓЕФЃЌетЪЧвђЮЊИќЖрдЊМўМЏГЩдкЭЌвЛТуЦЌЩЯЁЃвђДЫЃЌгыФкСЌбгГйДѓдМГЩе§БШЕФгаЙиЪБжгЭсаББфГЩЪБжгжмЦкЕФживЊВПЗжЃЌЖјЭЌВНЩшМЦжаЕФПчаОЦЌЭЈаХашвЊвЛИіЪБжгжмЦквдЩЯЪБМфЁЃ ВЩгУИДдгЕФЪБжгШЅЭсаБММЪѕРДНтОіетаЉЮЪЬтЁЃдкДѓСПЕФЩшМЦжаЃЌаТЕФЗНЗЈЃЌШчећЬхвьВНОжВПЭЌВНЃЈGALSЃЉНсЙЙе§дкЬцДњЭЈГЃЕФЖЈЪБЗНЗЈЁЃШЛЖјЃЌдкSOCЩшМЦжаВЛЭЌгђжЎМфЕФЪ§ОнДЋЪфШдШЛБиаыжиаТЭЌВНЁЃИпЫйЙІФмВтЪдПЩНтОіетРрЭЌВНЮЪЬтЃЌЕЋЦфЫћИпЫйЗНЗЈЃЈШчACЩЈУшЃЉВЛФмНтОіетРрЭЌВНЮЪЬтЁЃ ИпЫйI/OВтЪдЮЪЬт ЯждкЃЌИпадФмSOCЩшМЦАќКЌДѓСПВЛЭЌЕФИпЫйI/OзмЯпКЭавщЁЃПЩвдПДЕНВЛЭЌаХКХДЋЪфРраЭЕФЙуЗКЛьКЯЃЌДгЭЌВНЫЋЯђЕНЕЅЯђаХКХДЋЪфКЭЕЅЖЫЕНЕЭбЙВюЗжаХКХДЋЪфЁЃОпгаЗжРыЪБжгаХКХЕФДЋЭГПэЁЂВЂааЁЂдДЭЌВНзмЯпНсЙЙе§дкБЛеЁЂДЎааЁЂЧЖШыЪНЪБжгММЪѕЬцДњЁЃдкЦїМўЕФНгЪеЦїПкгУОпгаЪБжгКЭЪ§ОнЛжИДЃЈCDRЃЉЕЅдЊЕФДЎааЦї/НтДЎЦїЃЈSerDesЃЉДгЪфШыЪ§ОнСїжаЬсШЁЪБжгаХКХЁЃ PCаОЦЌзщЦїМўЪЧЛьКЯI/OРраЭЕФР§жЄЃЈЭМ1ЃЉЁЃР§ШчЃЌPCIExpressКЭS-ATAЖМгУОпгаЕЅЯђЕЭАкЗљВюЗжаХКХДЋЪфЕФЧЖШыЪНЪБжгММЪѕЁЃPCI ExpressПЩАќКЌдЫаадк2.5Gb/sЪ§ОнТЪЯТЕФ32ИіЭЈЕРЃЌЖјS-ATAдк1.5Gb/sЛђ3Gb/sжЛжЇГжвЛИіЭЈЕРЁЃ  ЭМ1 ОпгаДцДЂЦїЧХЃЈББЧХЃЉКЭI/OЧХЃЈФЯЧХЃЉЕФIntelЛљPCаОЦЌзщНсЙЙ ЯрЗДЃЌDDRДцДЂНгПкКЭIntelЕФЧАЖЫзмЯпЃЈFSBЃЉНсЙЙЯждкВЩгУЕЅЖЫЁЂЫЋЯђЁЂдДЭЌВНММЪѕЁЃЯждкFSBЕФ800Mb/sЪ§ОнТЪПЩЭћКмПьдіДѓЕН1066Mb/s,ЩѕжСПЩДяЕН1.6Gb/sЁЃ ЮЊСЫЪЪгІетжжгВМўБфЛЏКЭВЛЖЈЕФаавЕЖЈЪБЃЌашвЊгаСщЛюЕФВтЪдЩшБИЁЃашвЊМИАйИпЫйв§НХЃЌЕЋЪЧЃЌЖрЪБжггђвВЙЄзїдкВЛЙЬЖЈЕФЫйТЪЃЌвђЮЊВЛЭЌЕФНгПкБиаыЭЌЪБВтЪдЁЃ SerDesКъЕЅдЊДѓСПМЏГЩЕНЯћЗбРрSOCЦїМўжаЃЌетЛсДјРДгыI/OгаЙиЕФИДдгВтЪдЮЪЬтЃЌР§ШчЃЌгыЖЖЖЏгаЙиЕФЙубгВЮЪ§ВтЪдЁЃЖдгкИпМЏГЩSOCЦїМўЃЌетаЉВтЪдЫЦКѕЪЧИќживЊЕФЃЌвђЮЊЫќУЧДѓСПЕФаОКЫПЩФмЖдгааЇЕФЙиБеаОЦЌЪ§ОнДЋЪфгаИКУцГхЛїЁЃ ИпМЏГЩЪ§зжATEЭЈЕРБШДЋЭГЛњМмЛђЛьКЯаХКХвЧЦїИќЪЪКЯгкВЮСПВтЪдЁЃашвЊМИЧЇезКеЕФЪфШыФЃФтДјПэЁЂЕЭЕФЙЬгаЯЕЭГЖЖЖЏКЭИпЖЈЪБОЋЖШЁЃвђЮЊЫќЪЧеыЖдЫљгаетаЉВтЪдЮЪЬтЃЌЫљвдЃЌИпЫйЙІФмВтЪдЖдгкаОЦЌе§ШЗТпМКЭЕчЦјадФмЕФбщжЄШдНЋЪЧжївЊЙЄОпЁЃетЪЧИпЫйЦїМўЕїЪдКЭЬиадМјЖЈЦкМфСНИіжївЊЕФШЮЮёЁЃ ШЋЫйЖШЙІФмВтЪдКЭШЋЫйЖШDFTЙВДц ЫцзХВтЪдГЩБОЕФМЬајНЕЕЭЃЌТуЦЌЩЯВтЪдФмСІзЪдДЕФЙуЗКПЊЗЂКЭгІгУВЛЖЯЯђЧАЭЦНјЁЃЮЊСЫМьбщЯрЙиЖЈЪБМфЬтЃЌШевцВЩгУДЋЪфЙЪеЯЕФШЋЫйЖШНсЙЙВтЪдЁЂЙиМќЭЈТЗЕФЭЈТЗбгГйВтЪдКЭBIST/ЛЗЛиММЪѕЁЃ НсЙЙШЋЫйЖШЗНЗЈЕФвЛИіР§згЪЧACЩЈУшЃЌЖјEDAЙЄОпжаЖдACЩЈУшЕФжЇГжВЛЖЯИФНјЁЃШЛЖјЃЌACЩЈУшВтЪдЦкМфЕФПЊЙиЖЏзїгыЙІФмВтЪдЪЧЭъШЋВЛЭЌЕФЃЌе§ЪЧгЩгкДЫдвђЃЌетВЛПЩвдФЃФтецЪЕЕФгІгУЬѕМўЁЃвђДЫЃЌетбљЕФЗНЗЈашвЊЕФЪЕМЪЙІФмВтЪдЕФЙубгЯрЙиадЁЃЩѕжСгаСМКУЕФЯрЙиадЃЌШдШЛЛсгаЦфЫћПЩФмЕФЮЪЬтЃЌЕМжТГЩЦЗТЪЫ№ЪЇдіМгЛђВтЪдТЉЪЇЁЃ ВЛОЋШЗЕФбгГйВтЪдПЩФмЪЧГЩЦЗТЪЫ№ЪЇКЭВтЪдТЉЪЇЕФСэвЛИідвђЁЃжЛгаМИЪЎЦЄУыЕФбгГйЭЈТЗВтСПЮѓВюЯрЕБгкФкВПЪБжгжмЦкЕФ5%ЁЃжСНёВЛжЊЕРЖдбгГйЭЈТЗВтСПМгШнЯоВтЪдЕФЗНЗЈЃЌЫљвдЃЌетаЉЮѓВюПЩЕМжТГЩЦЗТЪЫ№ЪЇЛђВтЪдТЉЪЇЁЃ АбЦЌЩЯBISTНсЙЙгыДЎааЛЗЛиЗНЗЈЯрНсКЯЪЧШЋЫйЖШВњЦЗВтЪдЕФСэвЛжжСїааММЪѕЃЌЬиБ№ЪЧЖдгкSerDes I/OЕЅдЊЕФВтЪдЁЃгУзЈУХЕФATEЛЗЛиПЈЃЈШчAgilent93000 BIST Assist6.4ЃЉПЩдіЧПВтЪдЗЖЮЇЃЌГ§ЛљБОЙІФмВтЪдЭтвВжЇГжВЮСПВтСПЃЈЭМ2ЃЉЁЃ  ЭМ2 BISTЛЗЛиВтЪдЗНЗЈгызЈгУATEЛЗЛиПЈНсКЯ ОЁЙмDFTЛђЦфЫћЕЭГЩБОММЪѕЖдгкИпЫйЦїМўЕФКмЖрИпЦЕI/OЬиадЪЧзюОМУЕФВтЪдЗНАИЃЌЕЋШдШЛЖдATEгаНЯЧПЕФвЊЧѓЃЌЯЃЭћЫќФмЬсЙЉШЋЫйЖШМЄРјКЭВЖЛёЃЌЬиБ№ЪЧдкВњЦЗЖЈаЭЧАИќЪЧетбљЁЃ ЕБDFTЭъШЋШЁДњШЋЫйЖШЙІФмВтЪдЪБЃЌПЩДяЕНЕФЙЪеЯИВИЧТЪЧїгкелждЁЃетПЩФмЪЧвЛжжЧБдкЕФЗчЯеЃЌЬиБ№ЪЧЖдгкАбЙЄвеММЪѕЭЦжСМЋЯоЕФаТI/OММЪѕЖјбдЁЃСэЭтЃЌDFTШдШЛЪЧвЛжжГЩЪьЕФММЪѕЃЌЖјВЛЭЌЕФЙшЙЉгІЩЬзёбВЛЭЌЕФDFTПЊЗЂеНТдЁЃЛљгкДЫдвђЃЌШЋЫйЖШDFTВЛЪЧвЛЙсЕФПчвЕНчЪЕЯжЁЃЩѕжСдкЩњВњжаЃЌдкПЩдЄВтЕФНЋРДЃЌећИівЕНчНЋВЛЯЃЭћгУШЋЫйЖШDFTЭъШЋЬцДњШЋЫйЖШЙІФмВтЪдЁЃ ИпЫйATEЭЈЕРЕФЙиМќвЊЧѓ ЖдгкЩшМЦЬиеїЃЌATEИпЫйЧ§ЖЏКЭВЖЛёФмСІБиаыХфКЯИпЖЈЪБЕФОЋЖШЁЃЭЌЕШживЊЕФЪЧЃЌБиаыЬсЙЉЕФATEЙІФмЪЧОМУЕФЃЌвђЮЊАыЕМЬхГЇМвУцЖдОоДѓЕФГЩБОбЙСІЁЃ ИпЫйATEвЊЧѓШчЯТЃК ЁЄИпЖШСщЛюадЃКЦфФмСІАќРЈИїжжВЛЭЌЕФI/OРраЭЁЃ ЁЄЭъШЋПЩСПВтадЃКЦфФмСІАќРЈЫљашЫйЖШЕФећИіЗЖЮЇКЭЫљашЕФв§НХзЪдДЁЃЪ§ОнТЪЗЖЮЇДгМИАйезКеЕНМИЧЇезКеЃЌЫљашв§НХЪ§ИпДя2000в§НХЁЃ ЁЄИпадФмЃКИпОЋЖШКЭПьЫйЭЬЭТСПЁЃ ЁЄЖрЪБжггђжЇГжЁЃ ЁЄИКЕЃЕУЦ№ЕФГЩБОЁЃ Нсгя ВЛЙмЯждкЕФНјеЙШчКЮЃЌШЋЫйЖШНсЙЙКЭBISTЛљЛЗЛиВтЪдВЛДѓПЩФмНтОігыФЩУзжЦдьШБЯнЯрЙиЖЈЪБЕФЫљгаЮЪЬтЁЃЫцзХДѓЖрЪ§ВњЦЗЪйУќжмЦкБфЕУдНРДдНЖЬЃЌЖјМьбщКЭзюМбЛЏDFTЕчТЗДяЕНБиаыЕФЫЎЦНБфЕУИќМгРЇФбЁЃКмЖрЧщПіЯТЃЌDFTЛљММЪѕНЋгыгаЯоЪ§ЕФЙІФмШЋЫйЖШЭМаЮЙВДцЃЌетПЩЬюГфНіDFTММЪѕЕФТЉЪЇВтЪдЗЖЮЇЁЃвђДЫЃЌПЩЬсЙЉИпЫйЁЂИпУмЖШКЭИпЖШЭЈгУЕФATEНЋШдШЛЪЧЛёЕУГЩЙІАыЕМЬхжЦдьЕФЙиМќЁЃ |

ЭјгбЦРТл