ЛљгкFPGAЕФИпЫйЪ§зжЯрЙиЦїЩшМЦ

ЗЂВМЪБМфЃК2010-8-10 15:57

ЗЂВМепЃКlavida

ЙиМќДЪЃК

ЯрЙиЦї

|

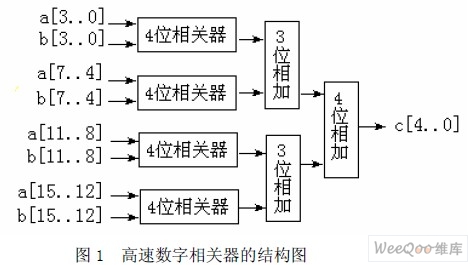

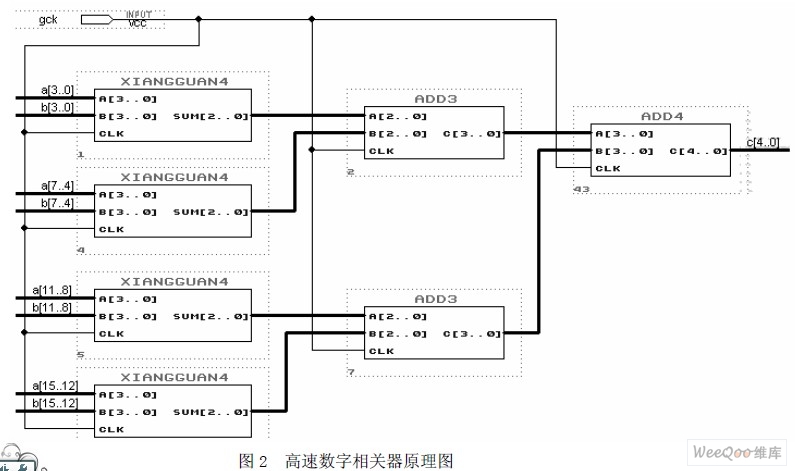

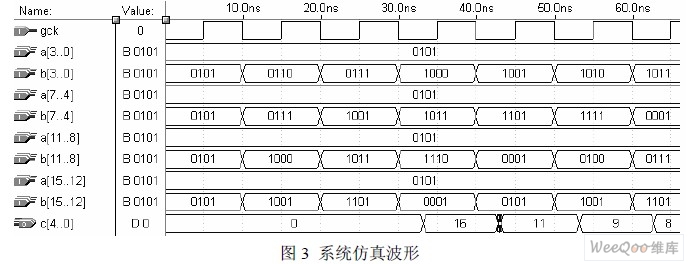

еЊвЊЃКдкЪ§зжЭЈаХЕФЪ§ОнДЋЪфЙ§ГЬжаЃЌашвЊБЃГжЪ§ОндкДЋЪфЙ§ГЬжаЕФЭЌВНЃЌвђДЫвЊдкЪ§ОнДЋЪфЙ§ГЬжаВхШыжЁЭЌВНзжНјааМьВтЃЌДгЖјгааЇБмУтЗЂЫЭЪ§ОнКЭНгЪеЪ§ОндкДЋЪфЙ§ГЬжаГіЯжЕФвьВНЮЪЬтЁЃЮФжаЬсГіСЫвЛжжВЩгУСїЫЎЯпММЪѕЁЂЛљгк FPGAЩшМЦИпЫйЪ§зжЯрЙиЦїЕФЗНЗЈЁЃЗТецНсЙћБэУїЩшМЦЗНАИЪЧПЩааЕФЁЃ дкЪ§зжЭЈаХЯЕЭГжаЃЌГЃгУвЛИіЬиЖЈЕФађСазїЮЊЪ§ОнПЊЪМЕФБъжОЃЌГЦЮЊжЁЭЌВНзжЁЃдкЪ§зжДЋЪфЕФЙ§ГЬжаЃЌЗЂЫЭЖЫвЊдкЗЂЫЭЪ§ОнжЎЧАВхШыжЁЭЌВНзжЁЃНгЪеЛњашвЊдквбНтЕїЕФЪ§ОнСїжаЫббАжЁЭЌВНзжЃЌвдШЗЖЈжЁЕФЮЛжУКЭжЁЖЈЪБаХЯЂЁЃжЁЭЌВНзжвЛАуЮЊвЛЯЕСаСЌајЕФТыдЊЃЌдкНгЪеЖЫашвЊЖдетвЛЯЕСаСЌајЕФТыдЊНјааМьВтЃЌШчЙћгыдЄЯШШЗЖЈЕФжЁЭЌВНзжЮЧКЯЃЌдђЫЕУїНгЪеЖЫгыЗЂЫЭЖЫЕФЪ§ОнЪЧБЃГжЭЌВНЕФЃЌПЊЪМНгЪеЃЌЗёдђВЛФмНјааНгЪеЁЃЭъГЩжЁЭЌВНзжМьВтЙЄзїЕФе§ЪЧЪ§зжЯрЙиЦїЁЃБОЮФВЩгУСїЫЎЯпММЪѕЃЌбаОПСЫЛљгк FPGAЕФИпЫйЪ§зжЯрЙиЦїЕФЩшМЦЗНЗЈЃЌВЂИјГіСЫ MAX+PLUSIIЛЗОГЯТЕФЗТецНсЙћЁЃ 1 Ъ§зжЯрЙиЦїдРэ Ъ§зжЯрЙиЦїдкЭЈаХаХКХДІРэжаЪЕжЪЪЧЦ№ЕНЪ§зжЦЅХфТЫВЈЦїЕФзїгУЃЌЫќПЩЖдЬиЖЈТыађСаНјааЯрЙиДІРэЃЌДгЖјЭъГЩаХКХЕФНтТыЃЌЛжИДГіДЋЫЭЕФаХЯЂЁЃЦфЪЕЯжЗНЗЈЪЧНјааСНИіЪ§зжаХКХжЎМфЕФЯрЙидЫЫуЃЌМДБШНЯЕШГЄЖШЕФСНИіЪ§зжађСажЎМфгаЖрЩйЮЛЯрЭЌЃЌЖрЩйЮЛВЛЭЌЁЃъРЛљБОЕФЯрЙиЦїЪЧвьЛђУХЃЌР§ШчЃЌy=aЈbЃЌЕБ a=bЪБЃЌy=0ЃЌБэЪОСНЮЛЪ§ОнЯрЭЌЃЛЕБ aЁйbЪБЃЌy=1ЃЌБэЪОСНЮЛЪ§ОнВЛЭЌЁЃЖрЮЛЪ§зжЯрЙиЦїПЩвдгЩвЛЮЛЯрЙиЦїМЖСЌЙЙГЩЁЃ NЮЛЪ§зжЯрЙиЦїЕФдЫЫуЭЈГЃПЩвдЗжНтЮЊвдЯТСНИіВНжшЃКЖдгІЮЛНјаавьЛђдЫЫуЃЌЕУЕН NИі 1ЮЛЯрЙидЫЫуНсЙћЃЛЭГМЦ NЮЛЯрЙидЫЫуНсЙћжа 0Лђ 1ЕФЪ§ФПЃЌЕУЕН NЮЛЪ§зжжаЯрЭЌЮЛКЭВЛЭЌЮЛЕФЪ§ФПЁЃ ЕБЪ§зжЯрЙиЦїНгЪеЕНвЛзщЪ§ОнЪБЃЌдкЪБжгЕФЩЯЩ§биЖджЁЭЌВНзжНјааМьВтЁЃЖдгкжЁЭЌВНзжЪЧвЛИіСЌај 16ЮЛЕФТыдЊЃЌЪ§зжЯрЙиЦїдкНјааМьВтЕФЙ§ГЬжаЃЌжЛгаЕБСЌајМьВтЕН 16ЮЛЕФТыдЊгыдЄЯШЩшЖЈЕФжЁЭЌВНзжЭъШЋЯрЭЌЪБЃЌВХгЩЪфГіЖЫЪфГіаХКХБэЪОжЁЭЌВНЁЃЗёдђЃЌШЮКЮвЛЮЛГіЯжВЛЯрЕШЃЌЪ§зжЯрЙиЦїгжНЋжиаТПЊЪМНјааМьВтЃЌжБЕНГіЯжСЌајЕФ 16ЮЛТыдЊгыдЄЯШЩшЖЈЕФ 16ЮЛТыдЊЭъШЋЯрЕШЪБВХНјааЪфГіЁЃЪ§зжЯрЙиЦїЕФЩшМЦвЛАуПМТЧВЩгУДЎааЪфШыЛђВЂааЪфШыСНжжЪфШыМьВтЗНЪНЃЌгЩгкДЎааЪфШыЪЧдк 16ИіЪБжгжмЦкФквРДЮЖдСНТЗДЎааЪфШыаХКХ AЁЂBНјаавьЛђдЫЫуЃЌВЂЭГМЦЪ§ОнЮЛЯрЭЌИіЪ§ЃЌМьВтЫйЖШНЯТ§ЃЌвЊЬсИпМьВтЫйЖШЃЌОЭвЊПМТЧВЩгУВЂааЪфШыМьВтЗНЪНЁЃ 2 ИпЫйЪ§зжЯрЙиЦїЕФ FPGAЪЕЯж дк 16ЮЛВЂааЪ§зжЯрЙиЦїжаЃЌгЩгкЪЕЯж 16ЮЛВЂааЯрЙиЦїашвЊЕФГЫЛ§ЯюЁЂЛђУХЙ§ЖрЃЌвђДЫЮЊНЕЕЭКФгУзЪдДЃЌПЩвдЗжНтЮЊ 4Иі 4ЮЛЯрЙиЦїЃЌШЛКѓгУСНМЖМгЗЈЦїЯрМгЕУЕНШЋВП 16ЮЛЕФЯрЙиНсЙћЃЌЦфНсЙЙЭМШчЭМ 1ЫљЪОЃЌШчЙћжБНгЪЕЯжИУЕчТЗЃЌећИідЫЫужСЩйвЊОЙ§Ш§МЖУХбгЪБЁЃЫцзХЯрЙиЪ§ФПЕФдіМгЃЌЫйЖШЛЙНЋНјвЛВННЕЕЭЁЃЮЊЬсИпЫйЖШЃЌВЩгУЁАСїЫЎЯпММЪѕЁБНјааЩшМЦЃЌФЃПщжаЖдУПвЛВНдЫЫуНсЙћЖМНјааЫјДцЃЌАДееЪБжгНкХФж№МЖЭъГЩдЫЫуЕФШЋЙ§ГЬЁЃЫфШЛУПзщЪфШыжЕашвЊОЙ§Ш§ИіНкХФКѓВХФмЕУЕНдЫЫуНсЙћЃЌЕЋЪЧЃЌУПИіНкХФЖМгавЛзщаТжЕЪфШыЕНЕквЛМЖдЫЫуЕчТЗЃЌУПМЖдЫЫуЕчТЗЩЯЖМгавЛзщЪ§ОнЭЌЪБНјаадЫЫуЃЌЫљвдзмЕФРДНВЃЌУПВНдЫЫуЛЈЗбЕФЪБМфжЛгавЛИіЪБжгжмЦкЃЌДгЖјЪЙЯЕЭГЙЄзїЫйЖШЛљБОЕШгкЪБжгЙЄзїЦЕТЪЁЃ  дкЪЙгУ VHDLНјааИпЫйЪ§зжЯрЙиЦїЩшМЦЪБЃЌжївЊЪЕЯж 4ЮЛЯрЙиЦїКЭЖрЮЛМгЗЈЦїФЃПщЕФЩшМЦЁЃЦфдЊМўЩњГЩЭМЗжБ№ЪЧ 4ЮЛЯрЙиЦїФЃПщ XIANGGUAN4ЁЂ3ЮЛМгЗЈЦїФЃПщ ADD3КЭ 4ЮЛМгЗЈЦїФЃПщ ADD4ЃЌЦфЕчТЗдРэЭМШчЭМ 2ЫљЪОЁЃЦфжа 4ЮЛЯрЙиЦїФЃПщ XIANGGUAN4ЕФжївЊдДДњТыЮЊЃК  entity xiangguan4 is port(a,b:in std_logic_vector(3 downto 0); sum:out std_logic_vector(2 downto 0); clk:in std_logic); end ; architecture one of xiangguan4 is signal ab :std_logic_vector(3 downto 0); begin abprocess(clk) begin if clk'event and clk='1' then if ab="1111" then sumelsif ab="0111" or ab="1011" or ab="1101" or ab="1110" then sumelsif ab="0001" or ab="0010" or ab="0100" or ab="1000" then sumelsif ab="0000" then sumelse sumend if; end if; end process; end one; 3 ЗТецЪЕбщМАНсТл дк MAX+PLUSIIЛЗОГЯТЃЌИљОнИпЫйЪ§зжЯрЙиЦїЕФдРэЭМНјааЩшМЦЃЌетРяНЋЪБжгЖЫ gckЩшМЦЮЊжмЦк 10nsЕФЪБжгЁЃa[15..0]ЖЫЮЊжЁЭЌВНзжЩшжУЖЫЃЌНЋЦфЩшжУЮЊ 1ЁЂ0НЛЬцТыЃЛ b[15..0]ЖЫЮЊТыдЊЪфШыЖЫЃЌЪфШыСЌајЕФаХКХЃЌЦфЪфШыТыдЊЕФжмЦквВЮЊ 10ns ЃЛc[4..0]зїЮЊМЧТМаХКХЃЌМЧТМСЌајЕФЪфШыТыдЊгыжЁЭЌВНзжЯрЭЌЕФИіЪ§ЁЃШЛКѓЖддРэЭМНјааБрвыЁЂЗТецЃЌЕУЕНЗТецВЈаЮШчЭМ 3ЫљЪОЁЃПЩвдПДГіЃЌДгСЌајЕФ 16ИіТыдЊЪфШыЕНЭЌВНМьВтЪфГіОЙ§ 3ИіЪБжгжмЦкЃЌЪфГіЖЫ c[4..0]БэЪОСЫСЌајЕФЪфШыТыдЊ bгыжЁЭЌВНзж aЯрЭЌЕФИіЪ§ЃЌЕБ c[4..0]ЮЊ 16ЪБЃЌБэЪО aКЭ bЪЕЯжСЫЭЌВНЁЃдкЖдИпЫйЪ§зжЯрЙиЦїНјааБрвыЁЂЗТецГЩЙІКѓЃЌЖдв§НХНјааЫјЖЈВЂНЋБрГЬЮФМўЯТдиЕН ALTERAЙЋЫО ACE1KЯЕСааОЦЌ EP1K30QC208НјааЪЕбщбщжЄЃЌЪЕбщНсЙће§ШЗЃЌБэУїЩшМЦЪЧПЩааЕФЁЃ  4 НсЪјгя Ъ§зжЯрЙиЦїЪЕЯжСЫЪ§зжЭЈаХЙ§ГЬжажЁЭЌВНзжЕФМьВтЃЌдкЪ§зжЭЈаХЯЕЭГжаОпгаживЊЕФзїгУЃЌЙуЗКгІгУгкжЁЭЌВНзжМьВтЁЂРЉЦЕНгЪеЛњЁЂЮѓТыаЃе§вдМАФЃЪНЦЅХфЕШСьгђЁЃБОЮФВЩгУ FPGAЖдИпЫйЪ§зжЯрЙиЦїНјааЩшМЦЃЌВЂНјааСЫБрвыЗТецКЭЯТдиЪЕЯжЁЃ БОЮФзїепДДаТЕуЃКЬсГіСЫВЩгУСїЫЎЯпММЪѕЪЕЯжВЂааИпЫйЪ§зжЯрЙиЦїЕФЩшМЦЗНЗЈЃЌЮЊИпЫйЪ§ОнСїЕФЩшМЦЬсЙЉСЫВЮПМЁЃ |

ЭјгбЦРТл