NAND FlashЕФЧ§ЖЏГЬађЩшМЦ

ЗЂВМЪБМфЃК2010-8-9 15:39

ЗЂВМепЃКlavida

|

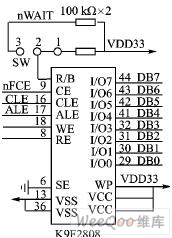

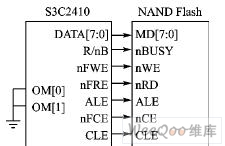

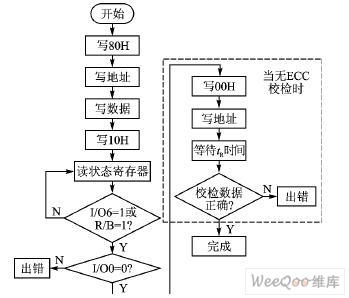

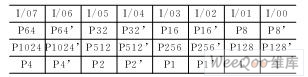

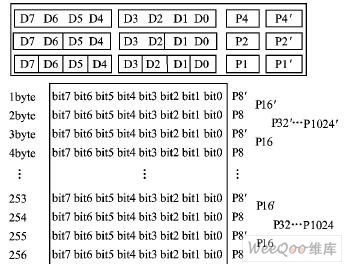

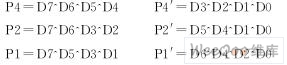

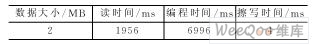

ЕБЧАИїРрЧЖШыЪНЯЕЭГПЊЗЂЩшМЦжаЃЌДцДЂФЃПщЩшМЦЪЧВЛПЩЛђШБЕФживЊЗНУцЁЃNORКЭ NANDЪЧФПЧАЪаГЁЩЯСНжжжївЊЕФЗЧвзЪЇЩСДцММЪѕЁЃNOR FlashДцДЂЦїЕФШнСПНЯаЁЁЂаДШыЫйЖШНЯТ§ЃЌЕЋвђЦфЫцЛњЖСШЁЫйЖШПьЃЌвђДЫдкЧЖШыЪНЯЕЭГжаЃЌГЃгУгкГЬађДњТыЕФДцДЂЁЃгыNORЯрБШ,NANDЩСДцЕФгХЕуЪЧШнСПДѓ,ЕЋЦфЫйЖШНЯТ§,вђЮЊЫќЕФI/OЖЫПкжЛга8Лђ16Иі,вЊЭъГЩЕижЗКЭЪ§ОнЕФДЋЪфОЭБиаыШУетаЉаХКХТжСїДЋЫЭЁЃNANDаЭFlashОпгаМЋИпЕФЕЅдЊУмЖШ,ШнСППЩвдБШНЯДѓ,МлИёЯрЖдБувЫЁЃ БОЮФвдШ§аЧЙЋЫОЕФ K9F2808UOBаОЦЌЮЊР§,НщЩмСЫNAND FlashЕФНгПкЕчТЗгыЧ§ЖЏЕФЩшМЦЗНЗЈЁЃЮФжаНщЩмСЫПЊЗЂNAND FlashЧ§ЖЏЛљБОдРэЃЌвтдкМђЛЏЧЖШыЪНЯЕЭГПЊЗЂЙ§ГЬЁЃ 1 NAND FlashЙЄзїдРэ S3C2410АхЕФNAND FlashжЇГжгЩСНВПЗжзщГЩЃКМЏГЩдкS3C2410 CPUЩЯЕФNAND FlashПижЦЦїКЭNAND FlashДцДЂаОЦЌЁЃвЊЗУЮЪNAND FlashжаЕФЪ§Он,БиаыЭЈЙ§NAND FlashПижЦЦїЗЂЫЭУќСюВХФмЭъГЩЁЃЫљвд, NAND FlashЯрЕБгкS3C2410ЕФвЛИіЭтЩш,ВЂВЛЮЛгкЫќЕФФкДцЕижЗЧјЁЃ 1.1 аОЦЌФкВПДцДЂВМОжМАДцДЂВйзїЬиЕу вЛЦЌNAND FlashЮЊвЛИіЩшБИ, ЦфЪ§ОнДцДЂЗжВуЮЊЃК1ЩшБИ=4 096ПщЃЛ1Пщ=32вГ;1вГ=528зжНк=Ъ§ОнПщДѓаЁ(512зжНк)+OOBПщДѓаЁ(16зжНк)ЁЃдкУПвЛвГжаЃЌзюКѓ16зжНкЃЈгжГЦOOBЃЌOut?of?BandЃЉгУгкNAND FlashУќСюжДааЭъКѓЩшжУзДЬЌгУЃЌЪЃгр512зжНкгжЗжЮЊЧААыВПЗжКЭКѓАыВПЗжЁЃПЩвдЭЈЙ§NAND FlashУќСю00h/01h/50hЗжБ№ЖдЧААыВПЁЂКѓАыВПЁЂOOBНјааЖЈЮЛЃЌЭЈЙ§NAND FlashФкжУЕФжИеыжИЯђИїздЕФЪзЕижЗЁЃ ДцДЂВйзїЬиЕугаЃК ВСГ§ВйзїЕФзюаЁЕЅЮЛЪЧПщЃЛNAND FlashаОЦЌУПвЛЮЛжЛФмДг1БфЮЊ0ЃЌЖјВЛФмДг0БфЮЊ1ЃЌЫљвддкЖдЦфНјаааДШыВйзїжЎЧАвЛЖЈвЊНЋЯргІПщВСГ§(ВСГ§МДЪЧНЋЯргІПщЕФЮЛШЋВПБфЮЊ1)ЃЛOOBВПЗжЕФЕк6зжНк(МД517зжНк)БъжОЪЧЗёЪЧЛЕПщЃЌжЕЮЊFFЪБВЛЪЧЛЕПщЃЌЗёдђЮЊЛЕПщЁЃГ§OOBЕк6зжНкЭтЃЌЭЈГЃжСЩйАбOOBЕФЧА3зжНкгУРДДцЗХNAND FlashгВМўECCТыЁЃ 1.2 NAND FlashНгПкЕчТЗ ЪзЯШНщЩмПЊЗЂАхЕФгВМўЩшМЦЃЌЭМ1ЮЊNAND FlashНгПкЕчТЗЁЃЦфжаПЊЙиSWЕФ1ЁЂ2СЌНгЪБR/BБэЪОзМБИКУ/УІЃЌ2ЁЂ3СЌНгЪБnWAITПЩгУгкдіМгЖС/аДЗУЮЪЕФЖюЭтЕШД§жмЦкЁЃдкS3C2410ДІРэЦїжавбОМЏГЩСЫNAND FlashПижЦЦїЃЌЭМ2ЮЊЮЂПижЦЦїгыNAND FlashСЌНгЕФЗНЪНЁЃ  ЭМ1 NAND FlashНгПкЕчТЗ 1.3 ПижЦЦїЙЄзїдРэ NAND FlashПижЦЦїдкЦфзЈгУМФДцЦїЧј(SFR)ЕижЗПеМфжагГЩфгаЪєгкздМКЕФЬиЪтЙІФмМФДцЦїЃЌОЭЪЧЭЈЙ§НЋNAND FlashаОЦЌЕФФкЩшУќСюаДЕНЦфЬиЪтЙІФмМФДцЦїжаЃЌДгЖјЪЕЯжЖдNAND FlashаОЦЌЖСЁЂМьбщКЭБрГЬПижЦЁЃЬиЪтЙІФмМФДцЦїгаЃКNFCONFЁЂNFCMDЁЂNFADDRЁЂNFDATAЁЂNFSTATЁЂNFECCЁЃ  ЭМ2 NAND FlashгыS3C2410СЌНгЕчТЗ 2 FlashЩеаДГЬађдРэМАНсЙЙ ЛљБОдРэЃКНЋдкSDRAMжаЕФвЛЖЮДцДЂЧјгђжаЕФЪ§ОнаДЕНNAND FlashДцДЂПеМфжаЁЃЩеаДГЬађдкзнЯђЩЯЗжШ§ВуЭъГЩЁЃЕквЛВу: жїЩеаДКЏЪ§ЃЌНЋSDRAMжавЛЖЮДцДЂЧјгђЕФЪ§ОнаДЕНNAND FlashДцДЂПеМфжаЁЃЕкЖўВу: ИУВуЬсЙЉЖдNAND FlashНјааВйзїЕФвГЖСЁЂаДМАПщВСГ§ЕШКЏЪ§ЁЃЕкШ§ВуЃКЮЊЕкЖўВуЬсЙЉОпЬхNAND FlashПижЦЦїжаЖдЬиЪтЙІФмМФДцЦїНјааВйзїЕФКЫаФКЏЪ§ЃЌИУВувВЪЧеце§НЋЪ§ОндкSDRAMКЭNAND FlashжЎМфЪЕЯжДЋЫЭЕФКЏЪ§ЁЃЦфжаЕкЖўВуЮЊЧ§ЖЏГЬађЕФЩшМЦЙиМќЫљдкЃЌЯТУцЖдИУВуЕФЖСЁЂаД(гжГЦБрГЬ)ЁЂВСГ§ЙІФмБрТыНјааЯъЯИНщЩмЁЃ 2.1 NAND Flash Read ЙІФмЃКЖСЪ§ОнВйзївдвГЮЊЕЅЮЛ,ЖСЪ§ОнЪБЪзЯШаДШыЖСЪ§ОнУќСю00H,ШЛКѓЪфШывЊЖСШЁвГЕФЕижЗ,НгзХДгЪ§ОнМФДцЦїжаЖСШЁЪ§Он,зюКѓНјааECCаЃбщЁЃ ВЮЪ§ЫЕУїЃКblockЃЌПщКХЃЛpageЃЌвГКХЃЛbufferЃЌжИЯђНЋвЊЖСШЁЕНФкДцжаЕФЦ№ЪМЮЛжУЃЛЗЕЛижЕ1ЃЌЖСГЩЙІЃЌЗЕЛижЕ0ЃКЖСЪЇАмЁЃ static int NF_ReadPage(unsigned int block, unsigned int page, unsigned char *buffer){ NF_RSTECC(); /* ГѕЪМЛЏ ECC */ NF_nFCE_L(); /* ЦЌбЁNAND FlashаОЦЌ*/ NF_CMD(0x00); /* ДгAЧјПЊЪМЖС *//* A0"A7(СаЕижЗ) */ NF_ADDR(0); /* A9A16(вГЕижЗ) */ NF_ADDR(blockPage&0xff); /* A17A24,(вГЕижЗ) */ NF_ADDR((blockPage>>8)&0xff);/* A25, (вГЕижЗ) */ NF_ADDR((blockPage>>16)&0xff);/* ЕШД§NAND FlashДІгкдйзМБИзДЬЌ */ ReadPage();/* ЖСећИівГ, 512зжНк */ ReadECC();/* ЖСШЁECCТы */ ReadOOB();/* ЖСШЁИУвГЕФOOBПщ *//* ШЁЯћNAND Flash бЁжа*/ NF_nFCE_H();/* аЃбщECCТы, ВЂЗЕЛи */ Return (checkEcc())} 2.2 NAND Flash Program ЙІФмЃКЖдвГНјааБрГЬУќСю, гУгкаДВйзїЁЃ УќСюДњТыЃКЪзЯШаДШы00h(AЧј)/01h(BЧј)/05h(CЧј), БэЪОаДШыФЧИіЧј; дйаДШы80hПЊЪМБрГЬФЃЪН(аДШыФЃЪН)ЃЌНгЯТРДаДШыЕижЗКЭЪ§Он; зюКѓаДШы10hБэЪОБрГЬНсЪјЁЃЭМ3ЮЊГЬађСїГЬЭМЁЃ  ЭМ3 аДГЬађСїГЬ ВЮЪ§ЫЕУїЃКblockЃЌПщКХЃЛpageЃЌвГКХЃЛbufferЃЌжИЯђФкДцжаД§аДШыNAND FlashжаЕФЪ§ОнЦ№ЪМЮЛжУЃЛЗЕЛижЕ0ЃЌаДДэЮѓЃЌЗЕЛижЕ1ЃЌаДГЩЙІЁЃ static int NF_WritePage(unsigned int block, unsigned int page, unsigned char *buffer){ NF_RSTECC(); /* ГѕЪМЛЏ ECC */ NF_nFCE_L(); /* ЦЌбЁNAND FlashаОЦЌ*/ NF_CMD(0x0); /* ДгAЧјПЊЪМаД */ NF_CMD(0x80); /* аДЕквЛЬѕУќСю *//* A0"A7(СаЕижЗ) */ NF_ADDR(0);/* A9A16(вГЕижЗ) */ NF_ADDR(blockPage&0xff);/* A17A24(вГЕижЗ) */ NF_ADDR((blockPage>>8)&0xff); /* A25(вГЕижЗ) */ NF_ADDR((blockPage>>16)&0xff);/* аДвГЮЊ512BЕНNAND FlashаОЦЌ */ WRDATA(); /*OOBвЛЙВ16зжНкЃЌУПвЛИізжНкДцЗХЪВУДгЩГЬађдБздМКЖЈвх, дкByte0 Byte2ДцECCМьбщТыЃЌByte6 ДцЗХЛЕПщБъжО*/ WRDATA(); /* аДИУвГЕФOOBЪ§ОнПщ */ CMD(0x10); /* НсЪјаДУќСю */ WAITRB();/* ЕШД§NAND FlashДІгкзМБИзДЬЌ *//* ЗЂЫЭЖСзДЬЌУќСюИјNAND Flash */ CMD(0x70); if (RDDATA()&0x1) { /*ШчЙћаДгаДэ, дђБъЪОЮЊЛЕПщ,ШЁЯћNAND Flash бЁжа*/ MarkBadBlock(block); return 0; } else { /* е§ГЃЭЫГіЃЌ ШЁЯћNAND Flash бЁжа*/ return 1;} 2.3 NAND Flash Erase ЙІФмЃКПщВСГ§УќСюЁЃ УќСюДњТыЃКЪзЯШаДШы60hНјШыВСаДФЃЪНЃЌШЛКѓЪфШыПщЕижЗЃЌНгЯТРДаДШыD0h, БэЪОВСаДНсЪјЁЃ ВЮЪ§ЫЕУїЃКblockЃЌПщКХЃЛЗЕЛижЕ0ЃЌВСГ§ДэЮѓЃЈШєЪЧЛЕПщжБНгЗЕЛи0ЃЛШєВСçóЯжДэЮѓдђБъМЧЮЊЛЕПщШЛКѓЗЕЛи0ЃЉЃЌЗЕЛижЕ1ЃЌГЩЙІВСГ§ЁЃ static int NF_EraseBlock(unsigned int block){/* ШчЙћИУПщЪЧЛЕПщ, дђЗЕЛи */ if(NF_IsBadBlock(block)) return 0; NF_nFCE_L(); /* ЦЌбЁNAND FlashаОЦЌ*/ NF_CMD(0x60); /* ЩшжУВСаДФЃЪН *//* A9A16(Page Address) , ЪЧЛљгкПщВСГ§*/ NF_ADDR(blockPage&0xff); NF_ADDR((blockPage>>8)&0xff); /* A25(Page Address) */ NF_ADDR((blockPage>>16)&0xff); NF_CMD(0xd0); WAITRB();CMD(0x70); if(RDDATA()&0x1){/*ШчгаДэ,БъЮЊЛЕПщ,ШЁЯћFlashбЁжа*/ MarkBadBlock(block); return 0; } else { /* ЭЫГіЃЌ ШЁЯћFlash бЁжа*/ return 1;} 3 ECCаЃМьдРэгыЪЕЯж гЩгкNAND FlashЕФЙЄвеВЛФмБЃжЄNANDЕФMemory ArrayдкЦфЩњУќжмЦкжаБЃГжадФмПЩППЃЌвђДЫдкNANDЕФЩњВњМАЪЙгУЙ§ГЬжаЛсВњЩњЛЕПщЁЃЮЊСЫМьВтЪ§ОнЕФПЩППадЃЌдкгІгУNAND FlashЕФЯЕЭГжавЛАуЖМЛсВЩгУвЛЖЈЕФЛЕЧјЙмРэВпТдЃЌЖјЙмРэЛЕЧјЕФЧАЬсЪЧФмБШНЯПЩППЕиНјааЛЕЧјМьВтЁЃШчЙћВйзїЪБађКЭЕчТЗЮШЖЈадВЛДцдкЮЪЬтЕФЛАЃЌNAND FlashГіДэЕФЪБКђвЛАуВЛЛсдьГЩећИіПщЛђЪЧвГВЛФмЖСШЁЛђШЋВПГіДэЃЌЖјЪЧећИівГЃЈР§Шч512зжНкЃЉжажЛгавЛЮЛЛђМИЮЛГіДэЁЃЖдЪ§ОнЕФаЃбщГЃгУЕФгаЦцХМаЃбщЁЂCRCаЃбщЕШЃЌЖјдкNAND FlashДІРэжаЃЌвЛАуЪЙгУвЛжжзЈгУЕФаЃбщЁЊЁЊECCЁЃECCФмОРе§ЕЅЮЛДэЮѓКЭМьВтЫЋЮЛДэЮѓЃЌЖјЧвМЦЫуЫйЖШКмПьЃЌЕЋЖд1ЮЛвдЩЯЕФДэЮѓЮоЗЈОРе§ЃЌЖд2ЮЛвдЩЯЕФДэЮѓВЛБЃжЄФмМьВтЁЃECCвЛАуУП256зжНкдЪМЪ§ОнЩњГЩ3зжНкECCаЃбщЪ§ОнЃЌет3зжНкЙВ24ЮЛЗжГЩСНВПЗжЃК6ЮЛЕФСааЃбщКЭ16ЮЛЕФаааЃбщЃЌЖргрЕФ2ЮЛжУ1ЃЌШчБэ1ЫљСаЁЃ  Бэ1 аЃМьЪ§ОнзщГЩ ЪзЯШНщЩмECCЕФСааЃМьЁЃECCЕФСааЃбщКЭЩњГЩЙцдђШчЭМ4ЫљЪОЃЌЁА^ЁББэЪОЁАЮЛвьЛђЁБВйзїЁЃгЩгкЦЊЗљЙиЯЕЃЌаааЃМьВЛзїНщЩмЃЌИааЫШЄЕФЖСепПЩвдВЮПМаОЦЌdatasheetЃЌдкШ§аЧЙЋЫОЭјеОПЩвдУтЗбЯТдиЁЃ  ЭМ4 СааЃбщКЭЩњГЩЙцдђ Ъ§бЇБэДяЪНЮЊЃК  ЕБЯђNAND FlashЕФвГжааДШыЪ§ОнЪБЃЌУП256зжНкЩњГЩвЛИіECCаЃбщКЭЃЌГЦжЎЮЊдECCаЃбщКЭЃЌБЃДцЕНвГЕФOOBЪ§ОнЧјжаЁЃЕБДгNAND FlashжаЖСШЁЪ§ОнЪБЃЌУП256зжНкЩњГЩвЛИіECCаЃбщКЭЃЌГЦжЎЮЊаТECCаЃбщКЭЁЃаЃбщЕФЪБКђЃЌИљОнЩЯЪіECCЩњГЩдРэВЛФбЭЦЖЯЃКНЋДгOOBЧјжаЖСГіЕФдECCаЃбщКЭгыаТECCаЃбщКЭАДЮЛвьЛђЃЌШєНсЙћЮЊ0ЃЌдђБэЪОЮоДэЃЈЛђепГіЯжСЫ ECCЮоЗЈМьВтЕФДэЮѓЃЉЃЛШє3зжНквьЛђНсЙћжаДцдк11ЮЛЮЊ1ЃЌБэЪОДцдквЛИіЮЛДэЮѓЃЌЧвПЩОРе§ЃЛШє3ИізжНквьЛђНсЙћжажЛДцдк1ЮЛЮЊ1ЃЌБэЪО OOBЧјГіДэЃЛЦфЫћЧщПіОљБэЪОГіЯжСЫЮоЗЈОРе§ЕФДэЮѓЁЃ 4 UBOOTЯТЙІФмбщжЄ ЪЕЯжUBOOTЖдNAND FlashЕФжЇГжжївЊЪЧдкУќСюааЯТЪЕЯжЖдNAND FlashЕФВйзїЁЃЖдNAND FlashЪЕЯжЕФУќСюЮЊЃКnand infoЁЂnand deviceЁЂnand readЁЂnand writeЁЂnand ereaseЁЂnand badЁЃгУЕНЕФжївЊЪ§ОнНсЙЙгаЃКstruct nand_flash_devКЭstruct nand_chipЃЌЧАепАќРЈжївЊЕФаОЦЌаЭКХЁЂДцДЂШнСПЁЂЩшБИIDЁЂI/OзмЯпПэЖШЕШаХЯЂЃЌКѓепЪЧЖдNAND FlashНјааОпЬхВйзїЪБгУЕНЕФаХЯЂЁЃгЩгкНЋЧ§ЖЏвЦжВЕНUBootЕФЗНЗЈВЛЪЧБОЮФжиЕуЃЌЙЪВЛзїЯъЯИНщЩмЁЃ бщжЄЗНЪНЃКЭЈЙ§TFTPНЋЪ§ОнЯТдиЕНSDRAMжаЃЌРћгУnand readЁЂnand writeЁЂnand ereaseШ§ИіУќСюЖдNAND FlashНјааЖСЁЂБрГЬЁЂВСаДВтЪдЁЃВтЪдНсЙћШчБэ2ЫљСаЁЃКЭdatasheetжаЪ§ОнЖдБШЃЌПЩвдЕУГіНсТлЃЌЧ§ЖЏдкЯЕЭГжадЫааСМКУЁЃ  Бэ2 ВтЪдНсЙћ Нсгя ЯждкЧЖШыЪНЯЕЭГгІгУдНРДдНЙуЗКЃЌЖјДцДЂЦїМўгжЪЧЧЖШыЪНЯЕЭГБиВЛПЩЩйЕФвЛВПЗжЃЌNAND FlashдкВЛГЌЙ§4 GBШнСПЕФашЧѓЯТЃЌНЯЦфЫћДцДЂЦїМўгХЪЦУїЯдЁЃБОЮФЫљЩшМЦЕФЧ§ЖЏВЂЮДЛљгкШЮКЮВйзїЯЕЭГЃЌПЩвдЗНБуЕивЦжВЕНЖржжВйзїЯЕЭГКЭBoot LoaderЯТЃЌЖдгкМђЛЏЧЖШыЪНЯЕЭГПЊЗЂгавЛЖЈЕФЪЕМЪвтвхЁЃ |

ЭјгбЦРТл