Р§ЫЕFPGAСЌди44ЃКDDRПижЦЦїМЏГЩгыЖСаДВтЪджЎVerilogДњТыНтЮі

ЗЂВМЪБМфЃК2016-11-8 17:49

ЗЂВМепЃКrousong1989

|

Р§ЫЕFPGAСЌди44ЃКDDRПижЦЦїМЏГЩгыЖСаДВтЪджЎVerilogДњТыНтЮі ЬиШЈЭЌбЇЃЌАцШЈЫљга ХфЬзР§ГЬКЭИќЖрзЪСЯЯТдиСДНгЃК http://pan.baidu.com/s/1c0nf6Qc

БОЪЕР§га8ИіФЃПщЃЌ3ИіВуМЖЁЃЦфВуДЮНсЙЙШчЭМ4.22ЫљЪОЁЃ

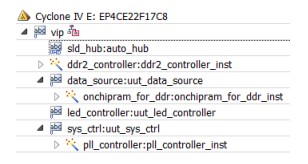

ЭМ4.22 ДњТыВуДЮЭМ Ёё vip.vЪЧЖЅВуФЃПщЃЌЦфЯТР§ЛЏСЫ5ИізгФЃПщЃЌМДsld_hub.vhdФЃПщЁЂddr2_controller.vФЃПщЁЂdata_source.vФЃПщЁЂonchipram_for_ddr.vФЃПщЁЂled_controller.vФЃПщКЭsys_ctrl.vФЃПщЁЃИУФЃПщНіНігУгкзгФЃПщМфЕФНгПкСЌНгЃЌвдМАКЭFPGAЭтВПЕФНгПкЖЈвхЃЌИУФЃПщжаЮДзїШЮКЮЕФТпМДІРэЁЃ Ёё sld_hub.vhdЖўМЖзгФЃПщЪЧвЛИіШэКЫIPЃЌБрвыЪБздЖЏВњЩњЃЌВЛЪЧЮвУЧдкЖЅВуДњТыvip.vжаР§ЛЏЕФЁЃЫќгУгкЮвУЧFPGAЕФЦЌФкRAMКЭQuartus IIжЎМфЭЈЙ§JTAGНјааЪ§ОнНЛЛЅЁЃЛЛОфЛАЫЕЃЌетИіФЃПщЦфЪЕЪЧвЛИіJTAGавщЕФНгПкЪЕЯжФЃПщЁЃИУФЃПщЪЧVHDLБраДЃЌВЂЧвФкВПДњТыЖдгУЛЇЪЧвЛИіЁАКкКаЁБЃЌЮвУЧжЛвЊЛсЪЙгУЫќОЭПЩвдЃЌЮоашЙиаФЫќЕФДњТыФкШнЁЃ Ёё ddr2_controller.vЖўМЖзгФЃПщвВЪЧвЛИіШэКЫIPЃЌЪЕЯжDDR2ЕФЪБађПижЦЙІФмЃЌВЂЧвЭЈЙ§вЛИіМђЕЅЕФAvalonНгПкЪЕЯжDDR2КЭFPGAТпМжЎМфЕФЖСаДЪ§ОнДЋЪфЁЃЦфЪЕИУФЃПщЯТЛЙгаЖрИізгФЃПщЃЌЕЋгЩгкжЛЪЧвЛИіIPКЫЃЌФкВПДњТыВЛжБНгПЊЗХЃЌЫљвдЮвУЧЙУЧвШЯЮЊЫќЪЧЮвУЧЙЄГЬжаЕФвЛИіФЃПщЁЃ Ёё data_source.vЖўМЖзгФЃПщЪЧгУЛЇТпМЃЌЮвУЧгУЫќЖЈЪБВњЩњвЛзщаДШыDDR2ЕижЗ0-1023ЕФСЌајЕФгаЙцТЩЕФЪ§ОнЃЛВЂЧвЮвУЧвВЛсЖЈЪБЕФЖСГіDDR2ЕижЗ0-1023ЕижЗЕФЪ§ОнЃЌНЋетаЉЪ§ОндйаДШыЕНFPGAР§ЛЏЕФЦЌФкRAMРяЁЃ Ёё onchipram_for_ddr.vШ§МЖзгФЃПщЪЧгВКЫIPЃЌЫќР§ЛЏЪЕЯжСЫFPGAЕФвЛПщЦЌФкRAMПеМфЁЃ Ёё sys_ctrl.vЖўМЖзгФЃПщжаР§ЛЏСЫPLLФЃПщЃЌВЂЧвЖдЪфШыPLLЕФИДЮЛаХКХвдМАPLLЫјЖЈКѓЕФИДЮЛаХКХНјааЁАвьВНИДЮЛЃЌЭЌВНЪЭЗХЁБЕФДІРэЃЌШЗБЃЯЕЭГЕФИДЮЛаХКХЮШЖЈПЩППЁЃ Ёё pll_controller.vШ§МЖзгФЃПщЮЊFPGAЦїМўЬигаЕФIPгВКЫФЃПщЃЌЦфжївЊЙІФмЪЧВњЩњЖрИіЬиЖЈЪфШыЪБжгЕФЗжЦЕЁЂБЖЦЕЁЂЯрЮЛЕїећКѓЕФЪфГіЪБжгаХКХЁЃ Ёё led_controller.vЖўМЖзгФЃПщНјаа24ЮЛМЦЪ§ЦїЕФбЛЗМЦЪ§ЃЌВњЩњЗжЦЕаХКХгУгкЪЕЯжLEDжИЪОЕЦЕФЩСЫИЁЃ |

ЭјгбЦРТл