Р§ЫЕFPGAСЌди31ЃКPLLР§ЛЏХфжУгыLEDжЎPLLЕФIPКЫХфжУ

ЗЂВМЪБМфЃК2016-9-12 17:04

ЗЂВМепЃКrousong1989

|

Р§ЫЕFPGAСЌди31ЃКPLLР§ЛЏХфжУгыLEDжЎPLLЕФIPКЫХфжУ ЬиШЈЭЌбЇЃЌАцШЈЫљга ХфЬзР§ГЬКЭИќЖрзЪСЯЯТдиСДНгЃК http://pan.baidu.com/s/1c0nf6Qc

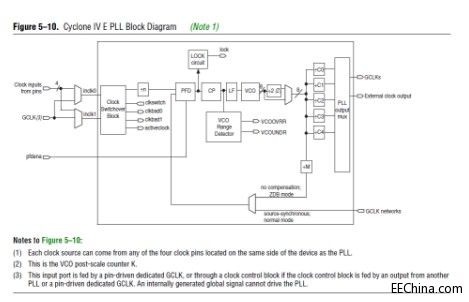

БОЪЕР§ЪЙгУСЫвЛИіPLLЕФгВКЫIPФЃПщЁЃЙигкPLLЃЌетРяМђЕЅЕФзіаЉЛљДЁЩЈУЄЁЃ PLL(Phase Locked Loop)ЃЌМДЫјЯрЛиТЗЛђЫјЯрЛЗЁЃPLLгУгкеёЕДЦїжаЕФЗДРЁММЪѕЁЃаэЖрЕчзгЩшБИвЊе§ГЃЙЄзїЃЌЭЈГЃашвЊЭтВПЕФЪфШыаХКХгыФкВПЕФеёЕДаХКХЭЌВНЃЌРћгУЫјЯрЛЗТЗОЭПЩвдЪЕЯжетИіФПЕФЁЃ ЪБжгОЭЪЧFPGAдЫааЕФаФдрЃЌЫќЕФУПДЮЬјЖЏБиаыОЋзМЖјКСЮоЦЋВюЃЈЕБШЛЯжЪЕЪРНчжаВЛДцдкЫљЮНЕФКСЮоЦЋВюЃЌЕЋЪЧЮвУЧЯЃЭћЫќЕФЦЋВюдНаЁдНКУЃЉЁЃвЛИіFPGAЙЄГЬжаЃЌВЛЭЌЕФЭтЩшЭЈГЃЙЄзїдкВЛЭЌЕФЪБжгЦЕТЪЃЌЫљвдвЛИіЪБжгПЯЖЈТњзуВЛСЫашЧѓЃЛДЫЭтЃЌгаЪБКђПЩФмСНИіВЛЭЌЕФФЃПщЙВгУвЛИіЪБжгЦЕТЪЃЌЕЋЪЧгЩгкЫћУЧдЫаадкВЛЭЌЕФЙЄзїЛЗОГКЭЪБађЯТЃЌЫљвдЫћУЧГЃГЃЪЧЭЌЦЕВЛЭЌЯрЃЈЯрЮЛЃЉЃЌдѕУДАьЃПгУPLLпТЁЃЕБШЛСЫЃЌЮвУЧЕФFPGAРяУцЖЈвхЕФPLLЃЌПЩВЛЪЧНіНіжЛгавЛИіЗДРЁЕїећЙІФмЃЌЫќЛЙгаБЖЦЕКЭЗжЦЕЕШЙІФмМЏГЩЦфжаЁЃбЯИёвЛЕуНВЃЌЮвОѕЕУетИіPLLЪЕМЪЩЯгІИУЫуЪЧвЛИіFPGAФкВПЕФЪБжгЙмРэФЃПщСЫЁЃВЛЖрЫЕЃЌШчЭМ3.9ЫљЪОЃЌДѓМвПДПДPLLФкВПЕФЙІФмПђЭМздМКЬхЮЖЬхЮЖЁЃ

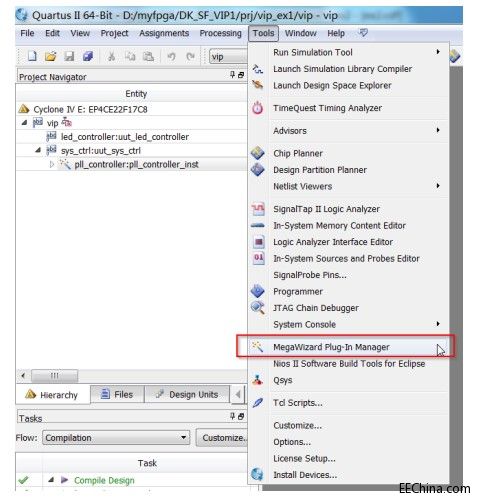

ЭМ3.9 PLLФкВПЙІФмНсЙЙ ЯъЯИЕФЙЄзїЛњРэЧыДѓМвВЮПМCyclone IV Device Handbook, Volume1ЕФChapter 5ЕФФкШнЁЃ Cyclone IVЕФPLLЪфШывЛИіЪБжгаХКХЃЌзюЖрПЩвдВњЩњ5ИіЪфГіЪБжгаХКХЃЌЪфГіЕФЦЕТЪКЭЯрЮЛЖМПЩвддквЛЖЈЕФЗЖЮЇФкЕїећЁЃ ЯТУцЮвУЧРДПДБОЪЕР§ШчКЮХфжУвЛИіPLLгВКЫIPЃЌВЂНЋЦфМЏГЩЕНЙЄГЬжаЁЃШчЭМ3.10ЫљЪОЃЌдкаТНЈЕФЙЄГЬжаЃЌЕуЛїВЫЕЅЁАToolsЈЄMegaWizard Plug-In ManagerЁБЁЃ

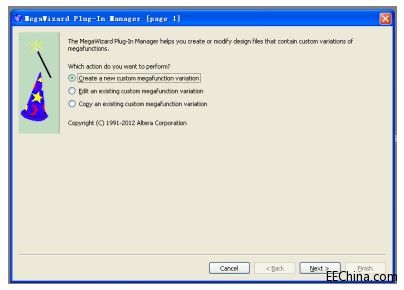

ЭМ3.10 ВЫЕЅбЁдёMegaWizard ШчЭМ3.11ЫљЪОЃЌбЁдёЁАCreat a new custom megafunction variationЁБЃЌШЛКѓNextЁЃ

ЭМ3.11 аТНЈMegaWizard НгзХбЁдёЮвУЧЫљашвЊЕФIPКЫЃЌШчЭМ3.12ЫљЪОНјааЩшжУЁЃ Ёё дкЁАSelect a megafunction from the list belowЁБЯТУцбЁдёIPКЫЮЊЁАI/O ЈЄ ALTPLLЁБЁЃ Ёё дкЁАWhat device family will you be usingЁБКѓУцЕФЯТРРИжабЁдёЮвУЧЫљЪЙгУЕФЦїМўЯЕСаЮЊЁАCyclone IV EЁБЁЃ Ёё дкЁАWhat type of output file do you want to create?ЁБЯТУцбЁдёгябдЮЊЁАVerilogЁБЁЃ Ёё дкЁАWhat name do you want for the output file?ЁБЯТУцЪфШыЙЄГЬЫљдкЕФТЗОЖЃЌВЂЧвдкзюКѓУцМгЩЯвЛИіУћГЦЃЌетИіУћГЦЪЧЮвУЧЯждке§дкР§ЛЏЕФPLLФЃПщЕФУћГЦЃЌЮвУЧПЩвдИјЫћЦ№УћНаpll_controllerЃЌШЛКѓЕуЛїNextНјШыЯТвЛИівГУцЁЃ

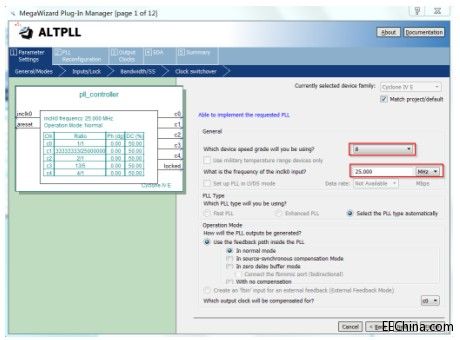

ЭМ3.12 бЁдёALTPLL IPКЫ НгзХРДЕНСЫPLLЕФВЮЪ§ХфжУвГУцЃЌзіШчЭМ3.13ЫљЪОЕФЩшжУЁЃШЛКѓЕуЛїNextНјШыЯТвЛИівГУцЁЃ Ёё дкЁАWhat device speed grade will you be using?ЁБКѓУцбЁдёЁА8ЁБЃЌМДЮвУЧЪЙгУЕФЦїМўЕФЫйЖШЕШМЖЁЃ Ёё дкЁАWhat is the frequency of the inclk0 input?ЁБКѓУцбЁдёЁА25MHzЁБЃЌМДЮвУЧЪфШыЕНИУPLLЕФЛљзМЪБжгЦЕТЪЁЃ

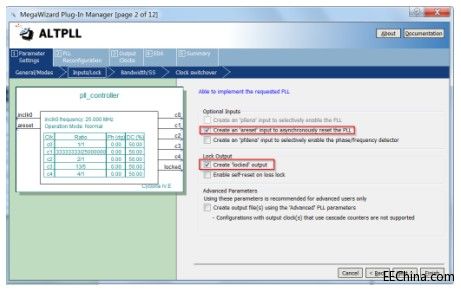

ЭМ3.13 PLLВЮЪ§ЩшжУ Input/lockвГУцжаЃЌШчЭМ3.14ЫљЪОНјааЩшжУЃЌНгзХЕуЛїNextНјШыЯТвЛИівГУцЁЃ Ёё ЙДбЁЁАCreate an ЁЎaresetЁЏ input to asynchronously reset the PLLЁБЃЌМДв§ГіИУPLLгВКЫЕФЁЏaresetЁЏаХКХЃЌетЪЧИУPLLгВКЫЕФвьВНИДЮЛаХКХЃЌИпЕчЦНгааЇЁЃ Ёё ЙДбЁЁАCreate ЁЎlockedЁЏ outputЁБЃЌМДв§ГіИУPLLгВКЫЕФЁЏlockedЁЏаХКХЃЌИУаХКХгУгкжИЪОPLLЪЧЗёЭъГЩФкВПГѕЪМЛЏЃЌвбОПЩвде§ГЃЪфГіСЫИпЕчЦНгааЇЁЃ

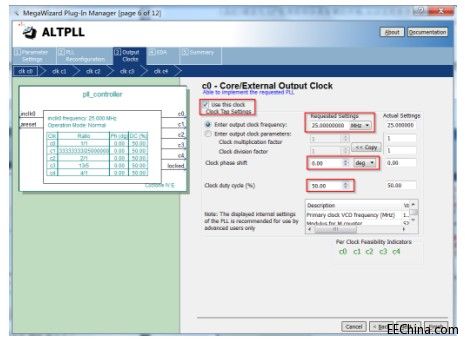

ЭМ3.14 PLLИДЮЛКЭЫјЖЈаХКХЩшжУ Bandwidth/SSЁЂClock SwitchoverКЭPLL ReconfigurationвГУцВЛгУЩшжУЃЌФЌШЯМДПЩЁЃжБНгНјШыOuput ClocksвГУцЃЌШчЭМ3.15ЫљЪОЃЌетРяга5ИіПЩбЁЕФЪБжгЪфГіЭЈЕРЃЌЭЈЙ§ЙДбЁЖдгІЭЈЕРЯТЗНЕФUse this clockбЁЯюПЊЦєЖдгІЕФЪБжгЪфГіЭЈЕРЁЃПЩвддкХфжУвГУцжаЩшжУЪфГіЪБжгЕФЦЕТЪЁЂЯрЮЛКЭеМПеБШЁЃетРяЪЧ C0ЭЈЕРЕФЩшжУЁЃ Ёё ЙДбЁЁАUse this clockЁБЃЌБэЪОЪЙгУИУЪБжгЪфГіаХКХЁЃ Ёё ЪфШыЁАEnter output clock frequencyЁБЮЊЁА25MHzЁБЃЌБэЪОИУЭЈЕРЪфГіЕФЪБжгЦЕТЪЮЊ25MHzЁЃ Ёё ЪфШыЁАClock phase shiftЁБЮЊЁА0 degЁБЃЌБэЪОИУЭЈЕРЪфГіЕФЪБжгЯрЮЛЮЊ0 degЁЃ Ёё ЪфШыЁАClock duty cycle(%)ЁБЮЊЁА50.00%ЁБЃЌБэЪОИУЭЈЕРЪфГіЕФЪБжгеМПеБШЮЊ50%ЁЃ

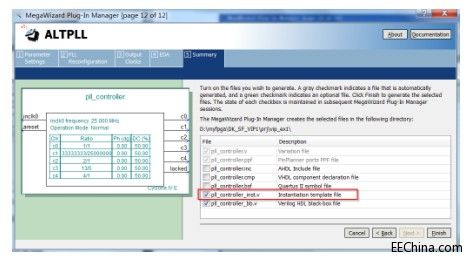

ЭМ3.15 PLLЪфГіЪБжгC0ЩшжУ КЭC0ЕФХфжУвЛбљЃЌЮвУЧПЩвдЗжБ№ПЊЦєВЂЧвХфжУC1ЁЂC2ЁЂC3КЭC4ЃЌетаЉЪБжгЫфШЛетИіР§ГЬднЪБгУВЛЩЯЃЌЕЋЪЧКѓајЕФР§ГЬНЋЛсЪЙгУЕНЁЃ Ёё C1ЕФЪБжгЦЕТЪЮЊ33.3333MHzЃЌЯрЮЛЮЊ0degЃЌеМПеБШЮЊ50%ЁЃ Ёё C2ЕФЪБжгЦЕТЪЮЊ50MHzЃЌЯрЮЛЮЊ0degЃЌеМПеБШЮЊ50%ЁЃ Ёё C3ЕФЪБжгЦЕТЪЮЊ65MHzЃЌЯрЮЛЮЊ0degЃЌеМПеБШЮЊ50%ЁЃ Ёё C4ЕФЪБжгЦЕТЪЮЊ100MHzЃЌЯрЮЛЮЊ0degЃЌеМПеБШЮЊ50%ЁЃ ХфжУЭъГЩКѓЃЌзюКѓдкSummaryвГУцЃЌШчЭМ3.16ЫљЪОЃЌЙДбЁЩЯ*_inst.vЮФМўЃЌетЪЧвЛИіPLLР§ЛЏЕФФЃАхЮФМўЃЌвЛЛсЮвУЧПЩвддкЙЄГЬФПТМЯТевЕНетИіЮФМўЃЌШЛКѓДђПЊЫќЃЌНЋЫќЕФДњТыИДжЦЕНЙЄГЬжаЃЌаоИФЖдгІНгПкМДПЩЭъГЩетИіIPКЫЕФМЏГЩЁЃ

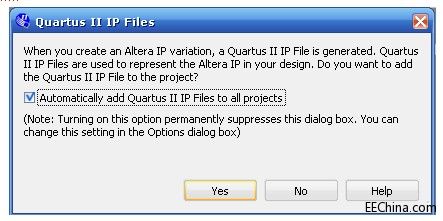

ЭМ3.16 SummaryХфжУвГУц ЕуЛїFinishЭъГЩPLLЕФХфжУЁЃЙЄГЬжаШєЕЏГіШчЭМ3.17ЫљЪОЕФЖдЛАПђЃЌЙДбЁЁАAutomatically add Quartus II IP Files to all projectsЁБбЁЯюКѓЃЌЕуЛїYesЁЃ

ЭМ3.17 здЖЏЬэМгЮФМўДАПк |

ЭјгбЦРТл