一种基于DSP的高精度波形发生器的设计

发布时间:2010-7-24 10:41

发布者:lavida

|

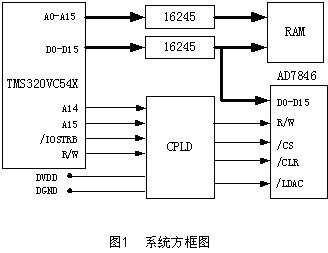

使用TMS320VC54X系列DSP控制模数转换器AD7846,设计出幅度可精确至1毫伏的波形发生器。文中给出了具体的硬件实现框图以及用来产生波形的DSP汇编源程序。 随着电子技术的发展,波形发生器已经广泛的应用在通信,控制,测量等各个领域。在很多地方,如测试测量领域,需要输出的波形能够精确地定位在某一整数值上,但通常由于ADC参考电平的限制,使之很难达到所需的精度,给系统的调试及软件设计带来诸多不便。本文采用了高精度的电压参考芯片ADR434为模数变换器提供参考电平,使波形发生器的最低可调电压达到125μV,为精确地输出整数值电压及其相应波形提供了方便的硬件环境。本设计具有输出精确,控制灵活方便等特点。 系统设计 本系统采用TI公司生产的TMS320VC54X系列DSP作为核心控制器件,并采CYPRESS工司生产的CY7C1021V(64K*16RAM)来扩充DSP的外部数据存储空间。在DSP与ADC及RAM之间的数据接口加入TI公司的74LVC16245(16位总线变换器)以增加DSP的驱动能力,并用来隔断器件间的干扰。DSP与DAC之间的逻辑控制采用CPLD实现,这样可以方便系统的设计与调试,本文中采用CPLD为ALETRA公司的EPM7064SLC84-10。整个系统的方框图如图1所示  器件简介 本系统所采用的模数变换器为AD7846,它是美国AD(Analog Device)公司基于LC2MOS工艺生产的16位数模转换器。它有  和 和 两个参考电平输入端以及一个片内放大器。标准情况下可以将其配置为单极性输出(0V到+5V,0V到+10V)或双极性输出( 两个参考电平输入端以及一个片内放大器。标准情况下可以将其配置为单极性输出(0V到+5V,0V到+10V)或双极性输出( , , )。当然,改变 )。当然,改变 和 和 两个参考电平输入端的电平,也可以改变其输出的动态范围。如本文中便是采用高精度电压参考芯片AD434提供参考电平,使DA的动态范围设置为 两个参考电平输入端的电平,也可以改变其输出的动态范围。如本文中便是采用高精度电压参考芯片AD434提供参考电平,使DA的动态范围设置为 。 。 AD7846采用分段式结构。DAC锁存器的高4位选通16个电阻串中的一段,段的两端接有运放作为缓冲,运放的输出反馈至12位的模数变换电路,并由该电路提供后12位分辨率。这种结构可以确保16位单调性,两个缓冲运放间输入失调电压的高度匹配还确保了优良的积分非线性。 除了优良的精度指标外,AD7846与微处理器的连接也非常方便。它有16位数据I/O口以及四根控制线(  ,R/ ,R/ , , 以及 以及 )。R/ )。R/ 与 与 用来控制对I/O锁存器的读写, 用来控制对I/O锁存器的读写, 信号用于多DAC系统中同步更新多片DAC数据, 信号用于多DAC系统中同步更新多片DAC数据, 用于将DAC的输出复位至0V。 用于将DAC的输出复位至0V。 AD7846参考电压的设计 为了使系统的输出波形在幅度上能够精确到1毫伏,本文采用AD434为AD7846提供参考电压。ADR434为AD公司生产的低噪声,高精度,低温漂的电压参考芯片。它采用了AD公司的温漂曲率修正专利技术,可以使其电压对温度的非线性达到最小。二者的具体连接如图2所示。  图2所示的连接方法使AD7846工作在双极性输出状态下。AD434为DA提供+4.096V的参考电平,DA根据此电平经过双极十六位线性分解,所得的最低可调电压为4.096V/215=125μV。具体的编码表如表1所示。 表1 AD7846编码表 ADC锁存器中的 二进制数 模拟输出( ) 最高位 最低位 1111 1111 1111 1111 1000 0000 0000 1000 1000 0000 0000 0001 1000 0000 0000 0000 0111 1111 1111 1111 0000 0000 0000 0000 +4.096V(32767/32768)=+4.095875V +4.096V(8/32768) =+0.001V +4.096V(1/32768) =+0.000125V +4.096V(0/32768) =0V -4.096V(1/32768) =-0.000125V -4.096V(32768/32768)=-4.096V 逻辑控制及软件实现 本文使用CPLD作为DSP控制DA的逻辑编程器件,将DA映射在DSP的I/O口,地址为4000H " 7FFFH。AD7846一共有四根控制线,它们组成的控制逻辑如表2所示。 表2 AD7846控制逻辑真值表 /CS R/W /LDAC /CLR 功能 1 0 0 X X X X 0 1 X 0 1 X X X 0 X X X X X 1 0 0 使DAC的I/O锁存器呈高阻态 数据(DB15"DB0)装入I/O锁存器 I/O锁存器中的数据输出到数据线上 I/O锁存器中的数据装入DAC锁存器 DAC锁存器装入数据000…000 DAC锁存器装入数据100…000 CPLD中烧入的逻辑图如图3所示。  对于波形的产生,通常有两种方法。一种方法为使用算法计算输出波形某点的幅度编码值(如正弦波可通过泰勒级数展开得到),这种方法可直接精确地计算出每个角度的波形值,所占用的存储空间小,但对于任意波形的输出,所需的算法较为复杂,系统实时性也会受到影响。另一种方法为查表法,该方法可能需要占用较大的存储空间,但软件控制却非常方便,实时性也更高。采用查表法的软件控制可由如下代码实现。 .mmregs .global main main: nop ori: stm #SINtable,ar2 ;将数据表头地址送入ar2 ld #13H,a ;循环输出20个样点值 JUMP: portw *ar2+,4000h ;AD7846被配置在I/O口的4000H " 7FFFFH处 rpt #1fffh ;改变rpt的值可以改变正弦波的频率 nop sub #1d,a bc JUMP,aneq b ori SINtable ;正弦波幅度编码表 .word 7FFFH .word 0A78DH .word 0CB3CH .word 0EF8DH .word 0F9BCH .word 0FFFFH .word 0F9BCH .word 0E78DH .word 0CB3CH .word 0A78DH .word 8000H .word 5872H .word 34C3H .word 1872H .word 0643H .word 0000H .word 0643H .word 1872H .word 34C3H .word 5872H .end 该段程序可使AD7846输出标准正弦波,幅度范围为  ,频率可通过改变rpt的值加以调节。若提供大量采样点,可使其实时输出高精度的任意波形。当然,利用DSP强大的运算处理能力,也可用软件计算出所需波形的各点采样值,这样可以节省存储空间,降低系统硬件成本。 ,频率可通过改变rpt的值加以调节。若提供大量采样点,可使其实时输出高精度的任意波形。当然,利用DSP强大的运算处理能力,也可用软件计算出所需波形的各点采样值,这样可以节省存储空间,降低系统硬件成本。 结束语 本系统已经过实际测量,系统各部分工作正常,AD7846可精确稳定地输出所需波形。该方案不仅达到了很高的精度与系统实时性,还具有控制灵活方便等特点,是一种很好的波形发生器。 |

网友评论