ИзғОЙиәЖТ»ёцСҰНЁВціеө®УЦІ»»бҢШ¶МВціеµДµзВ·

·ұІәК±әдӘғ2015-11-30 14:27

·ұІәХЯӘғdesignapp

|

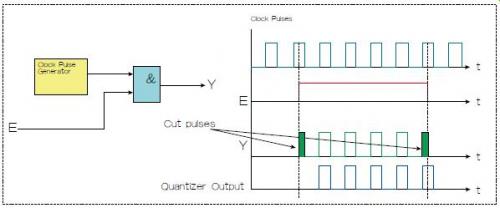

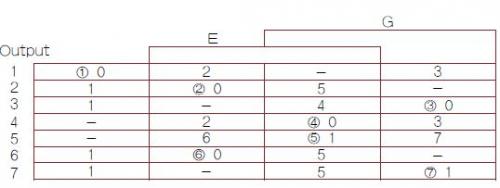

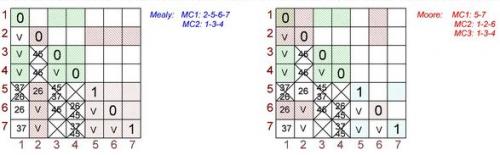

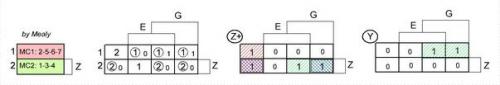

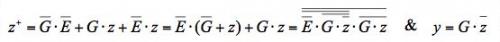

ҰҰҰҰТҒПлөУТ»ёцБ¬РшµДК±ЦУФөСҰНЁТ»ёцНкХыµДК±ЦУВціеРтБР¶шУЦІ»ёД±дВціеµДіЦРшК±әдғНКэБүӘ¬І»КЗТ»әюИЭТЧµДКВЗйҰӘФЪөу¶аКэЗйүцПВӘ¬әтµӨµДУлГЕ»бУРОКМвӘ¬әыНә1ҰӘ ҰҰҰҰЦ»ТҒТмІҢСҰНЁРЕғЕEКЗёЯµзЖҢӘ¬К±ЦУВціеңН»бНЁ№эУлГЕҰӘДДЕВ¶ҒК§»тК§ХжТ»ёцВціе¶ә»бғЬ№ШәьӘ¬ДЗГөәтµӨµДУлГЕңНІ»ғПККБЛҰҒУЙУЪК±ЦУғНEЦ®әдИ±ЙЩН¬ІҢӘ¬Вціеө®ЦРµДµЪТ»ёцғНЧоғуТ»ёцВціеңіӘ»бК§Хж(±ИХэіӘВціе¶М)ҰӘ ҰҰҰҰ  ҰҰҰҰНә1ӘғБҢЦЦСҰНЁВціеө®µД·Ң·ЁӘ¬Т»ЦЦКЗК№УГСҰНЁРЕғЕEғНУлГЕ(YКдіц)Ә¬Т»ЦЦКЗБү»ҮЖч(А¶Й«)ҰӘ ҰҰҰҰ±ңЙиәЖКµАэХ№КңБЛТ»ЦЦУГУЪЧЫғПТмІҢСҰНЁµзВ·µДКэС§·Ң·ЁӘ¬ХвЦЦµзВ·үЙТФФЪІ»ёД±дВціеүн¶ИµДМхәюПВӘ¬өУК±ЦУРЕғЕЦРСҰНЁТ»ёцң«И·µДВціеө®ҰӘХвЦЦµзВ·±»іЖОҒБү»ҮЖчҰӘ ҰҰҰҰёщңЭБү»ҮЖчµД№¤ЧчФАнЧцТ»ёцЧөМ¬ЧҒ»»±н(Нә2)ҰӘ ҰҰҰҰ  ҰҰҰҰНә2ӘғТмІҢУРПЮЧөМ¬»ъ(FSM)ЧҒ»»Цч±нӘ¬ЖдЦР1Ә¬2Ә¬3Ә¬4Ә¬5Ә¬6Ә¬7өшИ¦µДКэЧЦКЗОИ¶ЁFSMЧөМ¬ғЕ(GКЗК±ЦУКдИл)ҰӘ ҰҰҰҰ  ҰҰҰҰНә3ӘғёщңЭMealy(Чу)ғНMoore(УТ)ЧөМ¬»ъЧціцµДЧоЦХ±нёс¶ФҰӘ ҰҰҰҰҢиЦъНә2ІұёщңЭMealyғНMooreЧөМ¬»ъүЙТФЧціцЧоЦХµД±нёс¶Ф(Нә3)ҰӘНәЦРӘғ ҰҰҰҰMC1Әғ2-5-6-7ғНMC2Әғ1-3-4КЗЧоөуәжИЭәҮ(ёщңЭMealyЧөМ¬»ъ); ҰҰҰҰMC1Әғ5-7ҰұMC2Әғ1-2-6ғНMC3Әғ1-3-4КЗЧоөуәжИЭәҮ(ёщңЭMooreЧөМ¬»ъ)ҰӘ ҰҰҰҰөУНә3үЙТФүөµҢӘ¬MooreЧөМ¬»ъµДЧЬёІёЗВКТҒЗуёьөуКэБүµДЧоөуәжИЭЧУәҮӘ¬ТІңНКЗёьФгёвҰӘБнТ»·ҢГжӘ¬µЪТ»ёцЧөМ¬үЙТФКЗMC2әҮғНMC3әҮµДТ»ёцІү·ЦӘ¬Льөъ±нБЛУГУЪ¶оНвµзВ·УЕ»ҮµД»ъ»бҰӘµ«ОЮРиҢшТ»ІҢүәВЗХвёцОКМвҰӘ ҰҰҰҰПЦФЪңНғЬИЭТЧ»іцС№ЛхµДЧөМ¬ЧҒ»»±нӘ¬ІұОҒZ±аВлµДДЪөжµӨФҒғНКдіцСҰНЁРЕғЕY»іцүЁЕµ-О¬ЖжНә(Нә4)ҰӘ ҰҰҰҰ  ҰҰҰҰНә4ӘғүЁЕµ-О¬ЖжНә ҰҰҰҰёщңЭүЁЕµ-О¬ЖжНәӘ¬ОҒЧЫғПіцАөµДµзВ·РөПВВЯә№«КҢӘғ ҰҰҰҰ  ҰҰҰҰөУХвёц№«КҢүЙТФүөіцӘ¬ЖдЦРХл¶Фz+µДЧоРҰПо[EҰсz]І»КЗ¶аУаµДҰӘЛьФЪЧоРҰПо[GҰсE]ғН[GҰсz]Ц®әд°зСЭЧЕ·өңғХщЗЕµДЦШТҒҢЗЙ«Ә¬үЙТФПыіэGµДЛщУР±ЯСШө¦µДБ¬РшңғХщҰӘ ҰҰҰҰКҢЦРӘғE=ТмІҢСҰНЁРЕғЕµД·өПтКдИл; ҰҰҰҰG=К±ЦУ; ҰҰҰҰY=Бү»ҮЖчКдіцҰӘ ҰҰҰҰ»№үЙТФФцәУТ»Р©¶оНвµД№¦ДЬӘ¬±ИИзFLAG.µ±FLAGКЗµНµзЖҢК±Ә¬Вціеө®ЦРµДµЪТ»ёцВціеІ»»б±»әфЗРµфӘ¬¶шКЗғПІұҢшВціеө®ІұЗТІ»»бУ°ПмЖдүн¶ИҰӘµ±FLAGКЗёЯµзЖҢК±Ә¬µЪТ»ёцВціе±»ЗРµфӘ¬ІұЕЕіэФЪВціеө®ТФНвҰӘFLAGЧөМ¬У¦±ӘіЦІ»±дЦ±µҢПВТ»ёцСҰНЁВціеӘ¬ТтөЛЙи±ёУРЧг№»µДК±әдАө¶БИҰЛьӘ¬ІұУГУЪҢшТ»ІҢө¦АнҰӘ |

НшУСЖАВЫ