CPRIРТй·ЦОцТЗµДУІәюүҒ·ұУлКµПЦ

·ұІәК±әдӘғ2010-7-20 14:18

·ұІәХЯӘғconniede

|

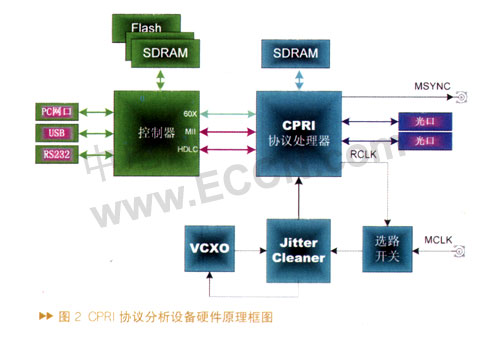

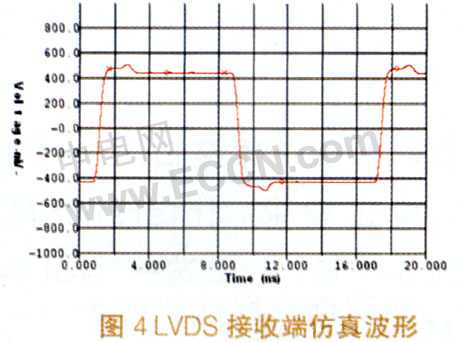

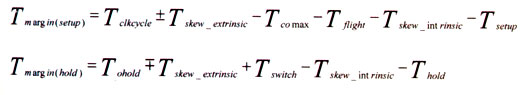

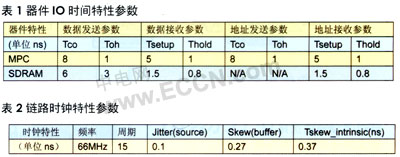

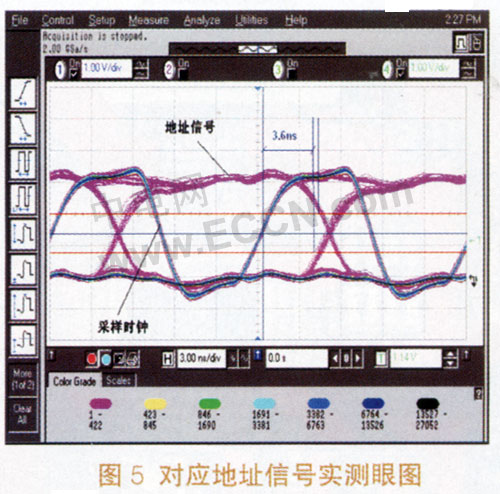

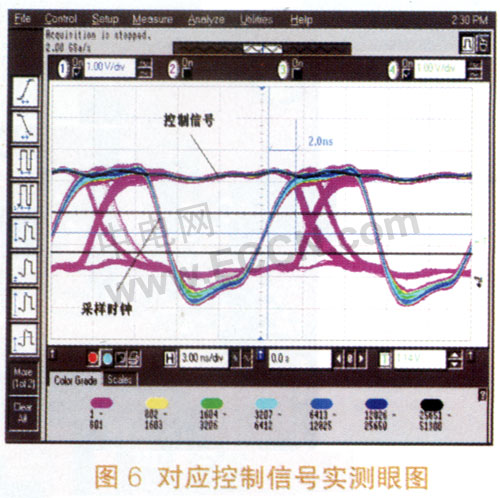

З°СФ ЛжЧЕНЁРЕәәКхµД·ұХ№Ә¬±кЧә»ҮµД»щөш-ЙдЖµҢУүЪФҢАөФҢКЬµҢёчі§әТµД№ШЧұӘ¬ФЪҢьәёДкДЪПаәМіцПЦБЛCPRIҰұOBSAIҰұTDRIҢУүЪ±кЧәҰӘCPRIЧчОҒНЁУГүҒ·ЕҢУүЪ±кЧәӘ¬УЙУЪЖдКµПЦЙПµДңәГәт±гРФКЬµҢБЛ¶а·Ңі§әТµДЦ§іЦӘ¬Йи±ё№©У¦ЙМПаәМНЖіцБЛ»щУЪCRPIРТй±кЧәµДАФ¶ІъЖ·Ә¬БнТ»·ҢГж»щУЪCRPIРТйµДҢ»»»»ъғНВ·УЙЖчТІФЪЦрҢӨµДіЙКмғННЖ№гҰӘүҒ·ЕµДНЁУГҢУүЪОҒ3G»щХңІъЖ·ҢЪФәіЙ±ңҰұМбёЯНЁУГРФғНБй»оРФМṩБЛ·Ң±гҰӘ CPRIРТйУЙ°®БұРЕҰұ»ҒОҒҰұNECҰұ±±µзғНОчГЕЧУОеёці§әТБҒғП·ұЖрЦЖ¶ЁӘ¬УГУЪОЮПЯНЁС¶»щХңЦР»щөшµҢЙдЖµЦ®әдµДНЁУГҢУүЪРТйӘ¬¶ФЖдЛьЧйЦҮғНі§әТүҒ·ЕҰӘCPRIөуІү·ЦДЪИЭЦчТҒХл¶ФWCDMA±кЧәӘ¬ОҒЖдүЙКµПЦБәғГ·юОсҰӘң·ЦОцӘ¬CPRIРТйН¬СщККУГУЪTD-SCDMAµЪИэөъТЖ¶ҮНЁС¶±кЧәҰӘCPRIРТйғбПт·ЦОҒОпАнІгғНКэңЭБөВ·ІгӘ»ЧЭПт·ЦОҒУГ»§ЖҢГжҰұүШЦЖ№ЬАнЖҢГжғНН¬ІҢЖҢГжӘ¬ңЯУРНә1ЛщКңµДҢб№№ҰӘ  УІәю№№әЬУлКµПЦ CPRIРТй·ЦОцТЗЦчТҒКµПЦЙдЖµµӨФҒҰұ»щөшµӨФҒµД№¦ДЬДӘДвҰӘТ»·ҢГжІЙәҮКэңЭҢшРРРТй·ЦОцӘ¬БнТ»·ҢГжФтІъЙъДӘДвКэңЭҢшРРРТй·ұЛНҰӘ»щУЪНә1µДРТйҢб№№Ә¬·ЦОцТЗУЙүШЦЖЖчҰұCPRIРТйө¦АнЖчҰұК±ЦУө¦АнТФә°¶ФНвҢУүЪЛДёцЦчТҒ№¦ДЬµӨФҒ№№іЙӘ¬Ц§іЦ614.4MbpsҰұ1.2288GbpsғН 2.4576GbpsИэЦЦКэңЭЛЩВКӘ¬ФАнүтНәИзНә2КңҰӘ  Іо·ЦРЕғЕµД¶ЛҢУғНЖӨЕд CPRI·ЦОцТЗ°еүЁЙПөжФЪLVDSҰұCMLғНLVPECLµИ¶аЦЦІо·ЦµзЖҢӘ¬І»Н¬µзЖҢЦ®әдµД»ӨБ¬РиТҒң«РДµШЙиәЖЛыГЗЦ®әдµДЖӨЕдғН¶ЛҢУӘ¬ТФКµПЦОИ¶ЁүЙүүµД№¤ЧчҰӘLVPECLµҢLVDSЦ®әдІЙУГDCсоғПӘ¬Нә3ғННә4ПФКңБЛ61.44MHzК±ЦУФЪХвЦЦЙиәЖПВµДІОКэғН·ВХжҢб№ыҰӘ   К±РтәЖЛг·ЦОц ЛщУРµДН¬ІҢК±РтµӨСШІЙСщ·ЦОцҢЁБұФЪИзПВБҢёцК±Рт±Х»·№«КҢµД»щөҰЙПӘғ №«КҢ:  №«КҢЦРёчІОКэµДғ¬Теә°ЖдАөФөүЙІОүәПВ±н:     ·ВХжәЖЛгҢб№ыПФКңӘ¬SDRAMІЙСщ±ӘіЦК±әдІ»ЧгӘ¬ФЪКµәКІЩЧчЦРӘ¬Ң«MCPµДК±ЦУПаО»Па¶Ф SDRAMК±ЦУµДПаО»ЦНғу0.6nsҢвңцОКМвҰӘ КµәКРЕғЕІвКФ үШЦЖРЕғЕµДКµІвСЫНәә°ЖдУлІЙСщК±ЦУµДПаО»№ШПµәыНә5ҰұНә6ҰӘ   ёщңЭКµІвКэңЭНЖЛгӘ¬µШЦ·РЕғЕғНКэңЭРЕғЕФЪSDRAMө¦µДІЙСщК±әдФӘ¶И·Ц±рОҒ2.8nsғН1.2nsӘ¬Ул·ВХжәЖЛгҢб№ыТ»ЦВҰӘ ҢбВЫ НЁ№эСПёсµДРЕғЕ·ВХжғНК±РтФӘ¶ИәЖЛгӘ¬КµК±µДµчХыЙиәЖғН¶Ф°еүЁµДІәңЦІәПЯУЕ»ҮғуӘ¬°еүЁРФДЬ±нПЦБәғГӘ¬Н¬К±ТІәхЙЩБЛPCBµДёД°жЙиәЖөОКэӘ¬ҢЪФәБЛСР·ұіЙ±ңҰӘФЪGHzә¶µДЙиәЖЦРӘ¬PCBµДЙиәЖ·ЗіӘЦШТҒӘ¬ө«КдПЯµДМШРФЧиү№үШЦЖӘ¬№эүЧµДМШРФЧиү№үШЦЖӘ¬¶ЛҢУЖӨЕдµДЙиәЖ¶ФРЕғЕµДУ°ПмІ»ИЭғцВФҰӘ¶ФУЪ№эүЧӘ¬УЙУЪіЙ±ңғНРФДЬЙПРиТҒңщғвӘ¬¶аІг°еүЁµД ОЮУГғёЕМТэИлµДµзИЭёғФШФцөуӘ¬ФЪғуРшµДEDAЦЖНә№¤ңЯЦРӘ¬Ц§іЦЦРәдІг¶аУағёЕМЙңіэµД№¦ДЬКЗ±ШРиµДҰӘЛжЧЕ°еүЁәҮіЙ¶ИµДМбёЯӘ¬·ВХжәЖЛгµИ№¤ЧчФҢАөФҢПФµГ±ШТҒӘ¬ЖңңСйЙиәЖµДДкөъЦрҢӨңГФ¶Ә¬үЙФ¤ЦҒµДҰұүЙүШЦЖРФЙиәЖРиТҒЙшНёµҢГүТ»ёцПёҢЪҰӘ |

НшУСЖАВЫ