FPGA实战演练逻辑篇46:逻辑复制与资源共享

发布时间:2015-7-5 19:40

发布者:rousong1989

|

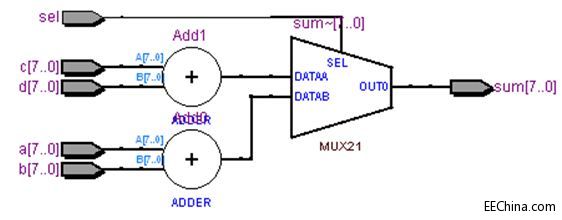

逻辑复制与资源共享 本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》 配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt 逻辑复制是一种通过增加面积来改善时序条件的优化手段。逻辑复制最主要的应用是调整信号的扇出。如果某个信号需要驱动的后级逻辑信号较多,换句话说,也就是其扇出非常大,那么为了增加这个信号的驱动能力,就必须插入很多级的Buffer,这样就在一定程度上增加了这个信号的路径延时。这时可以复制生成这个信号的逻辑,用多路同频同相的信号驱动后续电路,使平均到每路的扇出变低,这样不需要插入Buffer就能满足驱动能力增加的要求,从而节约该信号的路径延时。 资源共享和逻辑复制恰恰是逻辑复制的一个逆过程,它的好处就在于节省面积,同时可能也要以速度的牺牲为代价。(特权同学,版权所有) 看一个实例,如下: // Verilog例程 module example(sel, a, b, c, d, sum); input sel,a,b,c,d; output[1:0] sum; wire[1:0] temp1 = {1'b0,a}+{1'b0,b}; wire[1:0] temp2 = {1'b0,c}+{1'b0,d}; assign sum = sel ? temp1:temp2; endmodule 该代码综合后的视图如图5.12所示,和我们的代码表述的一致,有连个加法器进行运算,结果通过2选1选择器后输出给sum。(特权同学,版权所有)

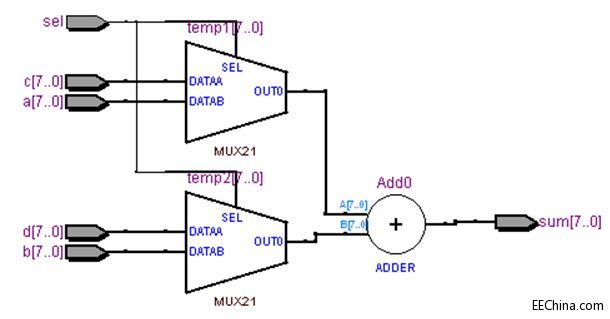

同样实现这个的功能,我们还可以这么编写代码: // Verilog例程 module example(sel, a, b, c, d, sum); input sel; input[7:0] a,b,c,d; output[7:0] sum; wire[7:0] temp1 = sel ? a:c; wire[7:0] temp2 = sel ? b:d; assign sum = temp1+temp2; endmodule 综合后的视图如图5.13所示,原先两个加法器我们现在用一个加法器同样可以实现。而原先的一个2选1选择器则需要4选2选择器(可能是两个2选1选择器来实现)替代。如果在设计中加法器资源更宝贵些,那么后面这段代码通过加法器的复用,相比前面一段代码更加节约资源。(特权同学,版权所有)

|

网友评论