数字卫星信道接收芯片(DVB_S)帧格式转换模块设计

发布时间:2010-7-12 23:47

发布者:conniede

|

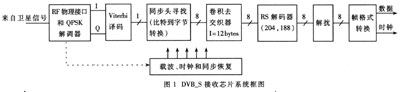

数字卫星接收芯片(DVB_s)是准基带采样变换到MPEG-2码流的完全解决方案的集成芯片。主要用于卫星传输的数字电视、数字语音的压缩编码的数字解调与信道解码。此传输系统基于前向纠错编码(FEC)技术和QPSK调制技术,可保证传输业务的可靠性。 DVB-S系统功能模块如图1所示。包括物理接口、QPSK解调、Viterbi译码、同步头寻找、去交织、RS解码、解扰以及帧格式转换。经过帧格式转换后的数据称为TS流,输出的时钟为占空比近似为1:1的均匀时钟。TS数据和时钟送给解码芯片进行信源解码。

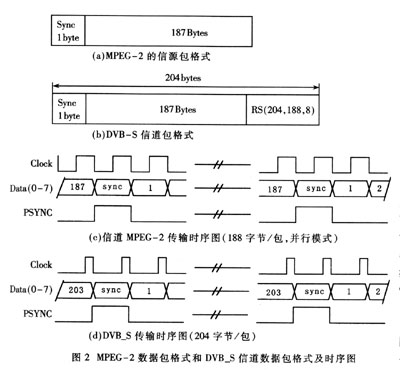

1 帧格式转换 帧格式转换位于信道传输的最前端(或最末端),完成信道传输与信源MPEG-2编(解)码的相应数据格式的转换以及产生相应的时钟。在发送端,该部分将信源MPEG-2的数据包格式转换成信道传输的数据包格式,并产生信道传输编码部分的时钟。相应地,接收端部分将信道传输的数据包格式转换成信源MPEG-2的包格式,同时也产生信源MPEG-2的时钟。 1.1 进行数据格式转换的原因 进行数据格式转换是由于DVB-S信道帧格式与MPEG-2的信源帧格式不同。信源MPEG-2编(解)码数据包格式是按段组织的,每一个数据段包括1个字节的段同步和187个字节的数据,这种帧结构称为信源数据包格式。而本方案信道传输的RS编(解)码是按每个段进行的,即(204,188,16)码,也就是每段187个字节信息数据外又增加16个纠错校验位。 MPEG-2数据包格式和DVB信道数据包格式及时序如图2所示。

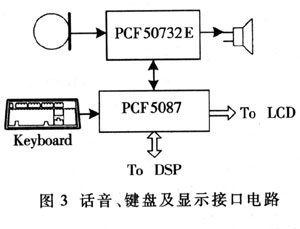

这里主要讨论接收端的格式转换,即将DVB_S信道格式转换为MPEG-2信源格式。接收端数据格式转换主要包括两部分:(1)去掉校验字节;(2)将时钟变为占空比1?1。去除校验字节子部分将由RS编译码引入的冗余校验字节去掉,使每包的数据恢复为188字节。为防止信号畸变,保证数据正确地采样,时钟占空比应展宽为1:1。目前市场上的解码芯片支持并行和串行两种模式。以上讨论的并行模式输出(以字节形式输出)、串行模式输出以比特形式输出。 1.2 帧格式转换设计 1.2.1 并行模式 该部分将去除由DVB-S的RS编码引入的冗余校验字节,使每包的数据恢复为MPEG-2格式的188字节?其结构框图如图3所示。其核心部分为数据缓冲区的设计和读时钟的产生。

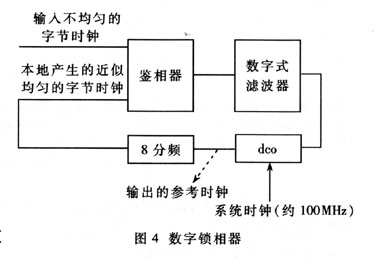

(1)数据缓冲区 从信道数据包格式和信源包格式可以看出,相对信源包而言,信道包每包多出了16个RS码校验字节。信道数据按如下规则写入缓冲区,读端也按照一定规则读出数据:16个字节的RS校验码不写入缓冲区,其他数据按地址顺序写入缓冲区;在读出时,按照顺序读出缓冲区的内容,每帧为188字节的数据。其中数据写入缓冲区时,使用信道的时钟,而从缓冲区读出数据时,使用信源时钟。 为了保证读出数据的正确性,只能读已经写入的数据,也就是读操作滞后于写操作?这里一个存储单元为1个字节 。设计时采用SRAM作为数据缓冲区。 (2)读时钟以及信源时钟的产生 参考时钟的产生 为了减少整个系统的复杂度(主要为减少芯片外围电路),前级时钟恢复(Clock Recovery)模块采用了内插算法,引起了符号时钟周期的不确定性,进一步导致了字节时钟周期的不确定性,即传输给帧格式转换模块的字节时钟是很不均匀的。 为了得到近似均匀的字节时钟,帧格式转换模块采用数字锁相法产生一个近似均匀的参考时钟,如图4所示。 图4中,本地产生的近似均匀的字节时钟频率与输入的不均匀字节时钟的频率保持一致,而输出的参考时钟频率是输入字节时钟的8倍,且近似均匀。之所以要8分频而不是2分频或是4分频,主要考虑到在DVB_S系统中符号频率是2MHz-45MHz,折算到字节频率为0.25MHz-5.5125MHz(如果Viterbi译码的删节模式是1/2,字节频率=符号频率×1/4×Viterbi译码的删节模式),当符号频率很低时,如采用2分频或4分频数字锁相器稳定较慢,而8分频符合设计要求。

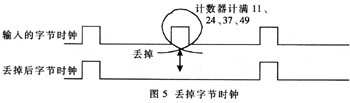

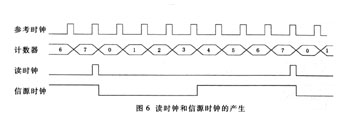

读时钟产生以及信源时钟的生成 由于信源格式的每个包只有188字节,因此首先把信道格式的每包204字节使能去掉16个,采用丢时钟的方法,在204中丢掉16次使能,即51中丢掉4次。故采用一个51计数器。当计数到11、24、37、49时丢掉输入的字节时钟,得到丢掉后的每包只有188个字节时钟(如图5)。把丢掉后的字节时钟传输给上面的参考时钟产生模块,得到较均匀的参考时钟。 由新的较均匀的参考时钟8分频即可得到较均匀的读时钟(每包188个),以及信源时钟(占空比约为1:1)。在设计时用一个模8计数器即可。如图6,读时钟和信源时钟是对齐的。

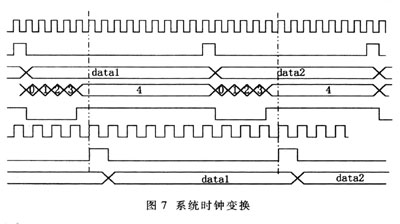

1.2.2 串行模式 根据解码芯片的要求,串行模式的输出工作在60MHz系统时钟上,而本设计中的数字卫星信道接收芯片工作在90MHz系统时钟上。因此首先需要系统时钟的变换,然后进行并行模式的处理,最后再并/串变换。 系统时钟的变换是关键,其设计可分为三步,如图7所示。

(1)把工作在90MHz上的字节时钟展宽,这时可用一个3bit的计数器实现,Verilog代码如下: always @ (posedge sys_clk) begin if(rst | byt_clk) sys_cnt <= 3'd0;? else if(~sys_cnt[2])? sys_cnt <= sys_cnt + 3'd1;? end assign 展宽的字节时钟 = sys_cnt[2]?? (2)用60MHz的系统时钟采样展宽的字节时钟的上跳沿,产生工作在60MHz上的字节时钟。 (3)以60MHz的系统时钟为采样时钟,工作在60MHz上的字节时钟为使能信号,采样输入的数据,得到工作在60MHz上的数据。这样,就不会出现多采或者漏采现象。 然后把60MHz的系统时钟、工作在60MHz上的字节时钟及数据送给并行模块。从并行模块出来的是信源的字节时钟,其每一个字节时钟周期中均有8个参考时钟,因此可以把这8个参考时钟作为串行输出的比特时钟,每一个字节数据在一个字节时钟周期内变为8个比特的数据,按照比特时钟输出。 2 ASIC实现 笔者选择的硬件描述语言是Verilog HDL。综合库?synthesis library 选用UMC 0.18μm工艺。综合之后此模块的总面积为6000门左右。此方案已经应用到DVB-S芯片的设计中,并且在FPGA上已经调试成功。 本文所讲述的帧格式转换处于DVB-S芯片中的最后一个模块,其主要功能是将数据和时钟从信道格式转变为信源格式。其输出连到解码芯片,解码芯片能否正常工作此模块起着非常关键的作用。 |

网友评论