FPGAШыУХЃКЕквЛИіЙЄГЬЪЕР§жЎЩшМЦЪфШы

ЗЂВМЪБМфЃК2015-2-28 10:58

ЗЂВМепЃКrousong1989

|

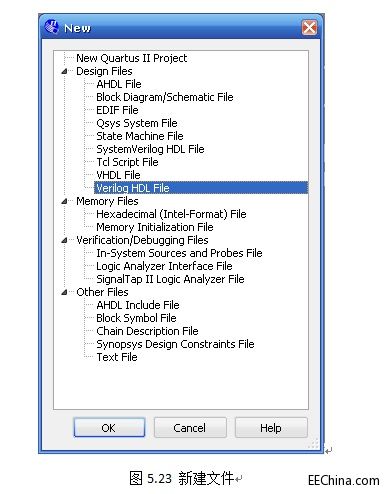

FPGAШыУХЃКЕквЛИіЙЄГЬЪЕР§жЎЩшМЦЪфШы ЪщжаДњТыЧыЗУЮЪЭјХЬЃКhttp://pan.baidu.com/s/1bndF0bt ЯТУцЮвУЧОЭРДДДНЈЙЄГЬЖЅВуЮФМўЃЌЮвУЧПЩвдЕуЛїВЫЕЅРИЕФFileЈЄNewЁЃЌШЛКѓЕЏГіШчЭМ5.23ЫљЪОЕФаТНЈЮФМўДАПкЃЌдкетРяЮвУЧПЩвдбЁдёИїжжашвЊЕФЩшМЦЮФМўИёЪНЁЃПЩвдзїЮЊЙЄГЬЖЅВуЩшМЦЮФМўЕФИёЪНжївЊдкDesign FilesРрБ№ЯТЃЌЮвУЧбЁдёVerilogHDL FileЃЈЛђепVHDL FileЃЉВЂЕЅЛїOKЭъГЩЮФМўДДНЈЁЃ

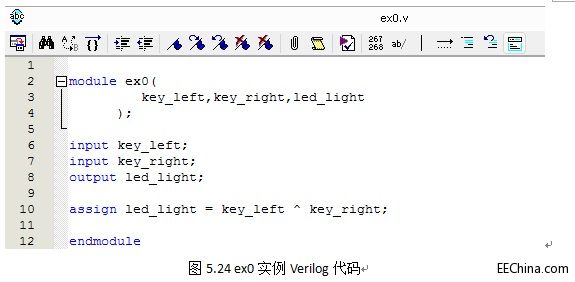

ЭМ5.23 аТНЈЮФМў дкжїБрМДАПкжаЃЌГіЯжСЫвЛИіаТНЈЕФПеАзЕФПЩБрМЮФМўЃЌЮвУЧНгзХдкИУЮФМўжаЪфШыЪЕЯжЪЕбщЙІФмЕФвЛЖЮVerilogДњТыЃЈШчЙћЪЧаТНЈVHDLЮФМўдђЖдгІЪфШыVHDLДњТыЃЉЃЌШчЭМ5.24ЫљЪОЁЃ

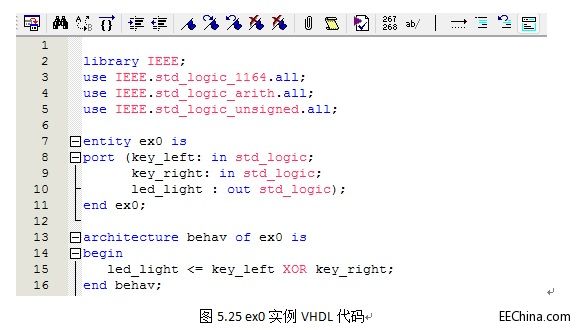

ЭМ5.24 ex0ЪЕР§VerilogДњТы Ёя ДњТыНВНт L2/L12ЃКЙЬЖЈгУЗЈЩъУїФЃПщЃЌИУФЃПщУќУћЮЊex0ЁЃ L3ЃКНЋИУФЃПщЫљгаЪфШыЪфГіаХКХСаБэЁЃ L6ЃКзѓМќЪфШыМќжЕВЩбљаХКХЁЃ L7ЃКгвМќЪфШыМќжЕВЩбљаХКХЁЃ L8ЃКLEDжИЪОЕЦЪфГіаХКХЁЃ L10ЃКвьЛђдЫЫуЃЌЪЙЕУСНИіАДМќКЭжИЪОЕЦЕФЙиЯЕгыБэ5.1ЕФецжЕБэЯрЮЧКЯЁЃ ШчЙћЪЙгУVHDLЪфШыЃЌдђЖдгІЕФVHDLДњТыШчЭМ5.25ЫљЪОЁЃ

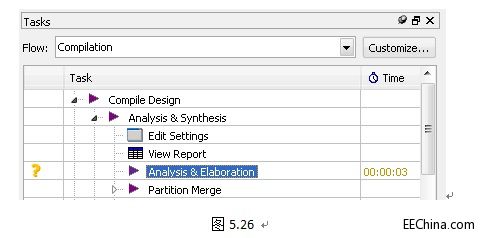

ЭМ5.25 ex0ЪЕР§VHDLДњТы дкетИіИеДДНЈЕФVerilogЃЈЛђVHDLЃЉЮФМўжаЪфШыДњТыКѓЃЌПьНнМќCtrl+SЛђЕуЛїFileЈЄSaveКѓдђЛсЕЏГівЛИіЖдЛАПђЬсЪОЪфШыЮФМўУћКЭБЃДцТЗОЖЃЌФЌШЯЮФМўУћЛсКЭЮвУЧЫљУќУћЕФmoduleУћЃЈЛђentityУћЃЉЯрвЛжТЃЌФЌШЯТЗОЖвВЛсЪЧЕБЧАЕФЙЄГЬЮФМўМаЁЃЮвУЧЭЈГЃвВЖМВЩгУФЌШЯЩшжУНјааБЃГжМДПЩЁЃ здДЫЃЌЮвУЧЕФЙЄГЬДДНЈКЭЩшМЦЪфШыЙЄзївбОЭъГЩЁЃЕЋЪЧЮЊСЫбщжЄвЛЯТЩшМЦЪфШыЕФДњТыЕФЛљБОгяЗЈЪЧЗёе§ШЗЃЌПЩвдЕуЛїFlow ЈЄ CompilationЯТЕФAnalysis & ElaborationАДХЅЃЌШчЭМ5.26ЫљЪОЁЃЭЌЪБЮвУЧПЩвдЪфГіДђгЁДАПкЕФProcessingРяЕФаХЯЂЃЌАќРЈИїжжwarningКЭErrorЁЃErrorЪЧВЛЕУВЛЙизЂЕФЃЌвђЮЊErrorвтЮЖзХЮвУЧЕФДњТыгагяЗЈДэЮѓЃЌКѓајЕФБрвыНЋЮоЗЈМЬајЃЛЖјwarningдђВЛвЛЖЈЪЧжТУќЕФЃЌЕЋКмЖрЪБКђwarningжаАЕВиаўЛњЃЌКмЖрЧБдкЕФЮЪЬтЖМПЩвдДгетаЉЬѕФПжабАевЕНжыЫПТэМЃЁЃЕБШЛСЫЃЌвВВЂВЛЪЧЫЕвЛИіЩшМЦБрвыЯТРДОЭВЛПЩвдгаwarningЃЌШчЙћЩшМЦепШЗШЯетаЉwarningЗћКЯЮвУЧЕФЩшМЦвЊЧѓЃЌФЧУДПЩвдКіТдЫќЁЃ

ЭМ5.26 зюКѓЃЌдкAnalysis & ElaborationЭъГЩКѓЃЌЭЈГЃЧАУцЕФЮЪКХЛсБфГЩЙДКХЃЌБэЪОЭЈЙ§ЁЃ БОЮФНкбЁздЬиШЈЭЌбЇЕФЭМЪщЁЖFPGA/CPLDБпСЗБпбЇЁЊЁЊПьЫйШыУХVerilog/VHDLЁЗ ЪщжаДњТыЧыЗУЮЪЭјХЬЃКhttp://pan.baidu.com/s/1bndF0bt |

ЭјгбЦРТл