ИзәОҪ«өзФҙНкХыРФ·ЦОцУлЗ©әЛөДЛЩ¶ИМбёЯ10ұ¶Јҝ

·ўІјКұјдЈә2014-12-17 11:21

·ўІјХЯЈәdesignapp

|

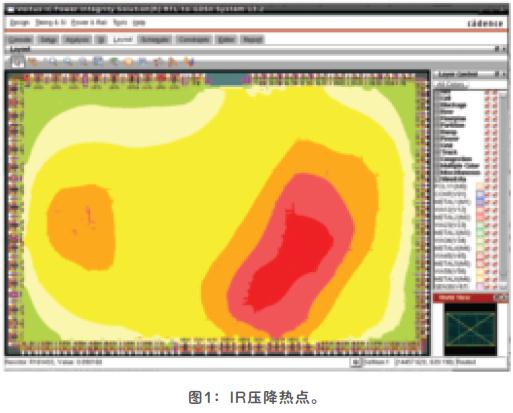

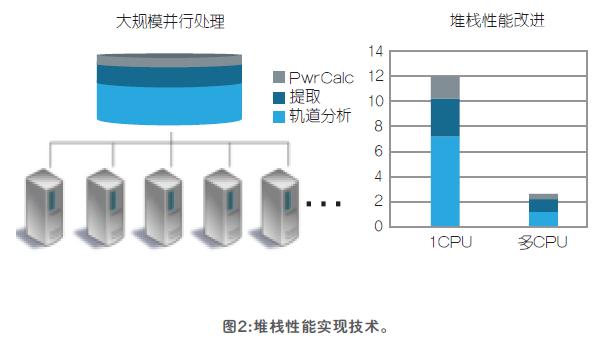

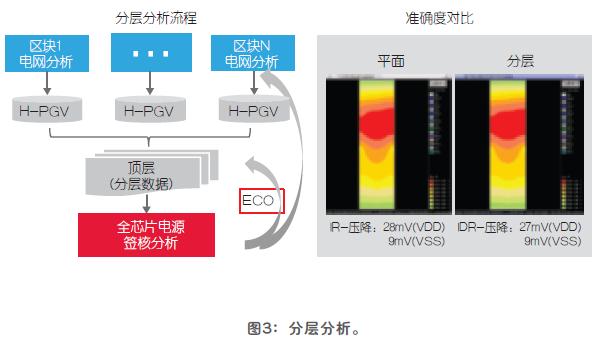

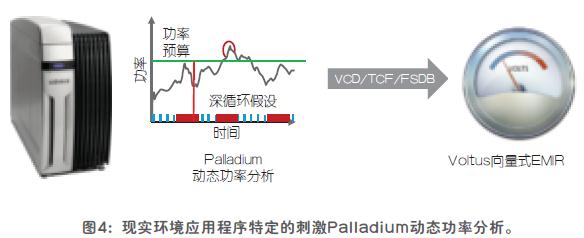

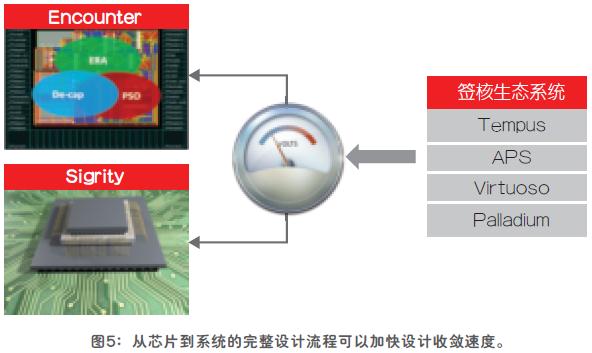

ФЪТЖ¶ҜјЖЛгКұҙъЈ¬Ж¬ЙППөНі(SoC)өДЙијЖТСҫӯұдөГёьОӘёҙФУЈ¬ТтОӘФЪЙијЖ№эіМЦРГжБЩЧЕЦо¶аМфХҪЈ¬ИзРиЧсСӯХл¶ФёЯј¶БчіМҪЪөгөДёҙФУЙијЖ№жФтЈ¬РиІЙУГөН№ҰВКөзВ·ЙијЖјјКхЈ¬Іў·ЕҙуөзВ·өДіЯҙзЎЈөзФҙНкХыРФКЗЙијЖ·Ҫ°ёДЬұ»іЙ№ҰЗ©әЛөД№ШјьТтЛШЦ®Т»ЎЈұҫОДҪйЙЬБЛТ»ЦЦРВөД№ӨҫЯЈ¬УлЖдЛыПЦУРјјКхПаұИҪПЈ¬ЛьІ»ҪцДЬҪ«өзФҙНкХыРФ·ЦОцУлЗ©әЛөДЛЩ¶ИМбёЯ10ұ¶Ј¬Н¬Кұ»№ДЬҙпөҪАаЛЖУЪјҜіЙөзВ·НЁУГДЈДвіМРт(SPICE)өДЧјИ·¶ИЎЈёГ№ӨҫЯҪ«Т»МЧНкХыөДЙијЖКөПЦәНЗ©әЛ№ӨҫЯХыәПөҪТ»ЖрЈ¬ТФұгёьәГөШҝЛ·юФЪЗ©әЛ№эіМЦРУцөҪөДМфХҪЈ¬ҙУ¶шКөПЦТөДЪЧоҝмөДЙијЖКХБІБчіМЎЈ јтҪй ОӘБЛВъЧгТЖ¶ҜјЖЛгөДёчЦЦТӘЗуЈ¬Ж¬ЙППөНіөДЙијЖұдөГФҪАҙФҪёҙФУЎЈЛжЧЕПы·СХЯҝӘКјЗанщёьРЎЗЙЎўРФДЬёьәГЎўөзіШРшәҪКұјдёьіӨөДЙиұёЈ¬ЙиұёЦРЛщК№УГөДРҫЖ¬ұШРлДЬМṩёь·бё»өД№ҰДЬЈ¬ёьөНөДДЬәДТФј°ёьРЎөДіЯҙзЎЈ¶ФЙијЖ№ӨіМКҰАҙЛөЈ¬ХвР©ұд»ҜТвО¶ЧЕЛыГЗФЪЙијЖ№эіМЦРұШРлФЛУГПИҪшөДөзФҙјјКх(АэИзөзФҙҝШЦЖҝӘ№Ш)ЎўФцјУЦӘК¶ІъИЁөДДЪИЭәН№ҰДЬ(АэИзДЈДв/»мәПРЕәЕәкЦёБо)ТФј°јхЙЩЙијЖФЈ¶И(АэИзөзФҙөзС№РЎУЪ1V)ЎЈБнТ»·ҪГжЈ¬ІъЖ·ЙПКРЦЬЖЪұдөГФҪАҙФҪ¶МЈ¬ТтҙЛФЪЙијЖЦЬЖЪөДЧоәуҪЧ¶ОЈ¬өзФҙЗ©әЛ¶ФіЙ№ҰҪ«ЙијЖ·Ҫ°ёЛНҪ»ЦЖФмАҙЛөЦБ№ШЦШТӘЎЈ ЦБҪсЈ¬ҝЙУГөДөзФҙЗ©әЛјјКхИФОҙДЬёъЙПҙҙРВөДІҪ·ҘЎЈАэИзЈ¬Т»ЦұТФАҙ¶оНвөДФЛРРКұјд¶јКЗ·Б°ӯЙијЖХЯГЗНкХы¶шИ«ГжөШҪшРРөзФҙНкХыРФ·ЦОцәНУЕ»ҜөДТ»ёцЖҝҫұЎЈИ»¶шЈ¬ПЦФЪУРТ»ЦЦРВ№ӨҫЯҝЙТФҪвҫцХвёцОКМвЈ¬ЛьАыУГПИҪшөДҙу№жДЈІўРРЛг·ЁәН·ЦІгҪб№№Ҫ«өзФҙНкХыРФ·ЦОцәНЗ©әЛөДЛЩ¶ИМбёЯөҪФӯАҙөД10ұ¶Ј¬Н¬Кұ»№ДЬҙпөҪАаЛЖУЪSPICEөДЧјИ·¶ИЎЈБнНвЈ¬ЧчОӘҙУРҫЖ¬өҪПөНіөДХыМЧБчіМЦРөДТ»Іҝ·ЦЈ¬ёГ№ӨҫЯНЁ№эМбёЯХыёцЙијЖЦЬЖЪөДЙъІъБҰ¶шјУЛЩЙијЖКХБІБчіМЎЈ ИХТжёҙФУөДІъЖ·ЙијЖШҪРиөзФҙНкХыРФ·ЦОцРВ№ӨҫЯ ІъЖ·ЙијЖөДёҙФУ¶ИФҪАҙФҪёЯЈ¬ІъЖ·іЯҙзФҪАҙФҪРЎЈ¬¶шЗТ¶ФІъЖ··ЦОцөДТӘЗуТІФҪАҙФҪёҙФУЈ¬ХвФцјУБЛНкіЙөзФҙНкХыРФ·ЦОцәНЗ©әЛЛщРиөДКұјдЎЈИз№ыК№УГЎ°ЖҪГжЎұЙијЖ·Ҫ·Ё°СЙијЖАӯЖҪіЙОӘёЯј¶ұрөДТ»ІгЈ¬ФтІ»ЧгТФ·ЦОцУөУРКэТЪКөАэөДі¬ҙу№жДЈЙијЖЎЈөұЗ°өДҪвҫц·Ҫ°ёЗчПтУЪҪ«ЙијЖ·ЦОц»®·ЦіЙУлЎ°өҘөг№ӨҫЯЎұ¶ФУҰөД¶аёцІҝ·ЦЈ¬ХвР©№ӨҫЯФЪЧјИ·РФ»тТЧУГРФ·ҪГжІўІ»ДЬҙпөҪёЯј¶Ж¬ЙППөНіөДТӘЗуЎЈ БнНвЈ¬УЙУЪөұЗ°өДҪвҫц·Ҫ°ёКЗК№УГөҘөг№ӨҫЯЈ¬ТтҙЛОЮ·ЁУРР§өШЖА№АөзФҙ¶ФКұРтКХБІөДУ°ПмЈ¬¶шКұРт¶ФөзФҙ(VDD)ИҙКЗЧоОӘГфёРөДЎЈҙЛНвЈ¬ёЯј¶ҪЪөгЙијЖјјКхј°јјЗЙ(ИзFinFET№ӨТХәНИэО¬РҫЖ¬(3D-IC)·вЧ°)ТІҙшАҙБЛРВөДМфХҪЎЈАэИзЈ¬ЛжЧЕFinFETЖчјюөДІҝК𣬻бТтОӘҙ№ЦұөзБч·ҪПтЎў№ҰВКГЬ¶ИФцјУөИТтЛШ¶шІъЙъРВөДөзЗЁТЖ№жФтЎЈ¶шЛжЧЕИэО¬¶СөюКҪРҫЖ¬өДІҝК𣬻бУРөзИИРӯН¬·ВХжөДРВРиЗуЎЈОӘБЛИГЙијЖ№ӨіМКҰГЗВъЧгЙПКРЦЬЖЪәНІъЖ·ЦКБҝөДПа№ШТӘЗуЈ¬РиТӘТ»ёцәӯёЗРҫЖ¬Ўў·вЧ°ТФј°ПөНіөДНкХыөзФҙНкХыРФ·ЦОц·Ҫ°ёЎЈ НкГАөДөзФҙНкХыРФ·ЦОц№ӨҫЯРиҫЯұёДДР©№ҰДЬЈҝ өұіцПЦ©йФцјУЎўОВ¶Иұд»ҜЈ¬»тХЯУЙУЪҫІМ¬әН¶ҜМ¬IRС№ҪөФміЙ№ӨЧчөзС№ПВҪөөИіЎҫ°КұЈ¬Т»ПоЙијЖҝЙДЬК§°ЬЎЈОЮВЫКЗ¶ФУЪКэ°ЩНтГЕј¶ЙијЖ»№КЗ¶ФУЪ¶аҝЕВгҫ§¶шСФЈ¬ДЬФЪЙијЖФзЖЪҪЧ¶ОҫН¶ФөзФҙәНIRС№ҪөФјКшҪшРРөчКФІўЦӨКөЖд·ыәПТӘЗуЈ¬КЗҪЪФјұҰ№уөДҝӘ·ўіЙұҫәНКұјдөД№ШјьЎЈ»»ҫд»°ЛөЈ¬ҫЎФзХТөҪРҫЖ¬ЙПөДЎ°ИИөгЎұУРЦъУЪ·АЦ№РҫЖ¬РФДЬПВҪө(Нј1)ЎЈ  ОӘБЛДЬёьәГөШЦ§іЦёЯј¶Ж¬ЙППөНіЙијЖЈ¬НкГАөДөзФҙНкХыРФ·ЦОц№ӨҫЯУҰҫЯұёТФПВ№ҰДЬЈә Ўс ДЬјЖЛгРҫЖ¬ЙПөД©йТФј°ҝӘ№ШәНДЪІҝәДДЬЈ» Ўс ДЬ¶ФөзФҙНшВзөДөзФҙНкХыРФҪшРР·ЦОц(IRС№ҪөјмІвј°өзЗЁТЖјмІв)Ј» Ўс ДЬҫНөзВ·ЦРИҘсоөзИЭөҘФӘәНөзФҙҝШЦЖҝӘ№ШөДЧојСіЯҙзәНІјЦГ·ҪКҪМṩҪЁТйЈ¬ҙУ¶ш¶ФЙијЖ·Ҫ°ёЦРөДОпАнКөПЦөзБчҪшРРУЕ»ҜЈ» Ўс ДЬЖА№АIRС№Ҫө¶Ф°ьАЁҫІМ¬КұРт·ЦОцФЪДЪөДЙијЖКХБІөДУ°ПмЎЈ АыУГФЪЙъІъ№эіМЦРТСөГөҪСйЦӨөДәНҫЯұёЗ©әЛЦКБҝөДЛг·ЁәНТэЗжЈ¬Cadence№«ЛҫҝӘ·ўіцБЛТ»ЦЦјИДЬёІёЗХыёцРҫЖ¬УЦДЬ№Лј°РҫЖ¬ЙПЛщУРөҘФӘөДРВРНөзФҙНкХыРФ·ЦОц№ӨҫЯ(јҙVoltusјҜіЙөзВ·өзФҙНкХыРФ·ЦОцҪвҫц·Ҫ°ё)Ј¬ёГ№ӨҫЯДЬМṩЙПКцЛщУР№ҰДЬЎЈЛьөД·ЦОцЛЩ¶ИұИЖдЛыН¬АаҪвҫц·Ҫ°ёҝм10ұ¶Ј¬Н¬Кұ»№МṩБЛАаЛЖУЪSPICEөДЧјИ·¶ИЎЈҙЛНвЈ¬МЁНе»эМеөзВ·ЦЖФм№Й·ЭУРПЮ№«Лҫ(TSMC)ТСҫӯНЁ№э16nmј¶FinFET№ӨТХ¶ФХвЦЦ№ӨҫЯөДРФДЬҪшРРБЛСйЦӨЎЈТтҙЛЈ¬№ӨіМКҰГЗҝЙТФПаРЕёГ№ӨҫЯДЬ№»ҝзФҪІ»Н¬өДЙијЖ№жФт¶шёшіцЧјИ·өД·ЦОцҪб№ыЎЈ ҙу№жДЈІўРРҙҰАнҝЙјУҝм·ЦОцЛЩ¶И УлПЦУРөДЖдЛыјјКхПаұИҪПЈ¬VoltusјҜіЙөзВ·өзФҙНкХыРФ·ЦОцҪвҫц·Ҫ°ёФЪРФДЬЎўЧјИ·¶ИәНЙијЖКХБІ·ҪГжҫщУРЛщМбёЯЎЈФЪРФДЬ·ҪГжЈ¬ёГ№ӨҫЯК№УГПИҪшөДҙу№жДЈІўРРЛг·ЁЈ¬ҙУ¶шК№·ЦОцЛЩ¶ИұИН¬АаҪвҫц·Ҫ°ёҝм10ұ¶ЎЈ ОӘБЛҪшТ»ІҪМеПЦХвЦЦ№ӨҫЯөДҝмЛЩ·ЦОцРФДЬЈ¬ПВГжҪ«ТФФзЖЪІвКФ°жҝН»§МṩөДО»УЪёЯј¶БчіМҪЪөгөДУөУРКэТЪКөАэөДі¬ҙу№жДЈЙијЖіЎҫ°ОӘАэЎЈФЪ¶ФХвСщөДі¬ҙу№жДЈЙијЖҪшРР·ЦОцКұЈ¬Из№ыФЛУГПЦУРөДЙъІъБчіМЈ¬·ЦІгөДҫІМ¬әН¶ҜМ¬өзФҙЗ©әЛРиТӘ10МмЧуУТІЕДЬНкіЙЈ»Из№ыІЙУГVoltusјҜіЙөзВ·өзФҙНкХыРФ·ЦОцҪвҫц·Ҫ°ёЈ¬ФтҝЙТФФЪ32ёцCPUЙПН¬КұҪшРР·ЦОцІЩЧчЈ¬ҪцәДКұ26ёцРЎКұҫНҝЙТФНкіЙ·ЦОц№ӨЧчЎӘЛЩ¶ИұИФӯАҙМбёЯБЛ10ұ¶ЧуУТЈ¬ТтҙЛҝЙТФМбЗ°Ҫ«ЙијЖ·Ҫ°ёЛНҪ»ЦЖФм(Нј2)ЎЈ  АҙҝҙТ»ёцҫІМ¬№ҰВК·ЦОцөД°ёАэЈ¬ФЪёГ°ёАэЦРІЙУГБЛТ»ёцФЪ40nmј¶ҪЪөгУөУР2700НтёцКөАэөДДЈДв/»мәПРЕәЕРҫЖ¬ЎЈИз№ыАыУГПЦУРөДЙъІъБчіМЈ¬ТӘНкіЙ·ЦОцҪ«РиТӘ58ёцРЎКұЎЈ¶шИз№ыАыУГVoltusјҜіЙөзВ·өзФҙНкХыРФ·ЦОцҪвҫц·Ҫ°ёЈ¬ФтҝЙФЪ8ёцCPUЙПН¬КұҪшРР·ЦОцІЩЧчЈ¬ҪцәДКұ6ёцРЎКұҫНҝЙТФНкіЙ·ЦОц№ӨЧчЈ¬ЛЩ¶ИМбёЯБЛ10ұ¶ЧуУТЈ¬ІўЗТІ»»бҪөөНЧјИ·¶ИЎЈ ёГ№ӨҫЯІЙУГБЛ·ЦІгҪб№№Ј¬¶шЗТ·ЦОцРФДЬЧҝФҪЈ¬ҝЙТФНЁ№эјЖЛг»ъНшВзҪшРРјЖЛг¶шЗТИЭБҝ·ЗіЈҙу(Чо¶аҝЙТФЦ§іЦ10ТЪёцКөАэ)ЎЈАэИзЈ¬Из№ыТ»МЁөҘ»ъЕдУР16ёцCPUЈ¬VoltusјҜіЙөзВ·өзФҙНкХыРФ·ЦОцҪвҫц·Ҫ°ёҝЙФЪХвР©CPUЙПН¬КұҪшРР·ЦОцІЩЧчЎЈИз№ыөҘ»ъөДКэБҝІ»Ц№Т»МЁЈ¬ГҝМЁөҘ»ъ¶јУР¶аёцCPUЈ¬¶шЗТХвР©өҘ»ъБ¬ҪУРОіЙБЛТ»ёцНшВзЈ¬ёГ№ӨҫЯИФИ»ҝЙТФК№УГЖд¶аПЯіМ·ЦІјКҪҙҰАнјјКхЦ§іЦҝмЛЩөзФҙ·ЦОцјЖЛгЎЈНЁ№э·ЦІг·Ҫ·ЁЈ¬№ӨіМКҰҝЙТФҪЁБўөзФҙНшВзДЈРНЈ¬ХвКЗЙијЖІгҙОЦРҪПөНІгөДІҝ·ЦЈ¬ДҝөДКЗ»сИЎЛщ№ШЧўөДөзФҙНшВзРЕПўЎЈХвТ»ДЈРНјхРЎБЛҙУ¶ҘІгЛщҝҙөҪөДҪЪөгЧЬКэЈ¬јшУЪҙЛЈ¬УлН¬АаҪвҫц·Ҫ°ёПаұИЈ¬№ӨіМКҰФЪ·ЦОц№эіМЦРҝЙТФФЛРРёь¶аөДЙијЖКөАэ(Нј3)ЎЈ  ФЪЙијЖКХБІ·ҪГжЈ¬Voltus№ӨҫЯФЪФзЖЪөЧІг№ж»®әНөзФҙ№ж»®ҪЧ¶О¶ФөзФҙ№мҪшРР·ЦОцЈ¬ТФұгНЁ№эІјПЯІјҫЦЎў№ӨіМұдёьЦёБо(ECO)әНРҫЖ¬УлПөНіөДРӯН¬ЙијЖ·ЦОцФЪОпАнЙП¶ФөзФҙНшВзҪшРРУЕ»ҜЎЈФЪЧјИ·¶И·ҪГжЈ¬VoltusјҜіЙөзВ·өзФҙНкХыРФ·ЦОцҪвҫц·Ҫ°ёІЙУГSPICEј¶өД№мҫШХуҪвЛг·ЁТФј°ҫ«И·өДөзФҙНшВзөзЧиөзИЭЭНИЎәНКөАэ№ҰВКјЖЛг/·ЦІјЎЈ№мҫШХуҪвЛг·ЁҪПОӘёҙФУЈ¬ҝЙТФФЪ·ЦІјФЪ¶аМЁЙиұёЙПөДјёК®ёцCPUЙПН¬КұҪшРРЈ¬МṩҙуРНөзФҙНшВзөДёЯЧјИ·¶ИДЈДвЎЈ ХыёцЗ©әЛБчіМөДТ»Іҝ·Ц VoltusјҜіЙөзВ·өзФҙНкХыРФ·ЦОцҪвҫц·Ҫ°ёКЗCadence№«ЛҫМṩХыёцЗ©әЛәНЙијЖКХБІБчіМөДТ»Іҝ·ЦЎЈёГ№ӨҫЯөДЧчУГУл¶АБўөДөзФҙЗ©әЛ№ӨҫЯАаЛЖЎЈө«ЛьјҜіЙБЛәЬ¶аЖдЛыЧйјюЈ¬ёшЙијЖ№ӨіМКҰГЗМṩБЛТ»ёцҙУРҫЖ¬өҪПөНіөД¶аІъҝмЛЩөДЙијЖКХБІБчіМЎЈ ФзЖЪөзФҙ№м·ЦОц ФЪҙ«НіөДЙијЖБчіМЦРЈ¬№ӨіМКҰІјНкПЯЦ®ә󣬻бҪшРРөзФҙЗ©әЛ·ЦОцЈ¬ТФЖА№АөзФҙНшВзЙијЖ·Ҫ°ёөДҝЙРРРФЎЈө«КЗЈ¬Из№ыФЪІјНкПЯЦ®әуІЕ¶ФЙијЖ·Ҫ°ёөДөзФҙНкХыРФҪшРР·ЦОцЈ¬¶шЗТФЪ·ЦОцЦ®әу·ўПЦБЛОКМвЈ¬ФтРиТӘәД·СёьіӨөДКұјдАҙҪвҫцОКМвЈ¬ЙхЦБҝЙДЬОЮ·ЁҪвҫцЎЈVoltusјҜіЙөзВ·өзФҙНкХыРФ·ЦОцҪвҫц·Ҫ°ёҝЙТФұЬГвЙПКцОКМвЈ¬ТтОӘЛьН¬Кұ»№јҜіЙБЛCadence EncounterКэЧЦКөПЦПөНіЈ¬К№ЙијЖ№ӨіМКҰГЗҝЙТФҪ«өзФҙНшВзЙијЖЕІөҪОпАнКөПЦөДФзЖЪҪЧ¶ОЎЈФзЖЪөзФҙ№м·ЦОцҝјВЗБЛөЧІг№ж»®РЕПўЈ¬ТФј°өзФҙНшВзҪрКфФӘјюөДҙуРЎәНО»ЦГЎЈИз№ы№ӨіМКҰұШРлҪ«БҪёц№ҰДЬЗшҝй·ЕөҪТ»Жр(¶шЗТБҪёцЗшҝйҫщК®·Ц»оФҫ)Ј¬ФтёГјҜіЙҪвҫц·Ҫ°ёҝЙТФМṩ№ШУЪИзәОКөПЦЧојСІјПЯөДЦёөјҪЁТйЎЈБјәГөДФзЖЪ№м·ЦОцҪб№ыҪ«»бНЖҪшөзФҙЗ©әЛЈ¬ёьҝмөШ»гҫЫЈ¬ҙУ¶шјУҝмЙијЖКХБІЎЈ ПЦКө»·ҫіЦРөД·еЦө№ҰВК·ЦОц Из№ыПсIRС№ҪөәНөзЗЁТЖХвСщөДөзФҙНкХыРФОКМвГ»УРөГөҪҪвҫцЈ¬ҝЙДЬ»бөјЦВ№и№КХПЎЈНЁ№эФЪПЦКө»·ҫіЦРҪшРРөзҙМјӨ·ЦОцҝЙТФМбёЯ·ЦОцҪб№ыөДЧјИ·РФЈ¬МШұрКЗФЪіӨКұјдДЪҝјБҝРҫЖ¬өДРРОӘЈ¬ТФј°ФЪ»оФҫ¶ИФцјУөДЗйҝцПВ№ЫІм·еЦө№ҰВКПыәД·ўЙъөДО»ЦГКұёьКЗИзҙЛЎЈ Cadence№«ЛҫPalladiumЖҪМЁМṩөДЎ°ЙоСӯ»·Ўұ¶ҜМ¬№ҰВК·ЦОц(DPA)№ҰДЬЦ§іЦФЪПЦКө»·ҫіЦРҪшРРөзҙМјӨ·ЦОцЈ¬өГТжУЪҙЛЈ¬Cadence Palladium·ВХжјјКхУлVoltusҪвҫц·Ҫ°ёөДҪбәПДЬ№»КөПЦёЯЧјИ·¶ИөДјҜіЙөзВ·өзФҙНкХыРФ·ЦОц(Нј4)ЎЈ  НіТ»өДөзЧУЗ©әЛ КұРт¶ФөзФҙЧоОӘГфёРЎЈТтҙЛЈ¬Из№ыөзФҙНшВзКөАэЦРИұ·ҰЧјИ·УРР§өДөзФҙЦөФт»бТэ·ўЙијЖ·А»ӨЖөҙшЈ¬ТІҫНФцјУБЛҫІМ¬КұРтЦРөДёәГжТтЛШЎЈУЙУЪVoltusјҜіЙөзВ·өзФҙНкХыРФ·ЦОцҪвҫц·Ҫ°ёјҜіЙБЛCadenceTempusКұРтЗ©әЛҪвҫц·Ҫ°ёЈ¬ЙијЖ№ӨіМКҰГЗҫНҝЙТФК№УГНіТ»өД№ҰВКәНКұРт·ЦОцКХБІПөНіЎЈјҜіЙҪвҫц·Ҫ°ёҪ«ҫІМ¬КұРт·ЦОцөДЧјИ·ВКМбёЯБЛ3ёц°Щ·ЦөгЈ¬јхЙЩБЛКұРтЦРөДёәГжТтЛШЈ¬ІўЗТФЪРҫЖ¬ЙПЙъіЙБЛёь·ыәППЦКөК№УГ»·ҫіөДС№ҪөЎЈ РҫЖ¬-·вЧ°-УЎЛўөзВ·°еРӯН¬·ВХжУл·ЦОц ОӘБЛ·АЦ№·вЧ°№эіМЦРөДИИұААЈТФј°ФЪРҫЖ¬ЙПәНФЪУЎЛўөзВ·°еҪЧ¶ОіцПЦөДЖдЛыөзФҙНкХыРФОКМвЈ¬ёГ№ӨҫЯјҜіЙБЛCadence Allegro SigrityјјКхЈ¬МṩРҫЖ¬-·вЧ°-УЎЛўөзВ·°еРӯН¬·ВХжУл·ЦОц№ҰДЬЎЈёГјҜіЙҪвҫц·Ҫ°ёМṩБЛХл¶ФөзФҙНшВзЦРРҫЖ¬әНөзВ·°еөДЧјИ··ЦОцЈ¬Н¬Кұ»№Ц§іЦПсИэО¬РҫЖ¬ДЗСщөДПИҪш·вЧ°јјКхЎЈНЁ№эН¬КұК№УГХвР©№ӨҫЯЈ¬№ӨіМКҰГЗҫНДЬ№»јУҝмПөНіј¶өзФҙНкХыРФ·ЦОцәНЗ©әЛөДЛЩ¶И(Нј5)ЎЈ  ЧЬҪб ёҙФУ¶ИёьёЯЎўәДКұёьіӨөДөзФҙНкХыРФ·ЦОцРиТӘІЙУГёьёЯР§өД·ЦОц№ӨҫЯЎЈИЛГЗ¶ФТЖ¶ҜУҰУГј°ОпБӘНшУҰУГөДРиЗу¶ФІъЖ·өДЙПКРЦЬЖЪәНРФДЬМбіцБЛёьёЯөДТӘЗуЎЈНЁ№эК№УГПИҪшөДҙу№жДЈІўРРЛг·ЁЎўҙуИЭБҝ·ЦОц(Чо¶аДЬЦ§іЦ10ТЪёцКөАэ)әН·ЦІгҪб№№Ј¬VoltusјҜіЙөзВ·өзФҙНкХыРФ·ЦОцҪвҫц·Ҫ°ёөДөзФҙЗ©әЛЛЩ¶ИұИН¬АаҪвҫц·Ҫ°ёҝм10ұ¶ЎЈёГҪвҫц·Ҫ°ёјҜіЙБЛЖдЛы№ШјьөДКұРт·ЦОцЎўОпАнКөПЦЎў·ВХжәН·вЧ°№ӨҫЯЈ¬РОіЙБЛТ»ёцЗ©әЛЙъМ¬ПөНіЈ¬ОӘТөҪзМṩБЛЧоҝмөДЙијЖКХБІБчіМЎЈ |

НшУСЖАВЫ