最大限度地提高缓冲器性能,修复保持时间违例

发布时间:2014-12-17 11:21

发布者:designapp

|

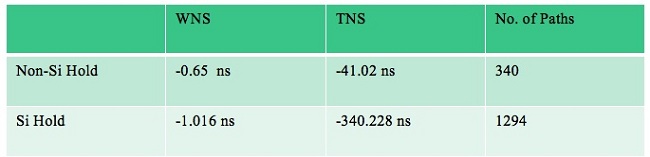

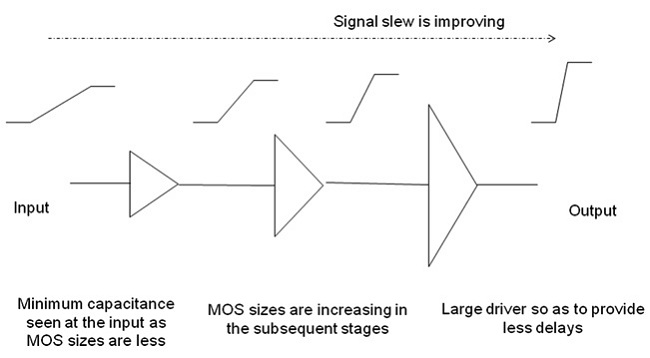

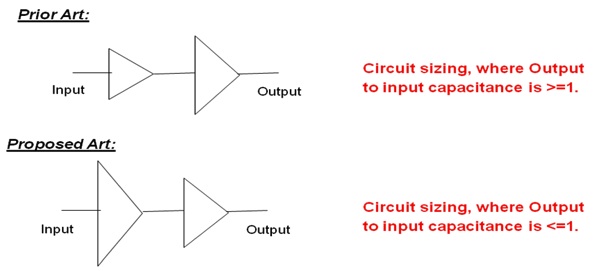

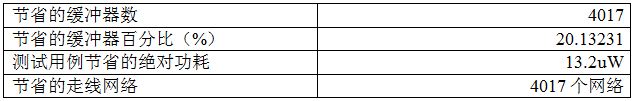

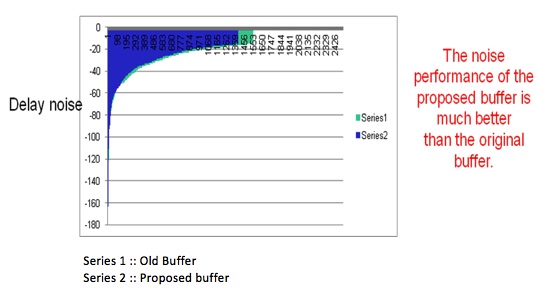

当前SoC(片上系统)设计的一大趋势是,集成电路变得越来越错综复杂,要满足所有设计要求变得越来越难以实现。噪声成为低端技术节点中的突出问题。当前SoC需要做到高抗扰度、实现低功耗设计并缩小芯片尺寸。虽然目前无法满足所有这些需求,但设计人员可以确保在不影响其它规格的情况下尽量满足所有这些需求。 在压缩技术中,任何SoC设计都能在多模多角情况下运行。因此满足所有角点的建立时间和保持时间是一个严峻的挑战。在设计上,保持时间违例关闭涉及Non-Si Hold关闭(由于时钟偏移)和Si Hold关闭(由于时钟和数据噪声)。减少现有逻辑缓冲器数或在路径中放置更多的保持时间缓冲器(主要为低驱动缓冲器),可以完成Non-Si Hold修复;而添加更多缓冲器,可以完成Si-Hold修复。 由于延时与驱动强度成反比,因此选择低驱动强度的单元,才会修复保持时间违例。这些缓冲器是驱动强度能力较低的常规缓冲单元。它们也有其自身的局限性,即更易产生噪声。如果有巨大的时序违例,则采用一连串的缓冲器,这样局部密度会变高。  表1. Si和Non-Si保持时间违例修复之比较 图字:No. of Paths:路径数 不同元件产生的噪声占比: 1) 20-25%来自时钟噪声 2) 50-55%来自逻辑数据路径 3) 15-20%来自设计中添加的保持时间缓冲器 因为存在这些缺点,我们才考虑采用一个新的缓冲架构,它能够满足保持时序,而不会对面积产生任何影响,同时具有高抗扰性。 级公比(Stage ratio)是设计缓冲器的决定因素。在任何缓冲器的传统设计方法中,级公比都大于1,也就是说,任何输出级的晶体管大小(扩散宽度W)都大于其输入级的,因而每个后续级的驱动能力超过其前一级,这样可确保任何缓冲单元有最小的延时。 传统缓冲单元设计方法 基本上,标准缓冲单元中每个电路都是多级结构。这意味着可以实现具有不同驱动强度的组合/时序单元,方法是通过该组合/时序元件的特定逻辑,再加一连串缓冲器(每一级都有一个公比)。 如图1所示,向输出级靠近时,晶体管的大小会逐级增加,从而确保每一级都可增强信号强度。采用这种配置,每一级都可实现良好的过渡,从而获得最佳延迟。而采用推荐方法,则朝相反方向移动时,延迟越大。但在我们推荐的设计中,我们将这一基本思路调转过来了,使级公比低于1,因为我们的目标是修复保持时间违例。这样做后,我们增加了缓冲单元延时,也提高了抗噪声能力。  图1. 传统缓冲单元设计 图字:Signal slew is improving:信号转换不断改善;Input:输入端;Output:输出端;Minimum capacitance seen at the input as MOS sizes are less:由于MOS尺寸变小,输入端可见最小电容;MOS sizes are increasing in the subsequent stages:MOS尺寸在随后的级别中不断增长;Large driver so as to provide less delays:较大驱动器,可提供较少延时  图2. 现有方法和推荐方法图示 图字:Prior Art:现有方法;Input:输入端;Output:输出端;Circuit sizing, where output to input capacitance is >=1 电路尺寸,输出与输入电容比>=1;Proposed Art:推荐方法;Input:输入端;Output:输出端;Circuit sizing, where output to input capacitance is <=1;电路尺寸,输出与输入电容比<=1 设计此缓冲单元期间,我们确保不影响其面积和功耗。由于推荐的缓冲单元有更高的延时,且对其面积没有任何影响,因而可以解决局部拥塞问题。 设计这种新架构的缓冲单元时,面积与传统缓冲单元的相同,但提供更多的延时。 整个设计是以修复保持时间违例为考虑重点的,能够以更少的新架构缓冲器实现相同的时序要求。所以,与采用传统缓冲器的设计相比,拥塞会更少。 设计结果 我们挑选一个设计,分别采用下列方式进行保持时间违例修复: 1) Run1:仅采用旧缓冲器。 2) Run2:采用新旧缓冲器(允许在任何设计中,推荐的保持时间缓冲器通过工具与库中现有的所有其它缓冲单元配合使用)。  表2. 旧缓冲器与推荐缓冲器之比较 设计中会有一些很小的保持时间违例,只能采用旧缓冲器才能修复,这是因为与推荐缓冲器相比,它提供的延时更少。例如,如果要修复10ps保持时间违例,使用推荐缓冲器会比旧缓冲器产生更多的延时。  表3. 设计结果分析 由于节省了20%的保持时间缓冲器,此设计的功耗和动态功率会整体下降。保持时间违例修复的走线开销由此降低了,局部拥塞问题也减少了。由于减少了所用的缓冲器数目,因而面积也省下来了。采用推荐缓冲器,可保持时序整洁。 旧缓冲器与推荐缓冲器的噪声性能。 采用上一张幻灯片的run1和run2中的值。  图3. 旧缓冲器和推荐缓冲器的抗噪声能力分析 图字:Delay noise:延时噪声;The noise performance of the proposed buffer is much better than the original buffer:推荐缓冲器的噪声性能比原来的缓冲器好很多;Series 1: Old buffer:系列1:现有缓冲器;Series 2: Proposed buffer:系列2:推荐缓冲器 图3中X轴表示带有噪声的违例路径的数量,Y轴表示噪声幅度。因此,该表显示,与系列2(新缓冲器)比较,系列1(旧缓冲器)有更高的噪声幅度和更多的路径。我们得出公平公正的结论:与旧缓冲器比较,采用推荐缓冲器,抗噪声能力会更好。 结论 基于上述分析,推荐缓冲器比现有缓冲单元更能有效地修复保持时间违例,具备高抗噪声能力,可节省面积、功耗和走线。一般来说,以最佳延时或低功耗结构为思路可以设计出标准缓冲单元电路。以前没有人在保持时间优化电路的背景下思考保持时间违例修复,因为速度,即高性能是需求,所以才会有糟糕的设计,通常,设计人员会以追求高性能为目标。 所有设计都可以采用推荐工艺架构。 以保持时间为重点考虑要素的设计或拥塞设计会从这个电路中获益颇丰,此外,还可以缩短任何SoC的周期。 参考文件 [1] Jan M. Rabaey, AnanthaChandrakasan, and BorivojeNikolic, Digital Integrated Circuits - A design Perspective (2nd Edition). [2] Ivan E. Sutherland, Bob F. Sproull, and David L. Harris, Logical Effort: Designing Fast CMOS circuits. |

网友评论