三星将推big.little技术八核处理器

发布时间:2012-11-23 11:03

发布者:李宽

|

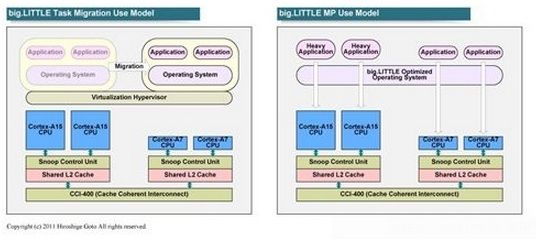

三星将在明年二月的国际电子电路研讨会(ISSCC)中,展示采用ARM big.little概念的移动应用处理器。 这是少数将在该会议大披露的新款微处理器,但包括英特尔的Haswell和Nvidia的丹佛计划(Project Denver),都很明显地缺席。不过,英特尔和Nvidia都将就新的芯片到芯片连接提出最新论文,展示他们对未来处理器的规划。 这种基于28纳米的八核ARM处理器将会由两部分组成:第一部分为1.8GHz主频的、四核Cortex-A15处理器,用来应付繁重的计算任务,如游戏、强度运算等,突出性能;;第二部分为1.2GHz主频的、四核Cortex-A7处理器,用来应对待机等较轻量级的任务。如浏览网页、听音乐等,注重功耗。 该芯片与ARM所提出之采用32位A15和A7核心的big.little 架构相同。今年10月时,ARM曾表示这种方法提供了比预期还要高的效益,未来将广泛应用在智能手机中。 Linley Group资深分析师Kevin Krewell表示,三星将推出首款big.little处理器。A7核心应该能处理大多数智能手机的任务,而A15核心则处理需要高性能的需求,如游戏。

而其他如高通(Qualcomm)、Nvidia和其他预计2013年推出,将与英特尔22nm Haswell在平板市场竞争的处理器则并未计划在ISSCC上披露。根据过去经验,英特尔在会议上提出的论文向来与处理器无关。 不过,这家x86巨擘将描述一款频宽达1Tb的可扩展64通道芯片到芯片互连。该链路使用多个2~16Gb/s通道,运行在0.8~2.6 pJ /bit,采用32nm CMOS制程,总线功耗为2.6W。 这篇文章介绍了英特尔研究院(Intel Labs)的研究成果。英特尔实验室资深首席工程师Bryan Casper表示,该论文描述了使用Samtec的micro-twinax线路,以及Ardent Concepts的连接器来连接Tb/s等级的芯片,否则功耗可能会拉升至20W。 Casper表示,直径1到2mm的线束将是“我们在跨越移动和服务器应用时,向前迈进的重要技术。次pJ /bit I/O非常重要,因为这是快速开启和关闭I/O连接的关键。” Nvidia将描述一款20Gb/s的串列芯片到芯片28nm CMOS,它采用0.9V电源,电源效率0.54pJ/b。这项互连技术可能会与Nvidia的丹佛计划整合,也可能应用在从笔电到超级本等所有ARM和图形核心处理器系列中。

此外,中国科学院计算技术研究所(ICT)将提出新版龙芯3B处理器(Godson 3B),该元件采用32nm。在此之前,ICT展示过八核心65nm CPU,并建议直接跨越到32nm。 在ISSCC上,工程师将详细介绍Godson-3B1500,这是一款32nm high-K金属栅极元件,在1.35 GHz、40W条件下可提供172.8 GFLOPS性能。在同等功耗条件下,新处理器性能较65nm版本的128 Gflops有显著提升,这主要归功于新制、架构和电路的改良。 在其他论文中,德州仪器(TI)和麻省理工学院(MIT)将提出一款200MHz的图像解码器,可符合高效影像编码标准,提供每秒249M像素性能。它支持3,840 × 2,160像素分辨率,在0.9V时耗电76mW。 瑞萨(Renesas)将描述一款整合手机芯片,其中包含28nm双核心1.5GHz CPU、 LTE/HSPA + 基频数据机处理器、绘图加速器和电源管理单元。AMD, IBM和甲骨文(Oracle)则将分别就其Jaguar, zSeries 和Sparc T5发表论文。 |

网友评论