英特尔ECTC大会披露封装技术突破:EMIB-T、散热革新与热键合工艺重塑芯片封装未来

2025年06月04日 11:18 发布者:eechina

6月3日,在电子元件技术大会(ECTC)上,英特尔披露多项芯片封装技术突破,涵盖EMIB-T、分解式散热器及新型热键合工艺三大核心领域,直指AI算力集群与异构集成芯片的封装瓶颈。这些技术不仅提升了芯片供电效率、散热能力及良率,更推动封装尺寸向120x180毫米迈进,为下一代HBM4内存及UCIe-A互连标准提供关键支撑。EMIB-T:突破供电与通信双重瓶颈,赋能HBM4集成

英特尔在大会上重点展示了EMIB-T技术,该技术通过将硅通孔(TSV)融入现有EMIB结构,实现芯片供电与通信的双重革新。传统EMIB设计因悬臂式供电路径导致高电压降,而EMIB-T通过TSV从封装基板底部直接供电,形成低电阻路径,显著提升供电效率。这一改进对HBM4/4e内存集成至关重要,结合UCIe-A互连技术,数据传输速率可达32 Gb/s以上。

此外,EMIB-T在桥接器中集成高功率金属-绝缘体-金属(MIM)电容器,有效补偿电压波动,确保信号完整性。该技术支持120x180毫米超大封装尺寸,可容纳24个内存堆栈、8个计算芯片及38个EMIB桥接器,凸块间距更从45微米缩小至35微米,并计划开发25微米间距。

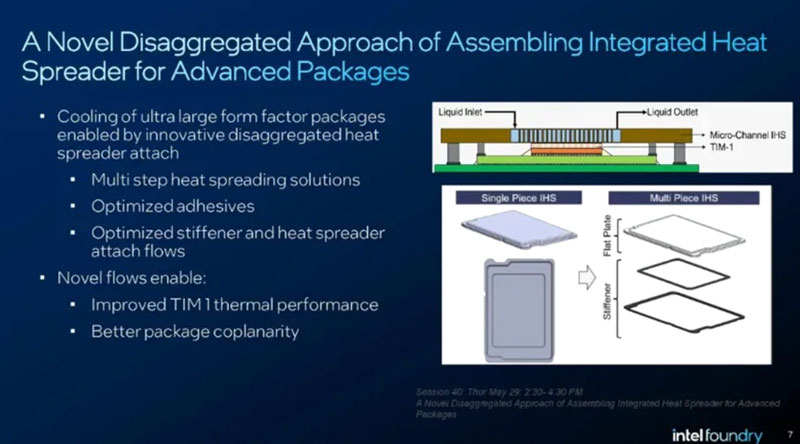

分解式散热器:冷却效能提升25%,应对千瓦级功耗挑战

针对AI芯片封装的高功耗散热难题,英特尔推出分解式散热器技术。该设计将散热器分解为平板与加强筋结构,优化与热界面材料(TIM)的耦合,减少TIM耦合焊料中的空隙达25%。实验数据显示,该技术可冷却TDP高达1000W的处理器封装,并集成微通道实现液体直接冷却,显著提升散热效率。

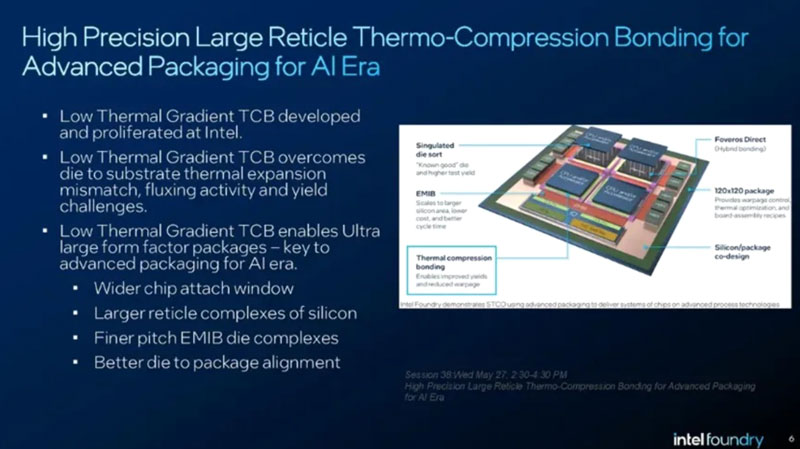

新型热键合工艺:消除翘曲,良率与密度双提升

为解决大型封装基板键合过程中的翘曲问题,英特尔开发了新型热压粘合工艺。该技术通过减少键合过程中的热差,将良率提升至行业领先水平,并支持更精细的EMIB连接间距。目前,该工艺已实现38个桥接器与12个裸片的集成,未来可进一步压缩凸块间距,提升封装密度。

技术生态协同:兼容有机/玻璃基板,拓展异构集成边界

英特尔强调,EMIB-T兼容有机与玻璃基板,其中玻璃基板因其高平整度与低热膨胀系数,成为未来封装的关键战略方向。这一兼容性使客户可将来自不同供应商的CPU、GPU、内存等芯片集成至单一封装,降低对单一工艺节点的依赖。目前,AWS、思科等企业已采用英特尔封装服务,涵盖美国政府的RAMP-C与SHIP项目。

行业影响:重构AI算力基础设施,竞逐台积电CoWoS

英特尔的封装技术突破与台积电CoWoS技术形成直接竞争。例如,EMIB-T的超大封装尺寸与高带宽互连能力,可支持单芯片封装集成超过10万GPU,为万亿参数大模型训练提供基础设施。据分析机构预测,先进封装技术将使AI训练成本降低30%-40%,加速超大规模AI集群的普及。

“AI基础设施的竞争已从单点技术转向系统级创新。”英特尔院士兼基板封装开发副总裁Rahul Manepalli表示,“EMIB-T不仅是封装技术的突破,更是AI算力集群的‘心脏’,它将推动单数据中心容纳百万张GPU成为可能。”