用FPGA避免微处理器过时

发布时间:2009-3-26 16:17

发布者:李宽

|

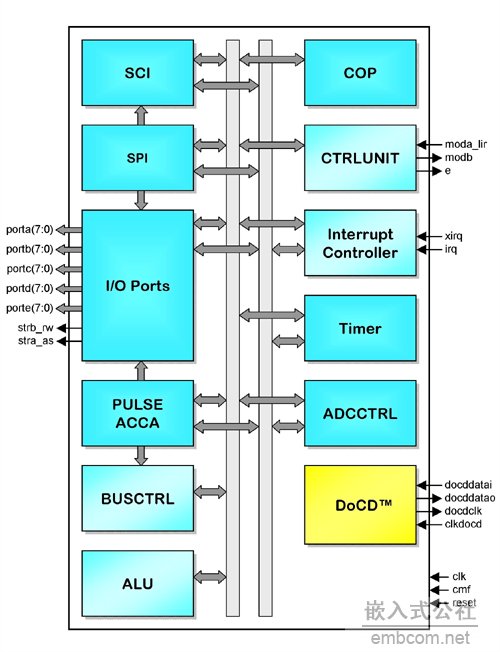

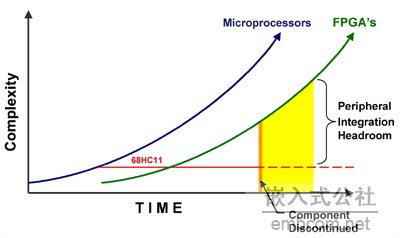

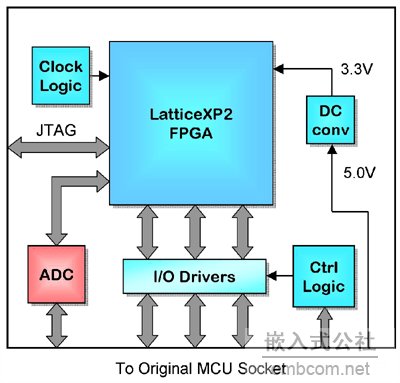

器件供应商降低制造成本的一个方法是中止老产品,这样做就导致微处理器过时。那些微处理器核的多个版本与集成外围器件的混合使情况更加复杂,对于特殊处理器的结构引起器件过剩。通过把外围设备整合至有微处理器的裸片,供应商可以把微处理器用于大批量的专门应用。(文中提到的“微处理器”指整个元件,包括处理器核与集成的外围设备)。由于应用和标准随着时间的推移而发展,微处理器设计的狭窄市场使得微处理器更加容易过时。本文阐述设计者面对微处理器(微控制器)过时的情况,采用FPGA的可选方案。 考虑这个选择之前,首先考虑FPGA作为应对微处理器过时的挑战是很有用的。例如LatticeXP2FPGA,可以实现68HC11兼容的CPU核,完全可综合的代码只要2600个slice。如图1所示的68HC11兼容的微处理器,把所有外设集成到这个器件将增加几百个slice。此外,容易适配至当今的FPGA,这个实现方案可以比原来的8-12 MHz 运行快5倍。  图1 实现D68HC11微处理器 技术曲线FPGA使设计者利用技术曲线,以防止微处理器的过时。外围设备,或者把它们组合在一起或许也会过时。除了处理过时的微处理器,针对把周围的功能整合到FPGA,FPGA技术曲线提供了选择。因此降低了整个系统的成本,并解除了对其它元件不能继续供应的担忧。基于SoC的微处理器和FPGA遵从的技术曲线如图2所示,用可综合的RTL,FPGA设计者免于受到将来器件过时的影响,在大批量ASIC的NRE里未提及。  图2 技术曲线增加了整合空间 图2中的技术曲线展示了微处理器和微控制器的相关等效逻辑复杂性与FPGA里软实现的比较。原来的微控制器过时的时候,可用的FPGA逻辑密度远多于实现微处理器和外设所需的逻辑。这个额外的逻辑称为外设整合空间,将随着FPGA密度继续增加而增长。图1中的D86HC11包括了DoCD块,提供了实时,非插入系统调试,以及没有整合到原来微控制器的功能。 FPGA提供了对设计的折衷方法,因此实现解决方案时设计者有多种选择。各种选择方案如下:选择方案1:完成再设计(将来验证设计) 在此方案中,器件供应商也许提供替代元件,或许不是相同的指令集结构(ISA)。这个选择需要完成硬件和软件的再设计,使用另外的基于元件的微处理器解决方案,或者基于FPGA的解决方案。如果选择这个方案,将来验证这个设计是理想的,采用开放源代码软处理器Harvard结构的32位LatticeMico32。不像GNU公用许可证(GPL),软件团体是相同的,用于LatticeMico32的创新开放源代码许可证是用硬件实现的。它可以移植到任何FPGA或者免费的ASIC。选择方案2:相同的ISA,较高的整合原来微处理器元件的软实现(μP核和集成外设)编程至FPGA。软处理器实现和外围设备比原来的元件运行速度高。采用这个选择,外设或者时序环有任何变化,软件只要做较小的改动。这个选择的优点是软件变化最小,降低了电路板的成本,因为电路板的其它功能都整合至FPGA。 选择方案3:二进制兼容,较高的整合 原来微处理器元件的软实现(μP核和集成外设)及精确的时序编程至FPGA。目标是用原始的二进制代码而不需要修改。通过整合其它电路板的功能至FPGA,这个选择降低了电路板的成本。 选择方案4:二进制兼容,插座兼容(典型方案) 这个选择使用中间层电路板实现FPGA,针对原来的微控制器,最小化相关的逻辑有准确的引脚对引脚的替换。除了中间层电路板之外,这个方法不用改变软件和硬件。例如,供应商停止68HC11MCU生产。对这个问题评估可能的方法,客户也许会规定替代的部件必须与原来的功能和时序一样,运行相同的二进制程序而无需修改。客户决定将DCD的D68HC11 IP核用在LatticeXP2FPGA中。LatticeXP2的片上Flash能用于较少部件的简单设计,见图3,因为非易失LatticeXP2不需要外部的Flash存储器,或者其它的电路下载FPGA配置。  图3 针对选择方案4的实现方案 最初客户考虑用完全不同的处理器代替68HC11,但是这个方法要求取代应用软件。这是一个很困难的任务,因为软件与68HC11指令和内部的外设紧密相关。因此转到新的处理器需要为软件的再设计付出大量的时间和精力。结果大多数解决方案是用FPGA取代68HC11。这个选择将专注FPGA里D68HC11 IP核的确认,避免改变系统的任何部分(软件应用,外部电路板元件),系统已完好地运行了15年多。 最重要的要求是能够得到与原来的微处理器完全兼容的软件。必须是运行在D68HC11上相同的二进制代码,对二进制代码的任何改变都是不可接受的。在这样的情况下,另外的限制是保持指令周期的精确性。这是很关键的,因为软件会使用指令循环构成的时序延时。此外,有些功能或外围接口也许会依赖精确根据指令和时钟周期确定的执行时间。使用这个方法时,很难达到外设兼容。然而在此情况,所有的数字部分都容易实现,并具有相同的功能和时序。大多数现成的IP核都是设计好的,并在DCD核库中验证过。 通常的问题是替代微控制器的模拟元件,例如模数转换器(ADC),上电/电源故障复位产生和时钟振荡器。数字可编程器件FPGA可以实现与这些功能相关的任何数字接口逻辑,但不是模拟电路。 用FPGA取代先前整合的ADC数字功能是可能的。采用外部ADC转换器和设计D68HC11接口是必须的。因为目前没有ADC具有和原来的元件有相同的精度,要选择性能好的。要求是有寄存器功能,与原来的ADC接口相同,包括ADC和CPU之间控制和状态信号的翻译。转换时序必须是相同的。这是ADC接口的主要功能,D68HC11的附加模块在FPGA中实现。 因此,用FPGA、ADC、时钟发生器和PLCC插座取代了老的器件,构成了小的印刷电路板并直接与客户的系统相连。对原来的电路板无需开发软件或改变。 用这个FPGA实现的大多数IP核源于DCD库,且已完全经过验证。任何新的外设都要设计成与68HC11的要求相匹配。对照旧的外设时序和功能,要仔细地验证新的外设。对验证来说FPGA是理想的,可以在FPGA中立即验证改变的HDL。 结论 本文中我们强调了微处理器的过时问题。提出了基于FPGA的选择方案,向涉及到过时微处理器问题的设计者提出了基于FPGA的选择,提供了将来验证需要微处理器的新设计方法。说明了FPGA如何针对过时问题的解决方案,以及整合功能、降低电路板成本的一些选择,并提高了调试设计的可见性。 |

网友评论