FPGA实战演练逻辑篇54:VGA驱动接口时序设计之1概述

发布时间:2015-7-26 21:35

发布者:rousong1989

|

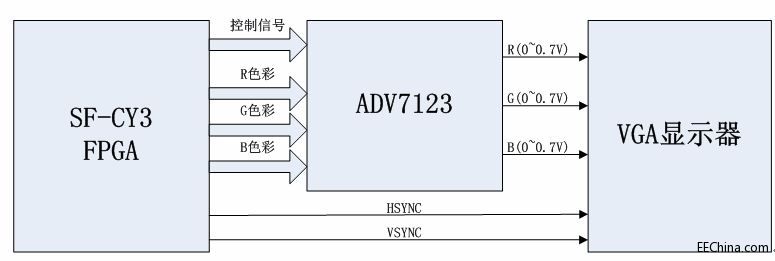

VGA驱动接口时序设计之1概述 本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》 配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt 第六章第8节中我们给出了VGA/SVGA显示驱动设计的实例,而那里所涉及的ADV7123芯片的驱动接口便是一组典型的FPGA输出接口。对于FPGA设计而言,这些输出接口需要进行reg2pin的时序约束,本节我们就通过这个VGA接口时序的分析来分析reg2pin路径。(特权同学,版权所有) 我们可以先回顾一下第三章中给出的VGA驱动实例的硬件接口框图。如图8.22所示,在这个框图中,我们主要分析FPGA器件和ADV7123芯片之间的接口,即图中所示意的控制信号、R色彩、G色彩和B色彩。ADV7123的控制信号即同步时钟lcd_clk和转换数据有效指示信号adv7123_blank_n;色彩信号即lcd_r[4:0]、lcd_g[5:0]和lcd_b[4:0]。(特权同学,版权所有)

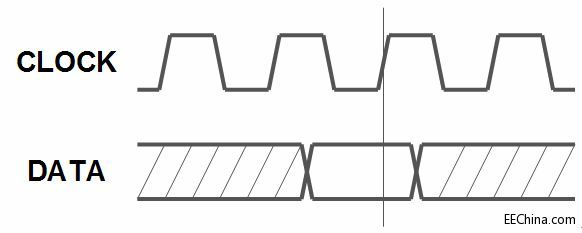

图8.22 VGA驱动实例硬件接口框图 要对上述输出信号的时序进行约束,使其满足设计要求,就必须先参考ADV7123芯片的datasheet,了解它的一些基本时序关系和时序参数,然后把这些时序信息套入前面给出的基本的reg2pin模型中进行分析。(特权同学,版权所有) 对于ADV7123来说,在它的输入引脚上,理想的时钟和数据波形如图8.23所示。在驱动时钟lcd_clk信号的上升沿,将对所有的数据和控制信号进行锁存。(特权同学,版权所有)

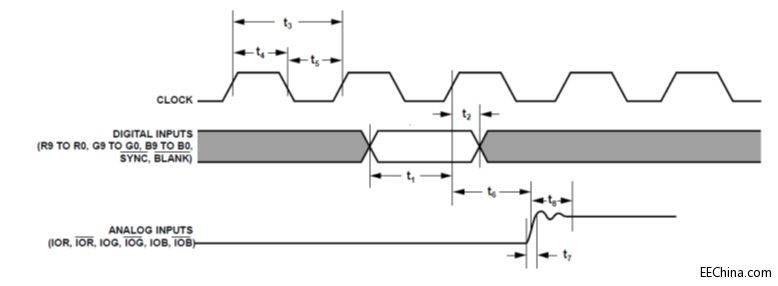

file:///C:/Users/pc/AppData/Local/Temp/msohtmlclip1/01/clip_image002.gif 图8.23 ADV7123理想的时钟和数据时序波形 我们还要进一步关心这些数据锁存时,时钟信号所需要的数据建立时间和保持时间是否满足要求。再来看图8.24,这里所示意的t1其实就是数据的建立时间,而t2则是数据的保持时间。(特权同学,版权所有)

图8.24 ADV7123数据传输的建立时间和保持时间 从对应的时序表中,我们找到了t1>0.2ns,t2>1.5ns这样的信息。 表8.1 ADV7123时序参数表

|

网友评论