FPGA实战演练逻辑篇21:引脚分配规划和扩展IO电路

发布时间:2015-5-6 11:09

发布者:rousong1989

|

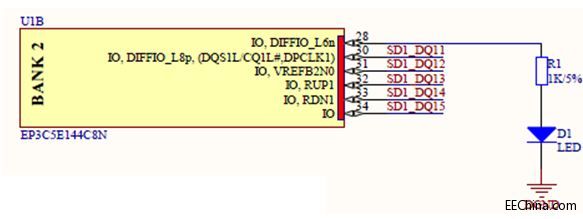

引脚分配规划和扩展I/O电路 本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》 配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt 核心板上专门留了一个LED指示灯连接到FPGA引脚上,用于板子的测试。I/O_28输出高电平LED将被导通点亮,低电平LED截止则不亮,其电路如图3.41所示。(特权同学,版权所有)

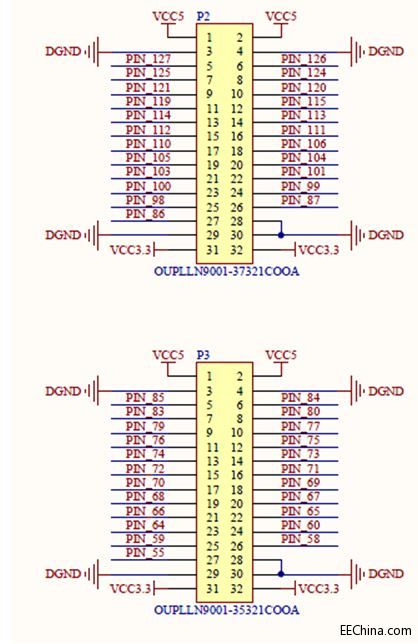

图3.41 连接FPGA引脚的LED驱动电路 如图3.42所示,该板子通过两个32PIN的连接器将46个I/O脚引出。每个连接器都有可用的23个I/O。电源5V/3.3V/GND也都引出扩展。具体的引脚定义和使用在后续每个子板的介绍中将会详细的定义和说明,其实这也是FPGA的I/O引脚灵活的体现,对于一般的信号,FPGA的I/O可以随意的连接。(特权同学,版权所有)

图3.42 核心板引出的两个插座电路 |

网友评论