дкЕЭГЩБОFPGAжаЪЕЯжЖЏЬЌЯрЮЛЕїећ

ЗЂВМЪБМфЃК2010-3-25 08:22

ЗЂВМепЃКРюПэ

|

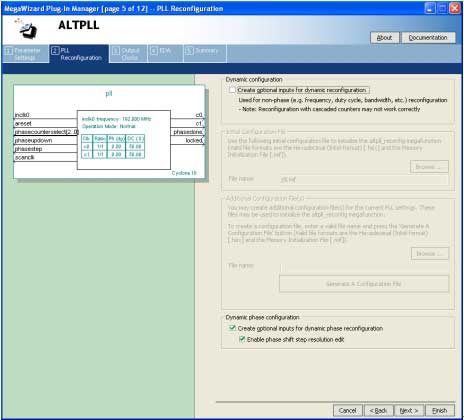

дкFPGAжаЃЌЖЏЬЌЯрЮЛЕїећ(DPA)жївЊЪЧЪЕЯжLVDSНгПкНгЪеЪБЖдЪБжгКЭЪ§ОнЭЈЕРЕФЯрЮЛВЙГЅЃЌвдДяЕНе§ШЗНгЪеЕФФПЕФЁЃ ALTERAЕФИпЖЫFPGAЃЌШчSTRATIX(r) ЯЕСажаздДјгаDPAЕчТЗЃЌЕЋЕЭЖЫЕФFPGAЃЌШчCYCLONE(r)ЯЕСажаЪЧУЛгаЕФЁЃБОЮФжївЊВћЪіШчКЮдкЕЭЖЫFPGAжаЪЕЯжетИіDPAЕФЙІФмЁЃ ЪЕЯжМмЙЙ дкLVDSЪфШыНгЪеЪБЃЌЪБжгКЭЪ§ОнЕФЯрЮЛПЩФмЪЧВЛШЗЖЈЕФЃЌвђДЫЮвУЧашвЊНЋЪБжгЕФЯрЮЛзїГіЕїећЃЌЪЙЕУЪБжгФмЮШЖЈЕФВЩМЏЕНЪфШыЪ§ОнЁЃЙЄзїЕФКЫаФОЭЪЧгУЫјЯрЛЗPLLЕФЯрЮЛЕїећЙІФмЃЌВњЩњШєИЩИіЪБжгЕФВЛЭЌЯрЮЛЃЌПДФФаЉЯрЮЛФмзМШЗЕФВЩМЏЕНЪфШыЪ§ОнЃЌШЛКѓШЁДАПкжаМфЕФвЛИіЪБжгЯрЮЛЃЌзїЮЊе§ГЃЙЄзїЪБЕФВЩбљЪБжгЁЃБШШчЭЈЙ§PLLВњЩњ0ЃЌ45ЃЌ90ЃЌ135ЃЌЁЁЃЌ315ЖШ8ИіЯрвЦЕФЪБжгЃЌШчЙћ0ЃЌ45ЃЌ90ЖШЯрвЦЕФЪБжгФме§ШЗВЩбљЕНЪфШыЃЌФЧУДзюКѓбЁШЁжаМфЯрЮЛЃЌМД45ЖШЕФЪБжгзїЮЊВЩбљЪБжгЁЃетбљНгПкЩЯОпгазюДѓЕФЪБађдЃСПЃЌДгЖјБЃжЄСДТЗЕФПЩППадЁЃЭМ1ЮЊетИіЩшМЦЕФЛљБОНсЙЙЃЌЭЈЙ§PLLЕїећЯрЮЛЕФНгПкЃЌВњЩњСЫЪБжгЕФВЛЭЌЯрЮЛРДВЩМЏЪ§ОнЃЌзюКѓбЁдёвЛИізюКЯЪЪЕФЯрЮЛЁЃ CYCLONEЯЕСаЕФPLLЕФЯрЮЛЕїећНгПкЪБађШчЭМ2ЫљЪОЃЌЕБгУЛЇТпМПижЦphasestep, phasecounterselectгыphaseupdownаХКХЪБЃЌPLLЕФЪфГіЪБжгC0ОЭИФБфвЛДЮЯрЮЛЁЃдкQIIЩњГЩPLLЪБЃЌгУЛЇБиаыбЁЩЯ create optional inputs for dynamic phase reconfigureЃЌЗёдђШБЪЁЪЧВЛЛсгаетаЉЙмНХЕФЃЌШчЭМ3ЫљЪОЁЃСэЭтБиаыдкoutput clock tabжааДШыphase shift step resolutionЕФжЕЃЌетбљВХФмШЗЖЈУПДЮЯрЮЛЕїећЕФВНГЄЁЃ гІгУЪЕР§ БОР§жаЕФВЮПМЩшМЦВЩгУCYCLONE3ЦїМўЃЌгыADIЙЋЫОЕФADS5277НгПкЃЌвбОдкгВМўЩЯВтЪдЙ§ЃЌжЄУїЪЧгааЇЕФЁЃADS5277ЪЧвЛПю8ЭЈЕРИпЫй ADCаОЦЌЃЌжївЊгУгкГЌЩљЩшБИвдМАВтЪдЩшБИжаЁЃЭМ4ЪЧИУВЮПМЩшМЦЕчТЗПђЭМЁЃ ADS5277ЫЭЕНFPGAЕФЪЧвЛИі192MHz ЕФЪБжгЃЌ8ТЗLVDSЪ§ОнЃЌЫйТЪЪЧ384MbpsЁЃЩЯЕчИДЮЛКѓADS5277ЗЂЫЭЕФЪ§ОнЪЧЁЎ0101010101ЁЁЁЏЃЌFPGAЦєЖЏDPAЕчТЗЃЌзМШЗШЗЖЈЪБжгЯрЮЛКѓдйЭЈЙ§ПижЦаХКХЃЌЪЙЕУADS5277ЗЂЫЭЁЎ000000111111ЁЁЁЏетбљЕФPATTERNЃЌFPGAПЩвдШЗЖЈзжЕФБпНчЃЌетвЛВНГЩЙІвдКѓЃЌFPGAОЭПЩвдЭЈЙ§ПижЦаХКХШУADS5277ЗЂЫЭе§ГЃЙЄзїЪБЕФЪ§ОнЃЌвђЮЊОЙ§СЫЪБжгЯрЮЛЕїећетвЛЙ§ГЬЃЌвдКѓЕФЪ§ОнВЩбљЪЧЗЧГЃЮШЖЈЕФЃЌВЛЛсЪмЕНЮТЖШЕчбЙБфЛЏРДЕФгАЯьЁЃ ЕБШЛетИіЩшМЦПЩвдКЭЫљгаLVDSЗЂЫЭаОЦЌНгПкЃЌВЂВЛжЛЯогкADS5277ЁЃЩѕжСПЩвдгІгУгкALTERAИпЖЫFPGAжаЃЌБШШчSTRATIX4ЕФДјгаDPA зЈгУЕчТЗЕФЙмНХжЛЗжВМдкзѓгвBANKЃЌЖјгУЕНетИіЩшМЦЕФЛАЃЌЩЯЯТBANKЕФIOвВФмЪЙгУЁЃDPAЩшМЦЫљЯћКФЕФТпМзЪдДЪЧЗЧГЃаЁЕФЃЌбЁгУЦїМўЮЊ 3C16F256C8, ШчБэ1ЫљЪОЁЃ

ЭМ1ЁЂдкFPGAжаЪЕЯжDPAЩшМЦМмЙЙЁЃ

ЭМ2ЁЂPLLЕФЯрЮЛЕїећНгПкЪБађЁЃ

ЭМ3ЁЂ

ЭМ4ЁЂВЮПМЩшМЦЕчТЗПђЭМЁЃ Бэ1ЁЂзЪдДЯћКФ

зїепЃКAlteraЙЋЫО СжБѓ ВЬКЃФў РДдДЃКAlteraЙЋЫО |

ЭјгбЦРТл