基于Actel FPGA的多串口扩展方案

发布时间:2010-3-17 18:54

发布者:李宽

|

随着现代电子技术的发展,接口技术在设计中占据越来越重要的地位。多串口动态扩展通信技术在现场工业控制、智能家居等领域应用越来越广泛。在当前的多串口的扩展应用中,虽然市面上有部分的多串口扩展芯片,但是其可扩展的串口数量有限并且扩展的个数是固定的,而且这些扩展芯片普片存在着价格比较昂贵、芯片体积较大在电路板中占据很大的空间,功耗过高等问题。 基于Actel FPGA的多串口扩展设计采用了Actel公司高集成度,小体积,低功耗,低系统成本,高安全性和可靠性的小容量FPGA-A3P030 进行设计,把若干接口电路的功能集成到A3P030中,实现了三路以上的串口扩展。该设计灵活性高,可根据需求灵活实现并行总线扩展三路UART或者 SPI扩展三路UART,波特率可以灵活设置。 1. 系统概述 本系统实现的UART扩展功能全部在具有3万门逻辑单元的小容量低成本的A3P030上实现。采用A3P030的通用I/O模拟SPI接口或者并行总线接口,实现SPI接口或者并行总线接口到UART接口的功能转换,同时在A3P030上实现UART串行收发单元的设计,最终实现不同接口到多路 UART扩展的功能。系统设计及应用框图如图 1所示。

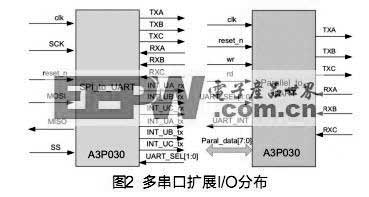

基于Actel A3P030的多串口扩展具有如下的功能及特点。 ● 系统电源为1.5V的A3P030内核电压和3.3V的I/O电压; ● 扩展的UART具有1位起始位,8位数据位,无校验位,1位停止位; ● UART双缓存锁存接收/发送数据; ● 波特率可以设置; ● 可实现基于SPI或者并行总线的UART扩展; ● 可实现并行总线扩展的中断查询; ● UART串行输入滤波; ● SPI串行输入滤波; ● 兼容标准的UART、SPI等通信协议。 基于Actel的 A3P030的多串口扩展设计除了具有高度的设计灵活性以外,还可以大大缩短产品的设计周期,加快产品上市速度。该设计方案所具有以下的优势:设计采用Actel公司的FPGA来实现,具有高度的可靠性和安全性,满足恶劣环境工作条件;完美的单芯片解决方案,Actel公司的FPGA无需配置芯片,上电即行;超低功耗,小封装。 基于Actel FPGA的多串口扩展在现代设计中主要有以下几个方面的应用: ● 电信网络:路由器、服务器等; ● 现场工业控制系统,电力抄表等; ● 智能家居控制系统,POS系统等。 2. 引脚定义 基于Actel A3P030设计的多串口扩展I/O分布如图2所示,其中左侧为基于SPI接口扩展多路UART的引脚分布,右侧为基于并行接口的多路UART扩展的I/O分布。

基于Actel A3P030的SPI接口扩展三路UART的I/O功能定义如表 1所示。

基于Actel A3P030的并行总线接口扩展三路UART的I/O功能说明如表2所示。

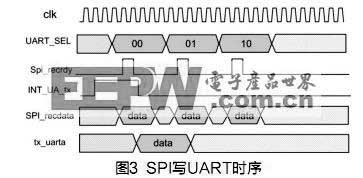

3. 时序操作 (1) 基于SPI的读写 本设计的SPI扩展多路UART中,SPI读写操作与标准的SPI从设备的读写方式是完全一致的,设计采用时钟上升沿发送数据,下降沿采集数据的方式(CPOL=0,CPHA=1)。SPI写A串口的操作时序如图3所示。

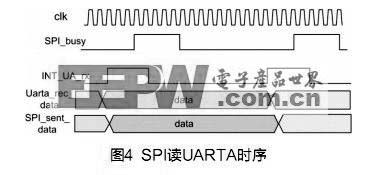

SPI读取UART接收完成的帧数据时序比较简单,主要是在SPI空闲状态时(SPI设备既不发送也不接收数据的状态),当UART帧接收完成标志信号有效时把UART接收完成后的并行数据传递到SPI发送寄存器。SPI读UART时序如图4所示。

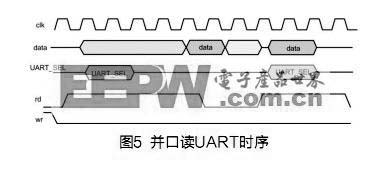

(2) 基于并行总线的读写 基于并行接口的多串口扩展设计中,并行总线采用的是Intel总线时序。并口读取UART接收寄存器的时序如图 5所示。在读操作时,首先根据中断信号来读取中断寄存器的数据并判定产生中断的是哪路UART,然后再读取数据。读信号至少有效五个时钟周期的时间,两次读操作的时间间隔必须大于两个时钟周期的时间,才能保证数据读取正确。

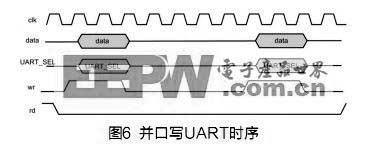

并行接口写UART如图6所示。在并行接口写UART发送寄存器时,写脉冲至少保持一个时钟周期,在写脉冲的上升沿过后,地址、数据和UART 的片选信号必须至少保持一个时钟周期。且两个相邻的写操作之间必须间隔5个以上的时钟周期,这样才能确保数据能正确写入寄存器中。另外,写UART发送寄存器前必须进行中断查询,中断数据有效后就读取中断数据并进行判断,然后进行写操作。

在并口写UART的时序中,clk为系统的时钟,uart_sel为UART片选信号,当uart_sel=00时为选择写入A串口,当 uart_sel=01时为选择写入B串口,当uart_sel=10时为选择写入C串口。wr是写信号,高电平有效,由于采用了双向的I/O设计,并口不能同时进行读写,因此在写信号有效的时候,读信号rd必须置为低电平的无效状态。 4. 小结 本文主要介绍了基于Actel A3P030的多串口扩展设计,可实现并行总线或SPI接口的UART扩展,该方案具有体积小、低功耗、低系统成本、高度可靠性和安全性以及高度的设计灵活性等特点,是在多串口应用中取代其他花费高昂成本的专用UART扩展芯片的最佳解决方案。我们有着一个接近30人的FPGA团队提供强有力的售后服务和技术支持,解决用户在产品使用和研发过程中遇到的困难。若有更多的需求可以与我们联系,我们将会竭诚为您服务,敬请关注下期的FPGA专题技术讲座。 来源:电子产品世界 2010-03-17 |

网友评论