用单片机实现SRAM工艺FPGA的加密应用

发布时间:2010-2-27 12:29

发布者:qgq

在现代电子系统设计中,由于可编程逻辑器件的卓越性能、灵活方便的可升级特性,而得到了广泛的应用。由于大规模高密度可编程逻辑器件多采用 SRAM工艺,要求每次上电,对FPGA器件进行重配置,这就使得可以通过监视配置的位数据流,进行克隆设计。因此,在关键、核心设备中,必须采用加密技术保护设计者的知识产权。

1 基于SRAM工艺FPGA的保密性问题 通常,采用SRAM工艺的FPGA芯片的的配置方法主要有三种:由计算机通过下载电缆配置、用专用配置芯片(如Altera公司的EPCX系列芯片)配置、采用存储器加微控制器的方法配置。第一种方法适合调试设计时要用,第二种和第三种在实际产品中使用较多。第二种方法的优点在于外围电路非常简单,体积较小,适用于不需要频繁升级的产品;第三种方法的优点在于成本较低,升级性能好。 以上几种方法在系统加电时,都需要将配置的比特流数据按照确定的时序写入SRAM工艺的FPGA。因此,采用一定的电路对配置FPGA的数据引脚进行采样,即可得到配置数据流信息。利用记录下来的配置数据可对另一块FPGA芯片进行配置,就实现了对FPGA内部设计电路的克隆。典型的克隆方法见图1。 2 对SRAM工艺FPGA进行有效加密的方法 由于SRAM工艺的FPGA上电时的配置数据是可以被复制的,因此单独的一块FPGA芯片是无法实现有效加密的。FPGA芯片供应商对位数据流的定义是不公开的,因此无法通过外部的配置数据流信息推测内部电路。也就是说,通过对FPGA配置引脚的数据进行采样可得到配置信息。但也不能知道内部电路结构。如果在配置完成后使FPGA处于非工作状态,利用另外一块保密性较强的CPU产生密码验证信息与FPGA进行通信,仅在验证成功的情况下使能 FPGA正常工作,则能有效地对设计进行加密。具体电路结构见图2。

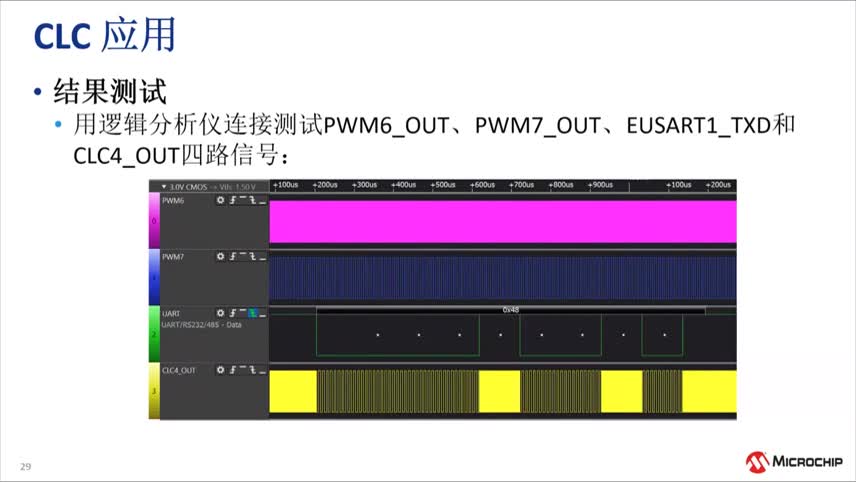

系统加电时,由单片机对SRAM工艺的FPGA进行配置。配置完成时,FPGA内部功能块的使能端为低,不能正常工作。此时,单片机判断到配置完成后,将 ASET信号置为高电平,使能FPGA内的伪码发生电路工作;同时,单片机产生一个伪码验证信息,在FPGA中将两路伪码进行比较,两者完全匹配时,FPGA内部电路正常工作,否则不能正常工作。加密电路主要利用了配置完成后处于空闲状态的单片机和FPGA内部分逻辑单元,没有增加硬件成本。 由上述讨论可知,系统的加密能力主要由CPU的加密能力决定。这就要求CPU的加密算法要足够复杂,使得对验证信息的捕获与识别足够困难。最常见的加密算法就是产生两个伪随机序列发生器:一个位于SRAM工艺的FPGA内;另一个位于CPU内。当两者匹配时,通过验斑点。对PN码有两点要求:一方面,要求伪随机序列的长度足够长,使得要捕获整个序列不太可能;另一方面,伪随机序列的线性复杂度要足够高,使推测伪随机序列的结构不易实现。 通常采用的伪随机码发生器的反馈电路如图3所示。实际中,可采用级数较高的线性反馈移位寄存器来产生伪随机码。如采用40级线性移位寄存器产生的最大序列的周期为2 40=10 12。若将所有伪随机码截获并存储,就需要1000Gb的存储空间;若码速率为50Kbps,捕获时间将长达5555小时;当增加移位寄存器的级数时,所需的存储空间和捕获时间都会呈指数增长,以至于难以实现。采用较为简单的线性反馈电路被推测出反馈结构的可能性较大,因此实际的系统中,除了级数要较多之外,往往通过对多个线性移位寄存器产生的伪码进行特定运算产生长码,以增加所产生伪码的线性复杂度。

3 FPGA内的校验工作电路 在此采用40级线性反馈移位寄存器来产生伪随机码,特征多项式为20000012000005(八进制表示)。其移位寄存器表示形式为:Bin=B23 XOR B21XORB2XORB0 FPGA内工作电路见图4。 在上电之后,单片机将图4中的电路配置在FPGA中。配置完成后,单片机发送的ASET信号由低电平跳变为高电平,使得FPGA内的PN码产生电路开始工作,并于CPU发送过来的PN码进行比较。比较结果一致就使能USER_DESIGN模块正常工作。其中PLL_BITSYS模块用来发生 VERIFY_PN的位同步时钟,采用微分锁相原理实现。各种参考资料都有较多介绍,在此不再详述。 COMPARE_PN模块完成对单片机发送的伪随机码和PNMA_PRODUCER模块产生的伪随机码的比较:当两路相同,输出1,不同时输出 0;若两路伪码完全匹配,则恒定输出1,使USER_DESIGN电路正常工作,否则,输出为类似于伪码的信号,使USER_DESIGN电路不能正常工作。 4 FPGA内的伪随机码产生电路 PNMA_PRODUCER模块和来产生伪随机码,采用移位寄存器实现,具体电路见图5。 LPM_SHIFTREG为移位寄存器模块。移位寄存器ASET端为异步置位端,高电平有效,即ASET为高时,将初值85置入移位寄存器内,LPMSHIFTREG模块的“DIRECTION”设置为“RIGHT”即移位方向为右移。Q[39..0]表示40位移位寄存器的各个状态,SHIFTIN为串行输入,SHIFTIN为Q0、Q2、Q21、Q23四个状态异或运算的结果。 图4 系统加电时,单片机将ASET置为低电平,经过一个非门,变成高电平使移位寄存器处于置位状态。在配置完成后,单片机将ASET信号置为高电平,经非门使移位寄存器正常工作。 利用移位寄存器电路产生伪随机码的电路非常简单,反馈逻辑也便于修改。 5 单片机验证伪码的程序 在位寻址区(20H~2FH)定义了字节变量WORD1、WORD2、WORD3、WORD4、WORD5,用来存储移位寄存器的40个状态。其中Q0对应WORD1.0,Q1对应WORD1.1……Q39对应WORD5.7。同时,在位寻址区定义了WORD6、WORD7、WORD8、 WORD9,用来进行后面的反馈逻辑计算。 单片机一上电,首先将ASET脚清零,同时,也将PNMA脚清零,将初值55H作为移位寄存器的初始状态,接着完成FPGA的上电配置工作。配置完成后,单片机检测来自FPGA的外部中断CONFDONE。如果配置完成,CONFDONE为高电;否则,为低电平。在检测到CONFDONE为高电平,即配置完成后,单片机将ASET脚置为1,使能FPGA内的伪码发生电路工作,单片机产生伪随机码的流程。配置完成后,首先将Q0输出到PNMA引脚,接着计算反馈逻辑输入,将参与反馈运算的几个状态运算结果存在中间变量MID_VARY中。然后,对各个状态进行右移,为了提高运算效率,使用了带进位C的字节循环右移指令。移位完成后,将MID_VARY存入Q39,再将新的Q0输出到PNMA引脚,程序循环执行产生伪随机码。 单片机核心源程序如下: CLR ASET ;单片机上电后将ASET位清0 CLR PNMA MOV WORD1,#55h MOV WORD2,#0 MOV WORD3,#0 MOV WORD4,#0 MOV WORD5,#0;将55H作为移位寄存器的初值PEIZHI: …… ;进行FPGA的配置工作 JB CONFDONE,PNPRODUCE;根据CONFDONE判断配置是否完成 LJMP PEIZHI ;否则继续配置 PNPRODUCE:SETB ASET ;配置完成后,将ASET脚置1 XMQLOOP:MOV C,Q0 MOV PNMA,C ;将Q0输出到PNMA引脚,作为PN码 MOV C,Q0 MOV WORD6.0,C ;用WORD6单元的0位来存Q0的状态 MOV C,Q2 MOV WORD7.0,C ;用WORD7单元的0位来存Q2的状态 MOV C,Q21 MOV WORD8.0,C ;用WORD8单元的0位来存Q21的状态 MOV C,Q23 MOV WORD9.0,C ;用WORD9单元的0位来存Q23的状态 MOV ACC,WORD6 XRL A,WORD7 XRL A,WORD8 XRL A,WORD9 ;通过异或指令,计算反馈逻辑 MOV C,ACC.0 ;反馈逻辑为Qin=Q0 ;XOR Q2 XOR Q21 XOR Q23 MOV MID_VARY,C ;将运算后的状态存到MID_VARY中右移运算 MOV ACC,WORD1 RRC A ;移位Q7~Q0 MOV WORD1,A ;移位后,保存到WORD1单元中 MOV ACC,WORD2 RRC A ;移位Q15~Q8 MOV WORD2,A ;移位后,保存到WORD2单元中 MOV Q7,C ;将Q8的值赋到Q7 MOV ACC,WORD3 RRC A ;移位Q23~Q16 MOV WORD3,A ;移位后,保存到WORD3单元中 MOV Q15,C ;将Q16的值赋到Q15 MOV ACC,WORD4 RRC A ;移位Q31~Q24 MOV WORD4,A ;移位后,保存到WORD4单元中 MOV Q23,C ;将Q24的值赋到Q23 MOV ACC,WORD5 RRC A ;移位Q39~Q32 MOV WORD5,A ;移位后,保存到WORD5单元中 MOV Q31,C ;将Q32的值赋到Q31 MOV C,MID_VARY ;将前面反馈计算的值赋给Q39 MOV Q39,C LJMP XMALOOP ;继续产生下一代PN码元

6 其它加密方法介绍及比较 对SRAM工艺的FPGA进行加密,除了可以利用单片机实现外,还可以用E2PROM工艺的CPLD实现。与用单片机实现相比,利用CPLD的优点在于可实现高速伪码,但要在硬件电路中增加一块CPLD芯片,使整个硬件电路复杂化,增加了成本。本文提供的加密方法考虑到配置完成后单片机处于空闲状态,此时利用单片机进行加密,不需要增加任何电路成本,使得整个系统硬件结构十分简洁。本文提出采用长伪随机码来实现加密。如果采用其它的算法产生验证信息,并增加单片机与FPGA工作时信息实时交互,使得获取验证信息的难度足够大,也可以达到类似的加密效果。 参考文献 1. 宋万杰 CPLD技术及其应用 1999 2. 候伯亭.顾新 VHDL硬件描述语言与数字逻辑电路设计 1999 3. 蔡美琴.张为民.沈新群 MCS-51系列单片机系统及其应用 1992 4. 沈允春 扩谱技术 1995 5. Ray Schouten A Whitepaper on SRAM FPGAsecurity 6. 刘晓明.王军.谢明钦 基于单片机的复杂可编程逻辑器件快速配置方法 [期刊论文] -电子技术应用2002(10) 7. 屈代明 可编程数字逻辑器件中数字锁相环的实现 [期刊论文] -石油仪器2000(2) 作 者:重庆大学 刘晓明 谢明钦 王军 来 源:单片机与嵌入式系统应用2003(7) |

网友评论