硅片堆叠成就FPGA容量突破 - 看Virtex-7 2000T

发布时间:2011-11-1 11:30

发布者:老郭

|

CPU厂商曾一直引领最新半导体技术的开发。现在似乎不一样了。 近日,赛灵思(Xilinx)公司推出了业界容量最大的FPGA,它含有68 亿个晶体管,200 万个逻辑单元(相当于 2,000 万个 ASIC 门)。在一个视频演示中,赛灵思公司在他们最新Virtex-7 2000T 器件中模拟了3600个处理器,每个处理器的工作频率为100MHz,总运算能力达到18万MIPS。赛灵思公司产品市场营销总监Brent Przybus说,除了世界上少数的几个超级计算机,没有任何芯片能达到如此高的运算能力,而且功耗不到20W。

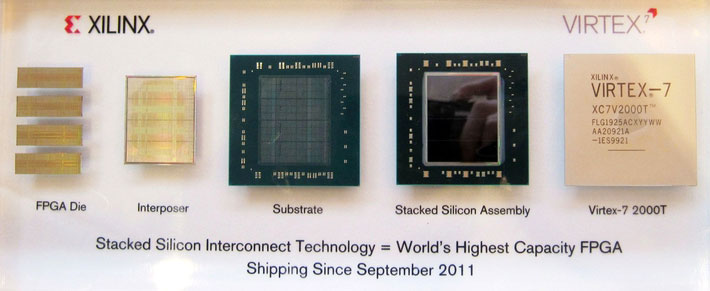

图1:Virtex-7 2000T的性能相当于2到4个最大容量的单片FPGA,但功耗却大幅降低 为何2000T能达到如此高的性能呢?它其实不是一个普通的FPGA。单个的FPGA目前能达到的容量不到100万逻辑单元。由于良率下降的原因,制造更大的FPGA晶片在经济上并不合算。赛灵思的方法是,把4个FPGA并起来使用。但简单地在一个封装内容纳4个FPGA的做法并没有多大帮助:FPGA之间的互联会严重影响系统性能并加重功耗,据说这种做法比使用4个FPGA器件好不到哪儿去。赛灵思采用的是一种更先进的技术,称作“堆叠硅片互联” (SSI),或2.5D IC技术,这样便可以在下一代线宽工艺出现之前实现器件的性能突破。

图2:Virtex-7 2000T包含4个FPGA晶片曾和一个无源中间层 赛灵思的SSI技术简单来说就是把4个28nm工艺的FPGA平行放置在另一层硅片上。这个称作中间层的硅片是65nm工艺的无源(或被动)器件IC,它起到FPGA晶片的互联作用,时延低且功耗小。赛灵思公司全球高级副总裁、亚太区执行总裁汤立人先生说,目前业界通行的说法是,有源(或主动)IC层的堆叠称作3D技术,有源层与无源层的堆叠称作2.5D技术,所以赛灵思所采用的技术是2.5D。就目前的工艺来说,3D IC技术尚未成熟,主要的障碍在于有源层之间的应力和散热问题。

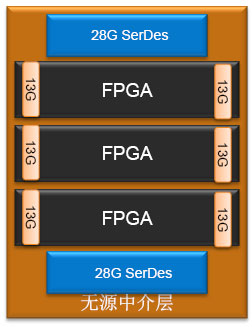

图3:无源中间层起到互联作用,时延低、功耗小 汤立人先生说,堆叠硅片的目的不是为了增加晶体管密度或减小芯片尺寸,而是为了提高芯片性能。目前赛灵思SSI技术是将4个同样的FPGA并行放置,这个称作同构2.5D,下一步的计划是将2.8Gbps的收发器做进来,称作异构2.5D技术,如下图所示。

图4:赛灵思下一步的计划是异构2.5D技术 Virtex-7 2000T的用途专门针对系统集成、ASIC 替代以及 ASIC 原型和模拟仿真。大容量FPGA在初期成本、开发时间、可扩展性等方面具有无可比拟的优势。据说这款产品在赛灵思客户中的反响十分强烈,超出了该公司的预期。 |

网友评论