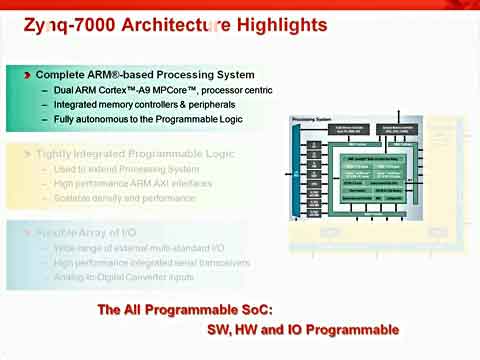

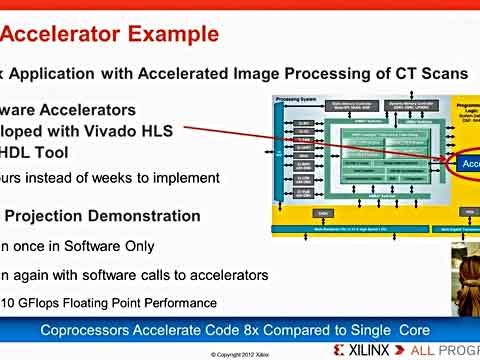

ADI ADSP-BF592 Blackfin处理器开发评估方案

发布时间:2011-9-24 22:36

发布者:1046235000

|

ADI公司的ADSP-BF592是低成本Blackfin处理器,具有适用于工业和通用应用的最佳的外设指令,具有高性能的高达400MHz Blackfin处理器,两个16位MAC,两个40位ALU,四个8位视频ALU和40位移位器.主要应用在消费类音频设备,低成本图像设备,智能电表,消费类手持设备,医疗设备和汽车驾驭辅助系统.本文介绍了ADSP-BF592主要特性,方框图和Blackfin处理器内核框图以及ADSP-BF592 Blackfin处理器评估板框图,电路图和材料清单(BOM). ADSP-BF592: Low Cost Blackfin with Optimized Peripheral Set for Industrial and General Purpose Applications The ADSP-BF592 processor is a member of the Blackfin® family of products, incorporating the Analog Devices/Intel Micro Signal Architecture (MSA). Blackfin processors combine a dual- MAC state-of-the-art signal processing engine, the advantages of a clean, orthogonal RISC-like microprocessor instruction set, and single-instruction, multiple-data (SIMD) multimedia capabilities into a single instruction-set architecture. The ADSP-BF592 processor is completely code compatible with other Blackfin processors. The ADSP-BF592 processor offers performance up to 400 MHz and reduced static power consumption. The ADSP-BF592 processor is a highly integrated system-on-a chip solution for the next generation of digital communication and consumer multimedia applications. By combining industry standard interfaces with a high performance signal processing core, cost-effective applications can be developed quickly, without the need for costly external components. The system peripherals include a watchdog timer; three 32-bit timers/counters with PWM support; two dual-channel, full-duplex synchronous serial ports (SPORTs); two serial peripheral interface (SPI) compatible ports; one UART® with IrDA support; a parallel peripheral interface (PPI); and a 2-wire interface (TWI) controller. Blackfin processors provide world-class power management and performance. They are produced with a low power and low voltage design methodology and feature on-chip dynamic power management, which provides the ability to vary both the voltage and frequency of operation to significantly lower overall power consumption. This capability can result in a substantial reduction in power consumption, compared with just varying the frequency of operation. This allows longer battery life for portable appliances. ADSP-BF592主要特性: Up to 400MHz high performance Blackfin processor Two 16-bit MACs, two 40-bit ALUs, four 8-bit video ALUs, 40-bit shifter RISC-like register and instruction model for ease of programming and compiler-friendly support Advanced debug, trace, and performance monitoring Accepts a wide range of supply voltages for internal and I/O operations Off-chip voltage regulator interface 64-lead (9 mm × 9 mm) LFCSP package MEMORY 68K bytes of core-accessible memory 64K byte L1 instruction ROM Flexible booting options from internal L1 ROM and SPI memory or from host devices including SPI, PPI, and UART Memory management unit providing memory protection PERIPHERALS Four 32-bit timers/counters, three with PWM support 2 dual-channel, full-duplex synchronous serial ports (SPORT), supporting eight stereo I2S channels 2 serial peripheral interface (SPI) compatible ports 1 UART with IrDA support Parallel peripheral interface (PPI), supporting ITU-R 656 video data formats 2-wire interface (TWI) controller 9 peripheral DMAs 2 memory-to-memory DMA channels Event handler with 28 interrupt inputs 32 general-purpose I/Os (GPIOs), with programmable hysteresis Debug/JTAG interface On-chip PLL capable of frequency multiplication ADSP-BF592应用领域: Consumer Audio Low-cost imaging devices Smart Meters Consumer Handheld Devices Medical Equipment Automotive Driver Assistance Systems

图1. ADSP-BF592处理器框图

图2. ADSP-BF592 Blackfin处理器内核框图 ADSP-BF592 Blackfin处理器评估板 Blackfin processors embody a new type of embedded processor designed specifically to meet the computational demands and power constraints of today’s embedded audio, video, and communications applications. They deliver breakthrough signal-processing performance and power efficiency within a reduced instruction set computing (RISC) programming model. Blackfin processors support a media instruction set computing (MISC) architecture. This architecture is the natural merging of RISC, media functions, and digital signal processing (DSP) characteristics. Blackfin processors deliver signal-processing performance in a microprocessor-like environment. Based on the Micro Signal Architecture (MSA), Blackfin processors combine a 32-bit RISC instruction set, dual 16-bit multiply accumulate (MAC) DSP functionality, and eight-bit video processing performance that had previously been the exclusive domain of very-long instruction word (VLIW) media processors. The evaluation board is designed to be used in conjunction with the VisualDSP++ ® development environment to test capabilities of the ADSP-BF592 Blackfin processors. The VisualDSP++ development environment aids advanced application code development and debug, such as: • Create, compile, assemble, and link application programs written in C++, C, and ADSP-BF592 assembly • Load, run, step, halt, and set breakpoints in application programs • Read and write data and program memory • Read and write core and peripheral registers • Plot memory Access to the processor from a personal computer (PC) is achieved through a USB port or an external JTAG emulator. The USB interface provides unrestricted access to the ADSP-BF592 processor and evaluation board peripherals. Analog Devices JTAG emulators offer faster communication between the host PC and target hardware. Analog Devices carries a wide range of in-circuit emulation products. The ADSP-BF592 EZ-KIT Lite provides example programs to demonstrate the evaluation board capabilities. The ADSP-BF592 EZ-KIT Lite installation is part of the VisualDSP++ 5.0. An EZ-KIT Lite is a licensed product that offers an unrestricted evaluation license for the first 90 days.

图3.评估板EZ-KIT Lite外形图 ADSP-BF592 Blackfin处理器评估板特性: • Analog Devices ADSP-BF592 Blackfin processor • Core performance up to 400 MHz • 64-lead LFCSP • Programmable VDDINT core power • Analog Devices AD5258 TWI digital potentiometer • Analog Devices ADP1715 low dropout linear regulator • SPI external flash memory • Numonyx M25P16 – 16 Mb • Audio codec • Analog Devices SSM2603 stereo, 24-bit analog-to-digital and digital-to-analog converters • Highly efficient headphone amplifier • Stereo line input and monaural microphone input • Universal asynchronous receiver/transmitter (UART) • ADM3202 RS-232 line driver/receiver • DB9 female connector • LEDs • Eight LEDs: one board reset (red), three general-purpose (amber), one power (green), one battery good indicator (green), one battery low indicator (amber) and one battery charging indicator (amber) • Push buttons • Four push buttons: one reset, two programmable flags, and one wake-up with debounce logic • Expansion interface II • Next generation of the expansion interface design, provides access to most of the processor signals • Land grid array • Easy probing of all port pins • Other features • JTAG ICE 14-pin header • Battery charger for a 3.7V single sell Li-Ion battery The EZ-KIT Lite is designed to demonstrate the ADSP-BF592 Blackfin processor capabilities. The processor has an I/O voltage of 3.3V. The core voltage of the processor is controlled by an Analog Devices ADP1715 low dropout regulator (LDO) and an Analog Devices AD5258 digipot, which is configurable over the 2-wire interface (TWI) signals. Refer to thepower-on-self test (POST) example in the ADSP-BF592 installation directory of VisualDSP++ for information on how to set up the TWI interface. The core voltage and clock rate can be set up on the fly by the processor. The input clock is 25 MHz. The core and system clock are programmable via the PLL_DIV register of the processor. The core clock runs at a maximum of 400 MHz.

图4.评估板EZ-KIT Lite方框图

图5.评估板EZ-KIT Lite电路图(1)

图6.评估板EZ-KIT Lite电路图(2)

图7.评估板EZ-KIT Lite电路图(3)

图8.评估板EZ-KIT Lite电路图(4)

图9.评估板EZ-KIT Lite电路图(5)

图10.评估板EZ-KIT Lite电路图 (6) 评估板EZ-KIT Lite材料清单(BOM):

详情请见: http://www.analog.com/static/imported-files/data_sheets/ADSP-BF592.pdf 和 http://www.analog.com/static/imported-files/eval_kit_manuals/ADSP-BF592_EZ-KIT_%20Lite_%20Rev1.0.pdf |

网友评论