通讯系统中超高效率降压型变换器的设计考虑

发布时间:2009-12-22 09:18

发布者:贾延安

|

目前,通讯系统要求越来越快的处理速度,其内部专用集成芯片、处理器单元等电路消耗的电流也越来越大。同时,为减小系统的体积和尺寸,内部的低压大电流的 DC/DC 变换器不断向高频、高密度方向发展。频率的提高带来了系统变换效率的降低。此外,世界范围内的能源危机和环境污染提出了节能减排的要求,因此,基于高频的变换器必须采用新型的器件,以保证系统既能工作在高频下,实现小尺寸小体积,又能提高系统的整体效率,达到节能减排的目的。整体效率的提高,进一步降低了电源系统的发热量,提高了系统的可靠性。通讯系统内部的系统板使用了大量的降压型变换器,本文将详细的讨论这种变换器的设计。 降压型变换器工作特点 在通讯系统的系统板上,前级通常是从-48V电源通过隔离电源或电源模块得到12V或24V输出,也有采用3.3或5V输出。目前基于ATCA的通讯系统大多采用12V的中间母线架构,然后再由降压型变换器将12V向下转换为3.3、5V、2.5V、1.8V、1.25V等多种不同的电压。常规的降压型变换器续流管采用肖特基二级管,而同步降压型变换器下面的续流管却使用功率MOSFET。由于功率MOSFET的导通电阻Rds(on)小,导通电压也远远低于肖特基二级管的正向压降,所以效率更高。因此,对于低压大电流的输出,通常利用同步的降压型变换器获得较高的效率。 对于降压型变换器,有以下的公式: Vo=Don×Vin 其中,为占空比。当输入电压较高时,占空比就小。因此,当输入电压高,而输入电压较低,即输入输出的电压差较大时,在一个开关周期,上部主功率开关管导通的时间将减小,而下部续流开关管导通的时间将延长。图1为上部MOSFET管和下部MOSFET管的工作波形,阴影为产生开关损耗的部分。 (a) 上管的开关波形 (b) 下管的开关波形

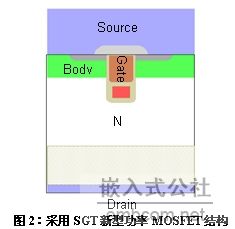

上部MOSFET管在开关的瞬态过程中产生明显的开关损耗,同时MOSFET导通电阻Rds(on)也将产生的导通损耗。平均导通损耗与占空比和导通电阻 Rds(on)成正比。对于基于ATCA的通讯系统,其输入电压为12V,输入输出的电压差大,占空比小,因此导通损耗相对较小,而开关损耗占较大比例。开关损耗主要与开关频率及MOSFET在开关过程中持续的时间成正比。开关持续的时间与MOSFET漏栅极的米勒电容直接相关。米勒电容小,开关持续时间短,则开关损耗低。因此,对于上部MOSFET管的功率损耗,必须同时考虑开关损耗和导通损耗。为降低导通电阻 Rds(on),MOSFET通常要采用更大面积的晶圆,这样就可以得到更多的小单元,多个小单元并联后的总导通电阻Rds(on)就更低。但与此同时,这也会增加漏极和栅极的相对面积,从而增大漏极和栅极米勒电容。 从波形可以看到,对于下部MOSFET管在开关的瞬态过程中,没有产生明显的开关损耗。通常MOSFET的关断是一个自然的0电压的关断,因为在MOSFET的漏极和源极有一个寄生的电容。由于电容的电压不能突变,所以在关断的过程瞬态过程中,漏极和源极电压几乎为0。这样在关断的过程中,电压与电流的乘积也就是关断的功耗为0。对于MOSFET,要想实现0电压的开关ZVS,关键要实现其0电压开通。 为防止上下管直通,同步降压型变换器的上下管通常有一个死区时间。在死区的时间内,上下管均保证关断。当上管关断后,由于输出电感的电流不能突变,必须维持原来的方向流动,所以下部功率MOSFET内部寄生二极管导通。寄生二极管导通后,下部MOSFET的漏极和源极的电压为二极管的正向压降,几乎为0,因此在寄生二极管导通后,MOSFET再导通,其导通是0电压的导通,开通损耗为几乎0。这样下管是一个0电压的开关,开关损耗几乎0。因此在下管中,主要是由导通电阻Rds(on)形成导通损耗。下管的选取主要考虑尽量选用低导通电阻Rds(on)的产品。 此外,为减小在死区时间内体内寄生二极管产生的正向压降功耗和反向恢复带来的功耗,通常会并联一个正向压降低、反向恢复时间短的肖特基二极管。过去主要是在下管MOSFET的外部并联一个肖特基二极管,现在通常将肖特基二极管集成在下部MOSFET管内部。起初是将一个单独的肖特基二极管和一个MOSFET 封装在一起,后来是将它们做在一个晶圆上。将一个晶圆分成二个区,一个区做MOSFET,一个区做肖特基二极管。 二极管具有负温度系数,并联工作不太容易。在一个晶圆上分成二个区做MOSFET和肖特基二极管,那么肖特基二极管在与MOSFET交界的区域温度高,而离 MOSFET较远的区域温度低。当肖特基二极管温度高时,流过更大的电流,因此与MOSFET交界的肖特基二极管区域的温度将进一步上升,可能导致局部损坏。现在通常将肖特基二极管的单元做到MOSFET的单元里面,这样可能得到更好的热平衡,提高器件可靠性。 适用于上管的SGT新型功率MOSFET 通常,对于MOSFET,导通电阻Rds(on)和漏极栅极的米勒电容是一个相互矛盾的参数,必须采用新技术才能解决这个问题。对于同样面积的晶圆,如果要减小米勒电容,则必须减小漏极和栅极相对接触面积。最为直观的方法是对栅极采用一定的屏蔽技术,减小漏极和栅极的相对电容。图2就是采用AOS的专利技术SGT所制作的具有极低漏极栅极米勒电容的新型功率MOSFET。

在图2中,除了栅极结构,其它部分是标准的采用Trench工艺的MOSFET。栅极被分割成上下两个部分,下部分用一些特殊的材料屏蔽起来。下部分在内部和上部分的栅极相连,而下部分栅极的屏蔽层被连接到源极,以减小漏极栅极米勒电容。采用这种技术设计的MOSFET,例如AOL1464,其Vds为 30V,在Vgs等于10V条件下,Rds(on)为6.2mΩ,而其Crss只有20pF。这样大大减小了开关过程中米勒平台的持续时间,降低了开关损耗。AOL1430的Vds为30V,在Vgs等于10V条件下,Rds(on)为2.5mΩ,而其Crss为50pF。图3给出了下管采用AOS的 AOL1428、上管采用AOL1430的设计,和采用其他厂家目前Crss最低器件的设计的效率曲线。由此可见,上管采用AOL1430的设计具有非常高的效率。请注意,这里的输入电压为12V,输出电压为1.7V,开关频率为300kHz。

适用于下管的超低Rds(on)功率MOSFET 下管主要是导通损耗,因此要尽量使用导通电阻Rds(on)低的功率MOSFET。目前主要通过改进工艺和使用新的材料,在同样面积的晶圆上降低每个单元的电阻,同时尽可能设计出更多的单元,提高单元的密度,以形成低的导通电阻Rds(on)。 (a) 原来的单元结构 (b) 新的单元结构

在图4中,每个MOSFET单元在相同额定的Vds电压条件下,导通电阻都相同,具有更高的单元密度,在水平和垂直两个方向都尽可能缩小了尺寸。AOS的 AON 6702采用DFN的封装,Vds为30V,在Vgs等于10V条件下,Rds(on)为1.9mΩ,同时内部集成了具有优异开头特性的肖特基二极管。 本文小结 同步降压型变换器的上管同时具有开关损耗和导通损耗,在输入输出压差大的应用中,以开关损耗为主。导通损耗与MOSFET的导通电阻Rds(on)成正比,开关损耗与漏极栅极米勒电容相关。 采用SGT技术功率MOSFET具有超低的漏极栅极米勒电容,减小了开关过程中米勒平台的持续的时间,降低了开关损耗。 同步降压型变换器的下管只有导通损耗,开关损耗几乎为0。建议选取Rds(on)尽量小的MOSFET。采用新工艺和新材料可以提高晶圆上单元的晶胞密度,降低单元的电阻密度。 作者:刘松,丁宇 万代半导体元件(上海)有限公司 作者介绍:刘松,男,硕士,36岁,万代半导体元件有限公司应用中心经理,曾任凌特有限公司上海办事处应用工程师,ST意法半导体上海有限公司高级电源系统工程师,现主要从事开关电源系统及模拟电路的应用研究和开发工作。发表论文30多篇,获发明专利一项及广东省科技进步二等奖一项。 地址:上海市松江区松蒸公路888号松江出口加工区B区茸康路109弄91号8/9栋 邮编201614 |

网友评论