零电容存储器ZRAM

发布时间:2009-12-1 09:11

发布者:李宽

|

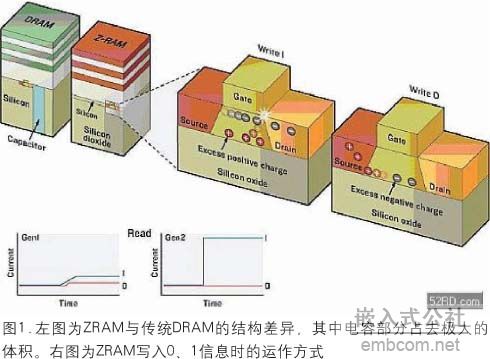

作者:秦文芳(wqin@semi.org) 对于IC设计的同行们来说,如何在提高存储密度的同时,又不用将芯片尺寸做得更大?位于日内瓦湖畔的芯片公司Innovative Silicon似乎找到了好的解决办法。 这家年轻的瑞士公司开发了零电容存储器ZRAM,即Zero Capacitor RAM。ZRAM原理事实上也就是传统DRAM的原理:以电容电荷来储存0、1信息,不过结构上异于传统DRAM。传统的DRAM是在电路设计时特意设计上用来储存电荷的电容,而ZRAM则直接利用绝缘硅(SOI)制程所加入的绝缘基板的副效应来充当电容(图1)。

所谓的副效应其实称为浮体效应(Floating Body Effect),是采用SOI制程后意外产生的效应。该效应是在上层电路与下层绝缘基板会产生电容效应,由于是意外产生,且对上层电路运作会产生不良影响,理应积极去除。但是如果运用上层电路来控制该电容,即可实现储存。稍有不同的是,ZRAM是将电容控制在电晶体闸极的下方。 ZRAM的最大特点就是不使用电容来保存数据,并采用先进的SOI工艺,可比处理器缓存常用的嵌入式SRAM得到大得多的密度,能显著提高处理器缓存容量。传统DRAM的每一位单元需要一个晶体管和一个电容,而ZRAM不需要电容,只需要一个晶体管就可以了。这样一来的直接结果就是ZRAM占用的电路面积几乎等于传统的一半,而且速度和功耗上也有相应的提高。 ZRAM基本上不需要任何新材料,也不需要制造工艺增加额外的处理步骤。这对芯片生产商来说极为重要。他们不愿为已经很复杂、很精密的工艺添加任何新材料。额外的处理步骤也会增加成本,而且往往增加幅度很大。 由于使用电容储存0、1资讯,因此与传统DRAM一样,电荷会随着时间逐渐消逝,所以ZRAM等也需要刷新才能保持资讯。在特性上,ZRAM有接近 SRAM的存取速度,以及胜过传统DRAM的记忆密度(原因是省去刻意设计的电容,直接取用浮体效应所产生的电容),且与现有的CMOS制程相兼容,而缺点则是要使用SOI制程。 ZRAM是一种单晶体管存储单元。尽管很多公司试图在SOI衬底上实现ZRAM,最终还是采用体硅上的finFET或者环栅(柱子)器件,这对于DRAM器件制造商来讲具有特别的吸引力。 标准的DRAM单元由一个晶体管和一个电容组成。为了实现更大的存储单元、更多的存储电荷,电容器的面积需要不断地增大。因此,为了节省昂贵的晶圆面积,DRAM厂商在晶体管上方制造电容,由此产生了高深宽比结构。并且为了等比例减薄介电材料厚度,还引入了高k值材料。通过使用ZRAM代替 DRAM,可以通过一个器件代替两个器件,潜在的晶圆加工成本可以降低20~30%。此外,由于ZRAM去除了高深宽比电容以及位线接触,ZRAM工艺可以更快地实现大批量生产并且允许更快的技术节点缩小。 ZRAM的魅力在于:不用什么特别的半导体,不用结构独特的元件,也不用试验性的绝缘体,每个存储单元就是一个晶体管。相比之下,传统的片上内存通常每个存储单元使用六个晶体管。所以可以把5MB的ZRAM内存做到仅仅1MB的传统嵌入式内存占用的面积上。这样可以大大增加芯片上的内存数量,从而提高性能并大幅减小芯片的尺寸和成本。 ZRAM技术兼顾了半导体行业的两个永远的追求:处理速度更快、功耗更低。经济因素对ZRAM极为有利,也许未来会对存储器领域带来革命性的改变。 |

网友评论