高速放大器设计三大常见问题, TI 帮您攻克

发布时间:2020-9-29 11:13

发布者:eechina

|

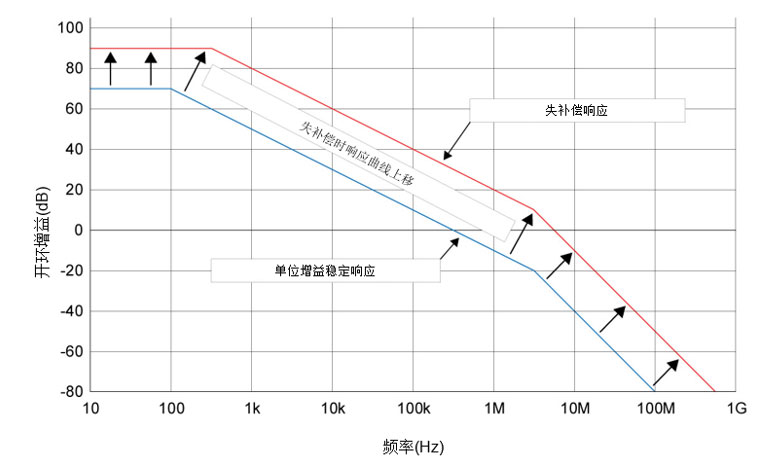

作者:德州仪器(TI) 在使用高速放大器进行设计时,一定要熟悉其通用的规格并了解其特定概念。在本文中,高速放大器是指增益带宽积(GBW)大于或等于50 MHz的运算放大器(op amps),但这些概念也适用于低速器件。以下设计师在使用高速放大器时遇到的一些常见问题。 问:为什么某些高速运算放大器具有最小增益规格? 答:失补偿的运算放大器具有闭环最小增益稳定规格,但与单位增益稳定的同类产品相比,在相同电流消耗下,其可提供更大的GBW和更低的噪声。 “失补偿”仅表示Aol(开环增益)响应曲线中具有第二个高于0 dB的极点。这第二个极点还规定了确保放大器稳定性所需的最小增益。想象一下Aol曲线“上移”,如图1所示。增加的Aol会导致更宽的带宽。

图1:失补偿放大器的开环增益响应曲线 缩小放大器输入对中的负反馈电阻的尺寸会增加Aol,如图2所示。更小的负反馈电阻还有助于降低放大器噪声。

图2:运算放大器中的负反馈电阻 OPA858 和 OPA859分别是失补偿和单位增益稳定放大器的两个示例。对于相同的电流消耗,OPA858 具有更宽的带宽和更低的噪声,如表1所示。

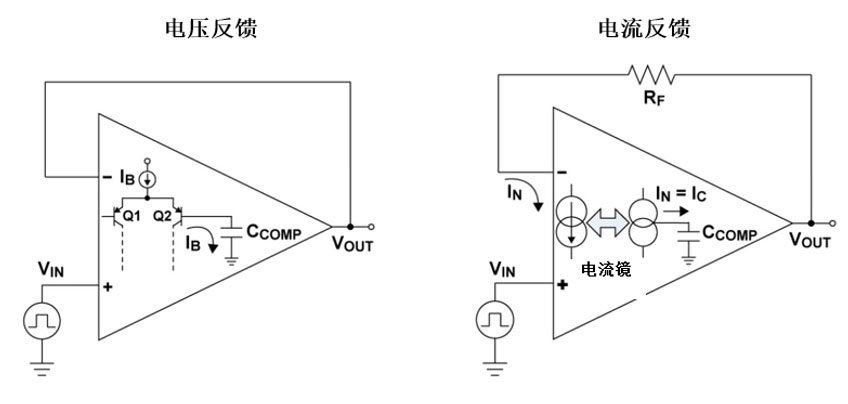

除增加带宽和降低噪声外,失补偿体系结构还可实现更高的压摆率。总体而言,最小增益规格提供了性能折衷。这意味着如果您放弃单位增益并满足最小增益要求,则可利用该性能。有望轻松满足最小增益规格的应用示例包括电流检测电路。其可测量并联电阻上的电压、信号链中的增益级和跨阻电路。 问:什么是电流反馈放大器? 答: 电流反馈放大器是一种通过将一部分输出信号作为电流反馈以实现对于放大器的控制的运算放大器。电流反馈放大器不同于依赖于电压形式的反馈的电压反馈放大器。大多数设计人员都了解电压反馈体系结构,因为它们在大多数电子课程中它们很常见并作为重点出现。 图3提供了电压和电流反馈放大器体系结构的基本输入级比较,其中电压反馈放大器建模为电压控制电压源,电流反馈放大器建模为电流控制电压源。

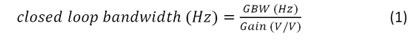

图3:比较电压和电流反馈运算放大器体系结构 两种体系结构仍被用作负反馈电路中的误差放大器,但它们所需的反馈类型有所差异。例如,您可在反相和同相增益配置中使用其中任何一种放大器。电流反馈体系结构的一个明显优势是带宽不取决于增益。但在电压反馈体系结构中,随着增益的增加,带宽减小,如公式1所示:

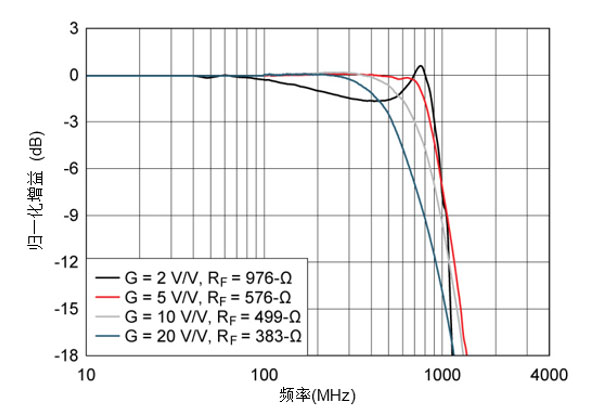

如图4所示,在电流反馈体系结构中,无论增益如何,带宽几乎保持恒定,。该图如THS3491数据表中所示。

图4:电流反馈运算放大器的增益和带宽关系 表2比较了电压和电流反馈放大器之间的一些主要区别。

请注意:电流反馈放大器的操作并非指在反馈路径中没有电阻。电流反馈放大器数据手册将对RF的指定值提出建议;这些值很重要,因为RF值决定了放大器,甚至单位增益的补偿。如图4,表3来自THS3491数据表。

有关这两种体系结构之间差异的更多详细信息,请查看了解电压反馈和电流反馈放大器。还可通过观看TI高精度实验室在线培训视频来了解有关电流反馈体系结构的更多信息。 问:为什么将高速放大器放在电路实验板上时会发生振荡? 答:一般而言,封装引线的电感以及电路试验板的电容和电感很可能导致高速放大器振荡。同样,在使用高速运算放大器进行设计时,最小化印刷电路板(PCB)上的电容和电感是至关重要的。即使是高速放大器GBW频谱下端的器件,如50MHz OPA607,也需要这些类型的电路板级设计注意事项。 可通过以下几种方法来优化高速布局设计: • 最小化走线长度。最小化走线长度可减少额外的电容和电感。 • 使用固定接地平面。对于高速设计而言,固定接地平面通常比散列平面更佳。 • 去除信号走线下方的接地层。去除器件输入和输出下方的接地层金属有助于减少敏感节点上的寄生电容。 • 最小化信号路径上的通孔。通孔会增加电感,并可能在高于100 Mhz的频率下引起信号保真度问题。为降低信号保真度,请将关键信号与放大器在同一层布线,以消除任何通孔。 • 优化返回电流路径。信号走线布局设计应尽量减少整个信号路环面积,从而使电感最小。 • 正确放置和布线旁路电容器。在电路板的同一层上,放置旁路电容器时应尽可能靠近放大器。使用较宽的走线,并将测通孔布线到旁路电容器,然后再到放大器,而非布线在电容器和放大器之间。 • 正确放置电阻。将增益设定电阻、反馈电阻和串联输出电阻置于靠近器件管脚的位置,以最大程度地减少电路板寄生效应。 评估高速运算放大器的性能时,最好对特定器件使用指定的评估模块。这些电路板展示了良好的高速电路板布局设计,并使用SMA连接器来维持高保真度和阻抗受控的信号路径。有关高速电路板布局实践的更多详细信息,请阅读高速PCB布局技术。 总体而言,高速运算放大器的运行方式与低速运算放大器相当。只需考虑一些设计上的细微差别,就可以利用它们为你的系统提供的所有速度和性能优势。以上哪些问题与您最相关?请在下方发表评论。 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

网友评论