ЮДгІгУгІБфЙЄГЬЃПChipwiorksЭјеОЫЩЯТ32nm HKMGЙЄвеЗжЮіГіТЏ

ЗЂВМЪБМфЃК2011-3-20 02:48

ЗЂВМепЃК1770309616

|

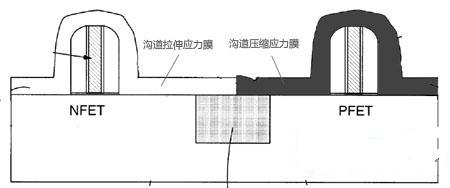

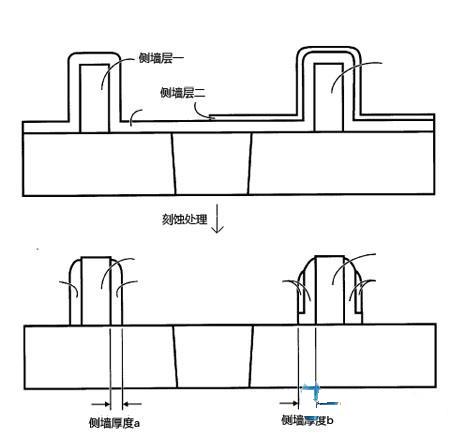

ШеБОЫЩЯТЙЋЫОдјБэЪОЦфЪзПюЛљгкHKMGЙЄвеЕФ32nmаОЦЌВњЦЗНЋгк2010ФъЕФ10дТЗнЩЯЪаЁЃЖјОЙ§ГЄЪБМфЕФЕШД§жЎКѓЃЌзюНќжЊУћаОЦЌММЪѕЗжЮіЙЋЫО ChipworksЕФЗжЮіЪІDick JamesжегкЗЂБэСЫЖдЫЩЯТетПю32nm HKMGаОЦЌВњЦЗЕФбаОПБЈИцЃЌБЈИцГЦИУЙЋЫООЙ§ЗжЮівбОКЫЪЕЫЩЯТЕФетПю32nm HKMGаОЦЌВњЦЗВЩгУЕФЪЧgate firstЙЄвежЦзїЁЃжСгкЮЊЪВУДКХГЦШЅФъ10дТЗнвбОЩЯЪаЃЌЖјЕНЯждкЭтНчВХФУЕНетПюаОЦЌНјааЗжЮіЃЌDick JamesдђНтЪЭГЦЃКЁАетПюаОЦЌВњЦЗШЗЪЕШчЫЩЯТЫљГаХЕЕФФЧбљЪЧдкШЅФъ10дТЗнМДЕк44жмЩЯЪаЕФЃЌВЛЙ§гЩгкВњЦЗСїЭЈЛЗНкЗБЫіЃЌвђДЫЮвУЧЕНзюНќВХЕУЕНСЫгаЙиЕФЪЕМЪВњЦЗЁЃЁБЫЩЯТЕБФъЛЙдјОЭЦГіЙ§ЛљгкHKMGЙЄвеЕФ45nmжЦГЬВњЦЗЃЌЕБЪБЦфетПюВњЦЗЩЯЪаЕФЪБМфКЭIntelЕФHKMG 45nmВњЦЗЗЧГЃНгНќЁЃВЛЙ§дк32nmНкЕуЃЌDick JamesдђБэЪОЃЌЫЩЯТЭЦГіЭЌРрВњЦЗЕФВНЕїдђЁАвЊБШIntelТ§СЫвЛФъзѓгвЃЌВЛЙ§ОнЮвУЧЫљжЊЃЌЫЩЯТгІИУЪЧЪзМвПЊЪМХњСПЩњВњ32nm HKMGаОЦЌВњЦЗЕФГЇМвЁЃЁБ ЖдЫЩЯТ32nm HKMGаОЦЌВњЦЗЕФЗжЮіЯдЪОЃЌетПюВњЦЗЁАВЩгУОХВуН№ЪєЛЅСЌВуЩшМЦ(8ВуЮЊЭЛЅСЌЃЌ1ВуЮЊТСЛЅСЌ)ЃЌЛЅСЌВуЕчНщжЪдђВЩгУСЫlow-kКЭextra-low-kСНжжЕчНщжЪЛьКЯЕФНсЙЙЁЃаОЦЌКЫаФГпДчдМ45ЦНЗНКСУзЃЌВЩгУГЃЙцЕФFC-BGAЗтзАаЮЪНЁЃзюаЁЕФН№ЪєДЅЕуНкОрГпДчОнЫЩЯТЙЋВМЕФЪ§ОнЮЊ120nmЃЌВЛЙ§ЮвУЧдкжЎЧАЕФЗжЮіжаЕУГіЕФЪЕМЪНкОрГпДчдђЪЧ125nmзѓгвЁЃЁБ ЫЩЯТЛЙаћГЦЦф32nm HKMGВњЦЗЕФадФмЬсЩ§СЫ40%ЃЌЭЌЪБЙІКФдђМѕЩйСЫ40%ЃЌаОЦЌУцЛ§дђЫѕаЁСЫ30%ЁЃ ЗжЮіЮФеТНјвЛВНжИГіЃКЁАПЩМћЫЩЯТ32nm HKMGаОЦЌЕФеЄМЋВЩгУЖрОЇЙшеЄ+ЕзВПTiNН№ЪєЙІКЏЪ§ВуЕФНсЙЙЃЌдкTiNВуЕФЕзВППЩвдЙлВьЕНhigh-kОјдЕБЁВуНсЙЙЁЃСэЭтЃЌжЕЕУзЂвтЕФЪЧетПюВњЦЗЕФеЄМЋВЩгУСЫЫЋВрЧНЙЄве(dual-spacer)ЃЌЫЋВрЧНЙЄвегаЪБгжБЛГЦЮЊВюЖЏЪНЦЋвЦИєРыВрЧН(differential offset spacer)ММЪѕЁЃСэЭтдкОЇЬхЙмЕФТЉдДМЋЖЅВППЩЙлВьЕНвЛВуБЁБЁЕФЕЊЛЏЮяЃЌетЯдЪОЫЩЯТетПюВњЦЗЕФhigh-kОјдЕВуЕзВПКЭЙшЙЕЕРЖЅВПжЎМфПЩФмВЩгУСЫЕЊбѕЛЏЮя(ЭЦВтгІИУЪЧSiON)жаМфВуЁЃЁБ differential offset spacerЭМНт dual-spacerВЂВЛЫуЪЧвЛЯюНЯаТЕФММЪѕЃЌвђДЫдкНќФъЕФБЈЕРжаНЯЩйБЛЬсМАЃЌетжжММЪѕЕФЪЕжЪЪЧЭЈЙ§ЕїНкВрЧНКёЖШРДЕїећеЄМЋЕФГЄЖШЃЌДгЖјПижЦТЉдДМЋРЉЩЂЧјКЭеЄМЋЕФжиКЯГЬЖШЃЌвдДяЕНПижЦЙЕЕРгааЇГЄЖШЃЌМАМѕаЁТЉдДМЋгыеЄМЋЕФМФЩњЕчШнЕФзїгУЁЃ ЁАеЄМЋКЭТЉдДМЋЕФН№ЪєЛЏЙЄве(salicide)дђВЩгУГЃМћЕФФјН№ЪєЛЏВєдгВЌЕФЙЄвеЁЃВЛЙ§ЫЩЯТ32nm HKMGВњЦЗЩЯВњЩњгІБфСІЕФЛњжЦдђБШНЯВЛУїЯдЃЌЫћУЧВЩгУЕФМШВЛЪЧЛљгкеЄМЋЕЊЛЏВуЕФММЪѕЃЌвВВЛЪЧЧЖШыЪНSiGeММЪѕЃЌСэЭтвВУЛгаЪЙгУЫЋгІБфСІФЄ(dual-stress liner:МДгУСНВуЗжБ№ПЩЖдЙЕЕРЪЉМгРЩьгІСІКЭбЙЫѕгІСІЕФЕЊЛЏФЄПижЦЙЕЕРгІБфСІ)ММЪѕЁЃЁБ ЕБФъAMD/IBMЫљгУЕФDSLЭМНт ЛиЙЫЫЩЯТЕБФъЕФ45nm HKMGЙЄвеЁАЫЦКѕУЛгаЪЙгУШЮКЮЙЕЕРгІБфдіЧПММЪѕЃЌPMOSЙЕЕРЧЈвЦТЪдіЧПЗНУцдђжЛВЩгУСЫ<100>ОЇЯђЩшМЦ(ЦеЭЈаОЦЌЮЊ<110>ОЇЯђЃЌЕЋ<100>ОЇЯђЕФPMOSЙЕЕРПебЈЧЈвЦТЪЯрЖдНЯИпЃЌЕБШЛОЇЯђЙЄГЬЕФаЇФмгыгІБфЙЄГЬЪЧЮоЗЈЯрБШЕФ)ЁЃПЩМћЫЩЯТгыIntelЕФ45nm HKMGЙЄвеЦфЫпЧѓЕФжиЕуВЛЭЌЃЌIntelВржигкОЇЬхЙмадФмЕФЬсЩ§ЃЌЖјЫЩЯТдђВржигкМЏГЩЖШЕФЬсИпКЭГЩБОЕФЯТНЕ.ЖјЕН32nmНкЕуЃЌЫЩЯТЕФВржиЕугждіМгСЫhigh-kОјдЕВуЕФЪЙгУКЭгЩДЫДјРДЕФЕЭЙІКФ/ЕЭТЉЕчЁЃЁБ |

ЭјгбЦРТл