MR25HxxxDFЕФ2.0mmТуТЖЕзЕцаТЗтзАвбЛёEverspinХњзМЩњВњ

ЗЂВМЪБМфЃК2020-4-14 14:23

ЗЂВМепЃКгЂЩаЮЂЕчзг

|

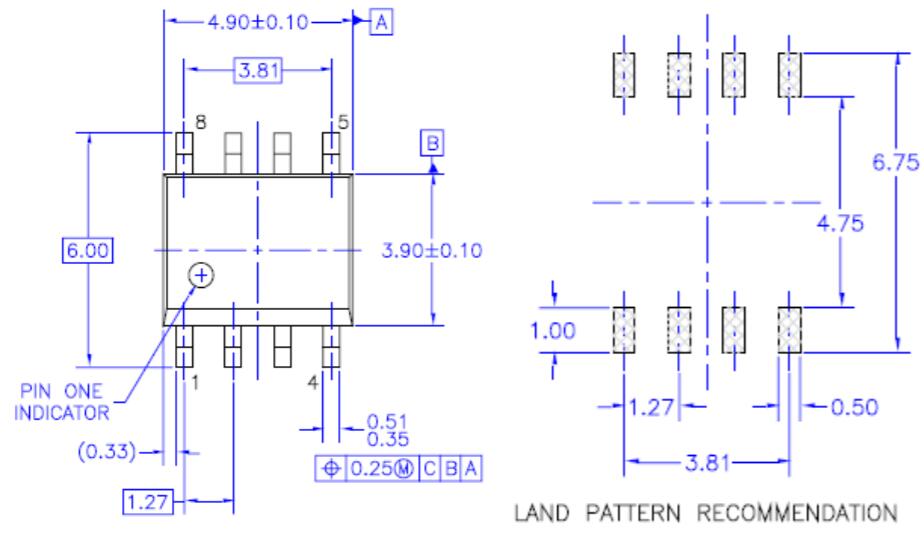

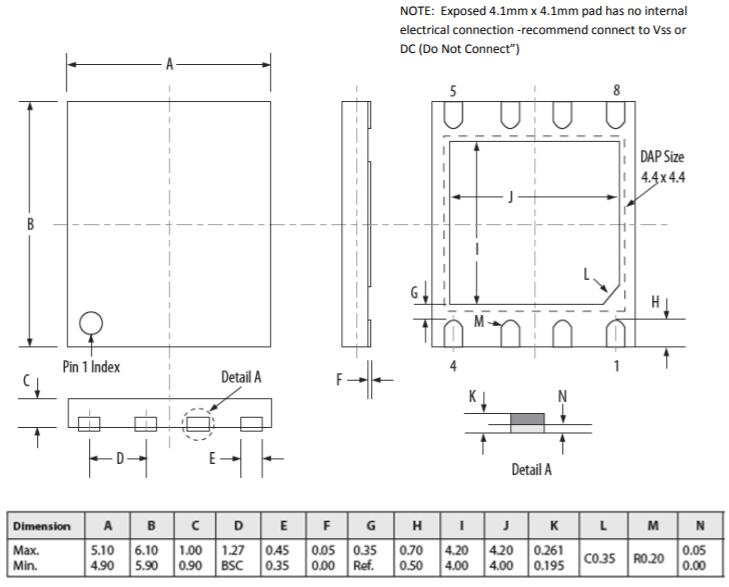

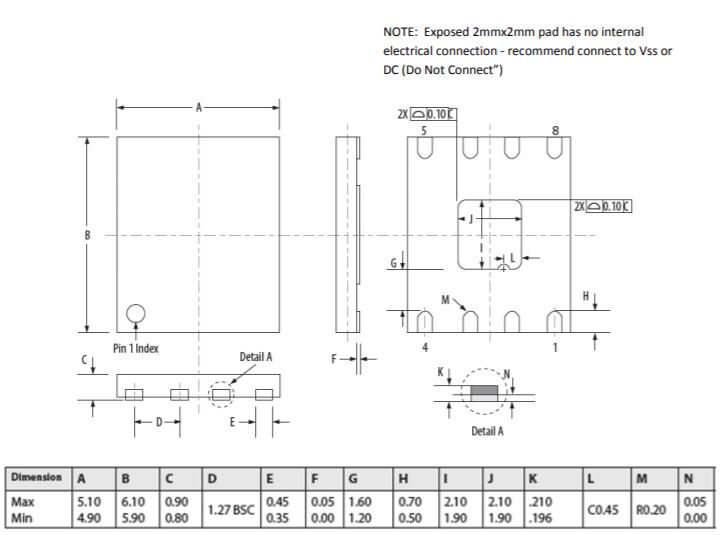

everspinдкДЫЩњВњЛљгк180nmЃЌ130nmКЭ90nmЙЄвеММЪѕНкЕуЕФMRAMВњЦЗЁЃВњЦЗАќзАКЭВтЪдвЕЮёБщМАжаЙњЃЌЬЈЭхКЭЦфЫћбЧжоЙњМвЁЃдкЦНУцФкКЭДЙжБДХЫэЕРНсЃЈMTJЃЉSTT-MRAMЮЛЕЅдЊЕФПЊЗЂЗНУцДІгкЪаГЁСьЯШЕиЮЛЁЃ EVERSPINЕФSPIВњЦЗЯЕСажадіМгСЫОпга2mmЕзВПТуТЖКИХЬЕФаТаЭDFN8ЗтзАЁЃетжжаТЗтзАдЪаэИУЦїМўМШПЩгУгкJEDECБъзМSOIC-8в§НХгжПЩгУгкDFN8 PCBКИХЬЭМАИЁЃЭМ1ЯдЪОСЫЕфаЭЕФSOIC-8 PCBКИХЬЭМАИЁЃ вЛаЉEverspinПЭЛЇЖдEverspinЁА DCЁБ DFNЗтзАЕФТуТЖЕзВПКИХЬЃЈ4.1mmКИХЬЃЉгыSOIC-8ЗтзАЕФPCBКИХЬжЎМфЕФБпМЪМфЯЖБэЪОЕЃгЧЁЃ EverspinЕФаТаЭ2mmТуТЖКИХЬDFN-8ЗтзАЛКНтСЫетжжЕЃгЧЁЃ  ЭМ1ДњБэСЫJEDECБъзМSOIC-8ЗтзАЕФНќЫЦГпДчКЭНЈвщЕФPCBКИХЬЭМАИЃЈзЂвтЃКвдЯТГпДчЮЊНќЫЦжЕЃЌПЩФмвђЙЉгІЩЬЖјвьЃЉ ЭМ2КЭЭМ3ЗжБ№ЪЧEverspin MR25HxxxDCЃЈ4.1mmТуТЖЕФЕзВПКИХЬЃЉКЭMR25HxxxDFЃЈ2.0mmТуТЖЕФЕзВПКИХЬЃЉЕФЗтзАГпДчЁЃгЩгкMR25HxxxDCЕФ4.1mmТуТЖЕзЕцгыSOIC-8 PCBКИХЬЭМАИжЎМфДцдкБпМЪМфЯЖЃЌвђДЫОпга2.0mmТуТЖЕзЕцЃЈMR25HxxxDFЃЉЕФаТЗтзАвбЛёEverspinХњзМЩњВњЃЌВЂЧвгыJEDECМцШнБъзМSOIC-8КЭDFN-8КИХЬЭМАИЁЃНЯаЁЕФЕзЕцдкЕзЕцКЭSOIC-8ЕФPCBКИХЬЭМАИжЎМфЬсЙЉзуЙЛЕФМфЯЖЁЃ  ЭМ2-Everspin MR25HxxxDCЗтзАЕФЗтзАГпДч  ЭМ3-EverspinЕФMR25HxxxDFЗтзАЕФЗтзАГпДч |

ЭјгбЦРТл