ЭцзЊZynqСЌди28ЁЊЁЊ[ex50] ЕквЛИіZynqЯЕЭГЙЄГЬЁАHello ZynqЁБ

ЗЂВМЪБМфЃК2019-9-30 13:24

ЗЂВМепЃКrousong1989

|

ЭцзЊZynqСЌди28ЁЊЁЊ[ex50] ЕквЛИіZynqЯЕЭГЙЄГЬЁАHello ZynqЁБ ИќЖрзЪСЯЙВЯэ ЬкбЖЮЂдЦСДНгЃКhttps://share.weiyun.com/5s6bA0s АйЖШЭјХЬСДНгЃКhttps://pan.baidu.com/s/1XTQtP5LZAedkCwQtllAEyw ЬсШЁТыЃКld9c

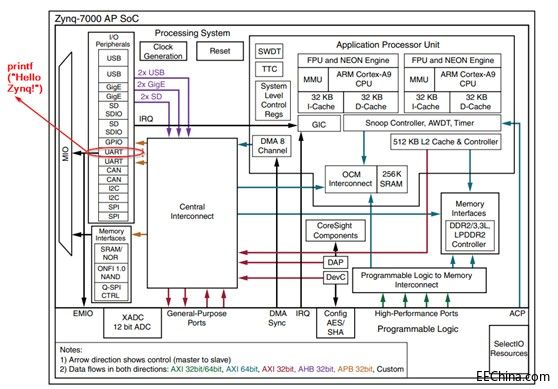

ЬкбЖЮЂдЦСДНгЃКhttps://share.weiyun.com/5s6bA0s АйЖШЭјХЬСДНгЃКhttps://pan.baidu.com/s/1XTQtP5LZAedkCwQtllAEyw ЬсШЁТыЃКld9c ШчЭМЫљЪОЃЌZynqЯЕЭГЕФPSВПЗжгаЗсИЛЕФЭтЩшНгПкЃЌГЃМћЕФUSBЁЂUARTЁЂSPIЁЂI2CЁЂSDIOЁЂCANЁЂGPIOЁЂвдЬЋЭјЃЌвЛгІОуШЋЃЌФмЙЛТњзуДѓЖрЪ§ЕФЧЖШыЪНгІгУашЧѓЁЃетУДЧПДѓЕФЭтЩшЯЕЭГЃЌЪЧВЛЪЧгааЉЦШВЛМАД§СЫЃЌВЛзХМБЃЌЭђеЩИпТЅЦНЕиЦ№ЃЌЮвУЧвЊДгзюМђЕЅЕФСїГЬХмЦ№ЃЌДјДѓМвЯШДгЙЄОпВуУцЭцзЊZynqЃЌдйЩюШыЦфжаЁЃ

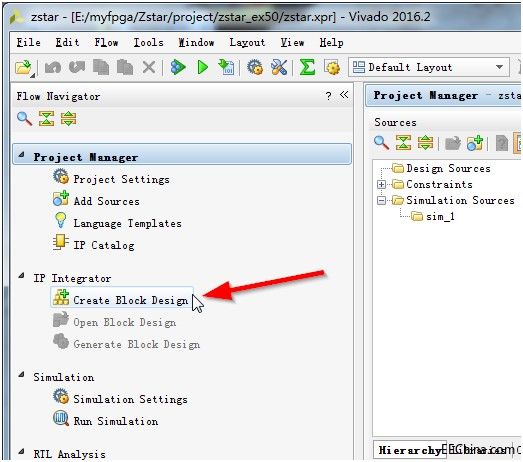

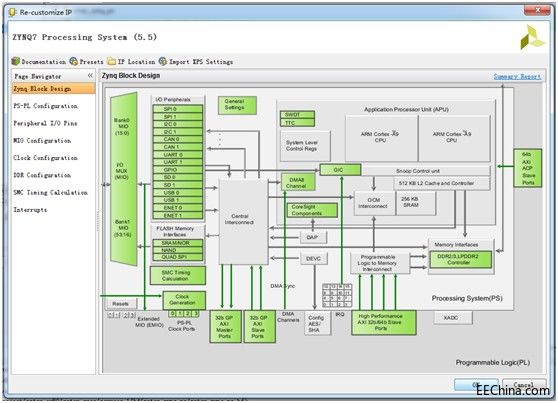

БОЪЕР§ЃЌЮвУЧвЊДюНЈЕквЛИіZynqЯЕЭГЙЄГЬЃЌВЂЧвдкетИіZynqЯЕЭГЕФCortex A9ЩЯдкЯпХмвЛИіЭЈЙ§UARTДђгЁЁАHello Zynq!ЁБЕФШэМўГЬађЁЃЕБШЛСЫЃЌжиЕуВЛЪЧHello ZynqЃЌЖјЪЧШчКЮаТНЈZynqЯЕЭГФЃПщЁЂХфжУPSЕФВЮЪ§ЁЂЕМГігВМўЁЂаТНЈШэМўЙЄГЬВЂЧвдкЯпАхМЖдЫааЦ№РДЁЃСїГЬКмживЊЃЌДѓМвдкПЊЪМЕФЪБКђзмвЊЯШзпвЛБщСїГЬСЫНтПЊЗЂЕФШЋУВЃЌШЛКѓдйЯИЯИАбЭцЃЌж№ИіОЋЭЈЁЃ аТНЈЮФМўМаzstar_ex50ЃЌзЂвтЫќЕФећИіДцЗХТЗОЖжаВЛвЊгажаЮФЁЂЗћКХЛђПеИёЃЈжЛФмЪЧЪ§зжКЭзжФИЃЉЁЃ ДђПЊVivadoЃЌВЮПМЁЖЭцзЊZynq-ЙЄОпЦЊЃКаТНЈVivadoЙЄГЬ.pdfЁЗаТНЈвЛИіVivadoЙЄГЬЁЃ дкIP IntegratorЃЈIPМЏГЩЦїЃЉЯТЕуЛїCreate Block DesignЃЈДДНЈаТЕФЩшМЦФЃПщЃЉЁЃ

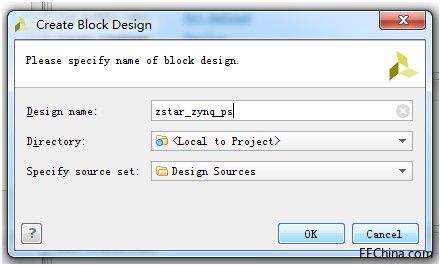

ШчЭМЫљЪОЃЌдкЕЏГіЕФCreate Block DesignДАПкжаЃЌDesign nameКѓУцЪфШыДДНЈЕФФЃПщУћГЦЃЈетРяУќУћЮЊzstar_zynq_psЃЉЃЌКѓУцЕФDirectoryМДЮФМўДцЗХТЗОЖЪЙгУФЌШЯЃЌSpecify source setМДжИЖЈЮФМўЕФзгМЏвВЪЙгУФЌШЯЁЃ

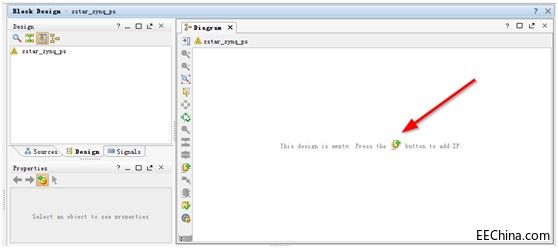

ДЫЪБЃЌдкVivadoЕФжїЪгЭМжаЃЌГіЯжСЫШчЭМЫљЪОЕФBlock DesignНчУцЁЃдкDiagramжаЃЌЕуЛїжабыЕФаЁМгКХЃЌзМБИЬэМгzynqЕФДІРэЦїIPКЫЁЃ

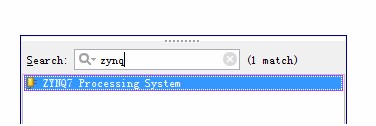

ШчЭМЫљЪОЃЌдкЕЏГіIPСаБэЕФSearchКѓУцЃЌЮвУЧЪфШыЙиМќДЪzynqЃЌЫцКѓЩИбЁГіЮЈвЛЕФZYNQ7 Processing SystemбЁЯюЃЌЕуЛїЫќЁЃ

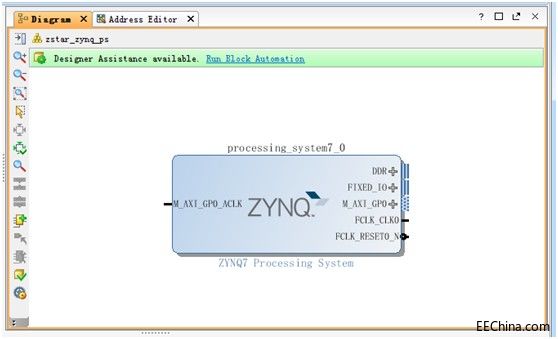

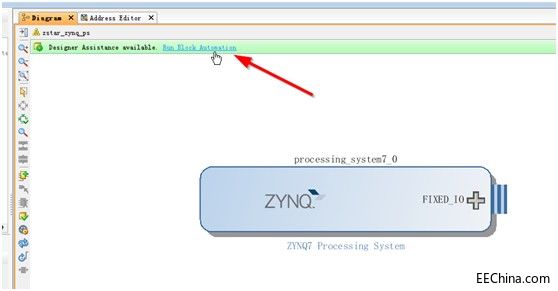

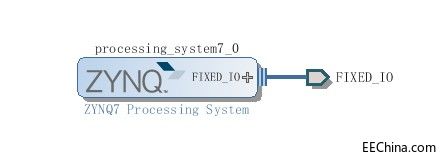

ДЫЪБЃЌDiagramНчУцжабыГіЯжСЫвЛИіУћЮЊprocessing_system7_0ЕФФЃПщЃЌПЩвдЫЋЛїетИіФЃПщЃЌНЋЕЏГіИУФЃПщЕФХфжУвГУцЁЃ

ZynqЯЕЭГХфжУвГУцШчЭМЫљЪОЁЃ

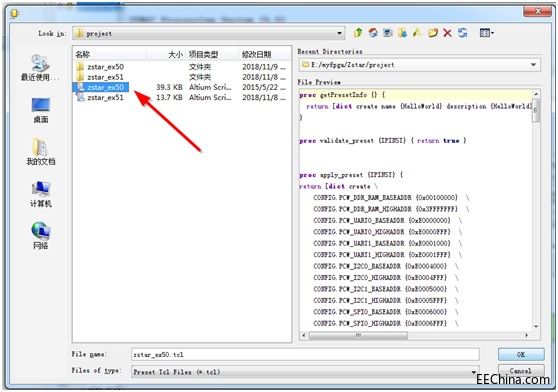

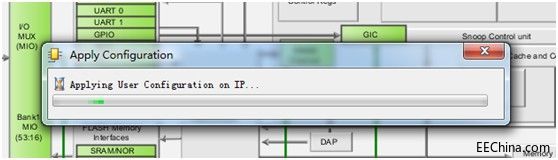

ЕуЛїPresetsАДХЅЃЌЕЏГіВЫЕЅШчЭМЃЌНгзХЕуЛїApply ConfigurationЁЃ

ЖЈЮЛЕНЕБЧАЙЄГЬТЗОЖЯТЃЌевЕНzstar_ex50.tclНХБОЃЌбЁжаЫќЃЌШЛКѓЕуЛїOKгІгУИУtclНХБОЕФЩшЖЈЁЃетВЛВйзїЕФвтвхдкгкЃЌНЋБЪепвбОХфжУКУЕФZYNQ7 Processing SystemВЮЪ§ећИігІгУЕНЕБЧАаТНЈЙЄГЬЕФЯЕЭГжаЁЃЯТУцЮвУЧЛсПДПДЖМгаФФаЉЬиЪтЕФашвЊзЂвтЕФХфжУЃЌетаЉХфжУЭЈГЃЪЧКЭЮвУЧЫљЪЙгУЕФАхМЖгВМўЕчТЗЩшМЦЯрЙиЕФЁЃ

ШчЭМЃЌЩшжУе§дкгІгУЩњаЇжаЁЃ

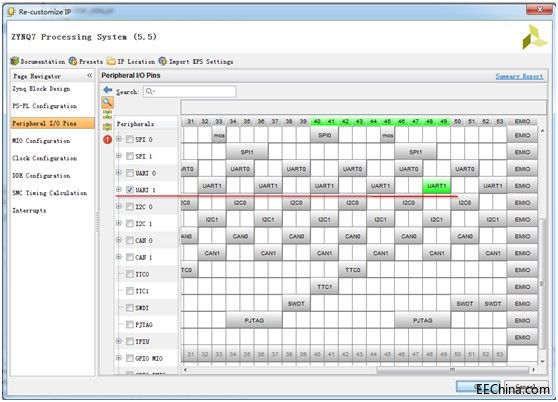

ЭъГЩХфжУМгдиКѓЃЌZynqЯЕЭГЕФЕБЧАХфжУОЭФмЙЛгУгкЮвУЧКѓајЕФШэМўЪЕР§ЁЃШчЭМЫљЪОЃЌдкPeripheral I/O PinsбЁЯюПЈжаЃЌUART 1БЛЙДбЁЩЯСЫЃЌЫќЖдгІЕФMIO48КЭMIO49СаЪЧИпССЕФЃЌБэЪОUART 1ЫљЪЙгУЕФв§НХЪЧMIO48КЭMIO49ЁЃЕуЛїOKЭъГЩЩшжУЁЃ

ЛиЕНDiagramжаЃЌПЩвдПДЕНZYNQФЃПщЕФНгПкЗЂЩњСЫБфЛЏЃЌЯждкжЛгаFIXED_IOЪЧПЩвдв§ГіЕФЃЌЪЕМЪЩЯЮвУЧКѓУцЕФЪЕР§жавВВЛЪЙгУетИів§ГіЕФFIXED_IOЁЃЕуЛїМ§ЭЗЫљжИЕФRun Block AutomationАДХЅЁЃ

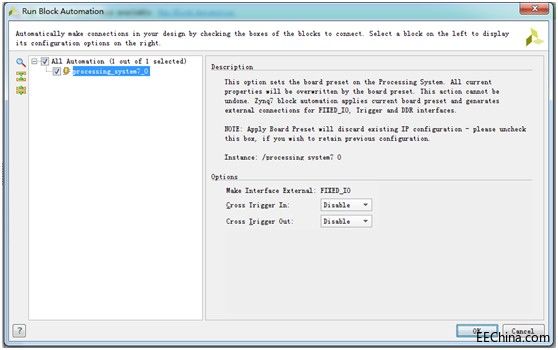

ЕЏГіЭМЪОЕФЖдЛАПђЃЌЪЙгУФЌШЯЩшжУЃЌЕуЛїOKОЭПЩвдЁЃ

етЪБЮвУЧПДЕНЃЌFIXED_IOЙћШЛБЛв§ГіСЫЁЃ

дкSourcesвГУцжаЃЌЮвУЧПЩвдПДЕНDesign SourcesЯТУцЃЌЮвУЧИеИеДДНЈЕФЯЕЭГФЃПщzstar_zynq_psЁЃ

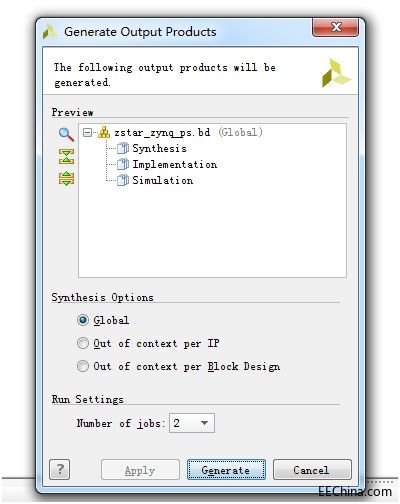

ЕуЛїбЁжаzstar_zynq_psФЃПщЃЌЕЅЛїгвМќЃЌЕЏГіВЫЕЅжаЕуЛїGenerate Output ProductsЃЌЪЙЕУИУЯЕЭГЪфГіЩњаЇЁЃ

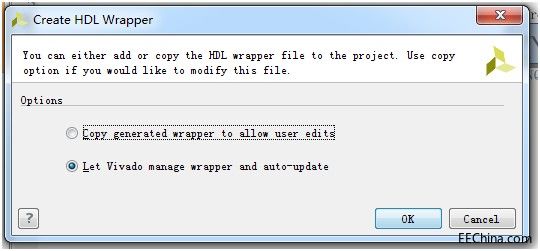

ЕЏГіЯТУцЕФЖдЛАПђЃЌЕуЛїGenerateЁЃ zstar_zynq_psФЃПщФПЧАЛЙВЛЪЧЕБЧАЙЄГЬЕФЖЅВуФЃПщЃЌБиаыдйДЮбЁжаЫќЃЌШЛКѓдкгвМќВЫЕЅжаЕуЛїCreate HDL WrapperЁЃ

ШєЕЏГіШчЯТЖдЛАПђЃЌЪЙгУФЌШЯЩшжУЃЌЕуЛїOKМЬајЁЃ

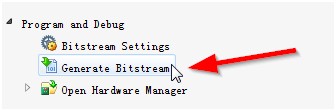

зюКѓЃЌдкFlow NavigatorЕФProgram and DebugЯТЃЌЕуЛїGenerate BitstreamБрвыећИіЙЄГЬвдЩњГЩПЩЩеТМPLЕФbitЮФМўЁЃ

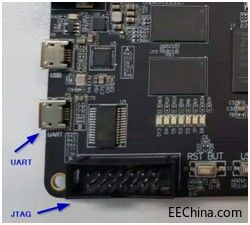

ВЮПМЮФЕЕЁЖЭцзЊZynq-ЙЄОпЦЊЃКЕМГіPSгВМўХфжУКЭаТНЈSDKЙЄГЬ.pdfЁЗЁЃ дкZstarАхзгЩЯЃЌЩшжУЬјЯпУБP3ЮЊJTAGФЃЪНЃЌМДPIN2-3ЖЬНгЁЃ СЌНгКУДЎПкЯпЃЈUSBЯпСЌНгPCЕФUSBЖЫПкКЭZstarАхЕФUARTНгПкЃЉКЭXilinxЯТдиЯпЃЈЯТдиЦїСЌНгPCЕФUSBЖЫПкКЭZstarАхЕФJTAGВхзљЃЉЁЃЪЙгУ5VЕчдДИјАхзгЙЉЕчЁЃ

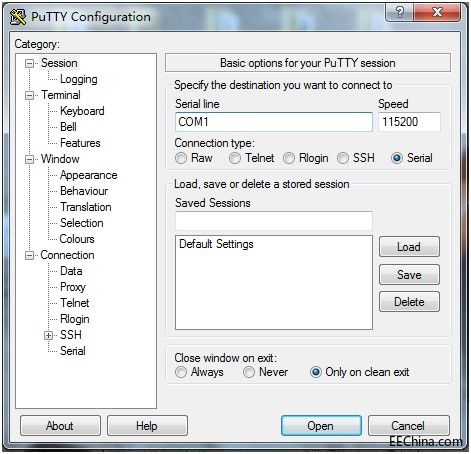

ШЗШЯЕБЧАЩшБИЙмРэЦїжаЪЖБ№ЕНЕФCOMПкКХЃЌХфжУКУДђПЊPuTTYДЎПкЕїЪдНчУцЁЃ

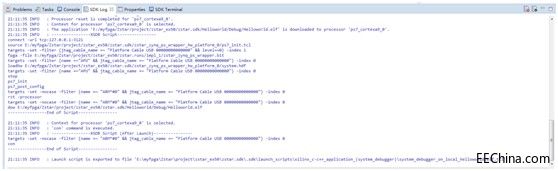

НгзХВЮПМЁЖЭцзЊZynq-ЙЄОпЦЊЃКSDKдкЯпдЫааТуХмГЬађ.pdfЁЗНЋzstar.bitЮФМўКЭHelloworld.elfЮФМўЩеТМЕНZynqжадЫааЦ№РДЁЃ

SDK LogДАПкжаЃЌвВЛсДђгЁЪфГіЯргІЕФSDKЙЄзїаХЯЂЁЃ

ЛиЕНPuTTYжаЃЌЮвУЧПЩвдПДЕНвВвбОДђгЁГіСЫЮвУЧЦкХЮвбОУЕФHello WorldЃЈВЛКУвтЫМЃЌВЛЪЧHello ZynqЃЌВЛЙ§УЛЙиЯЕЃЌHello ZynqвЊФуздМКГЂЪдИФCдДТыдйХмвЛБщОЭOKЃЉЁЃ

ЙЇЯВФуЃЌЭъГЩЕФZynqЯЕЭГCortex A9ЕФдЫааЃЌТуХмСЫвЛИіHello WorldГЬађЁЃ

|

ЭјгбЦРТл