гТИвЕФаОАщФуЭцзЊAltera FPGAСЌди105ЃКRTCЪБМфЕФLCDЯдЪОКЭUARTЩшжУ

ЗЂВМЪБМфЃК2019-2-28 16:30

ЗЂВМепЃКrousong1989

|

гТИвЕФаОАщФуЭцзЊAltera FPGAСЌди105ЃКRTCЪБМфЕФLCDЯдЪОКЭUARTЩшжУ ЬиШЈЭЌбЇЃЌАцШЈЫљга ХфЬзР§ГЬКЭИќЖрзЪСЯЯТдиСДНгЃК http://pan.baidu.com/s/1i5LMUUD

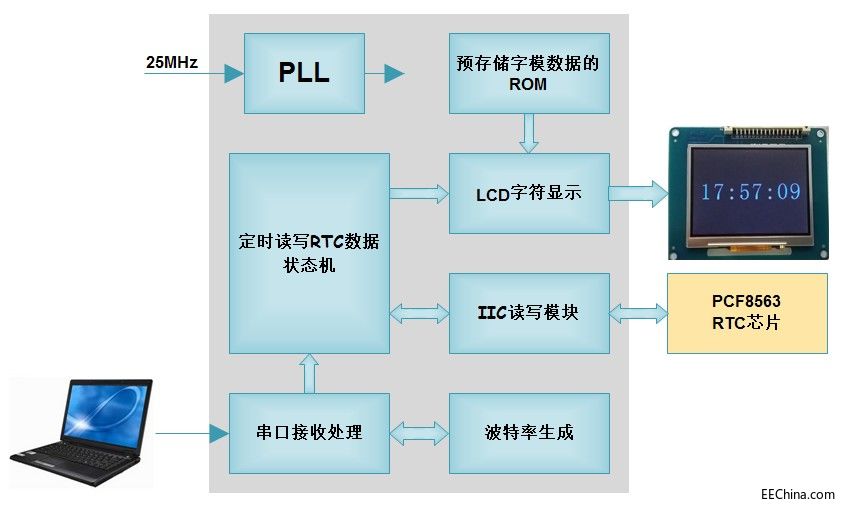

ИУЪЕР§ЙЄГЬЕФЙІФмПђЭМШчЭМ10.83ЫљЪОЁЃPCПЩвдЭЈЙ§UARTЗЂЫЭДЎПкжЁЪ§ОнЖдRTCаОЦЌЕФЕБЧАЪБМфНјааЕїећЃЛFPGAФкВПЖЈЪБЖСШЁRTCаОЦЌЕФзюаТЪБМфЃЌНЋДЫЪБМфЭЈЙ§3.5ДчЕФLCDЯдЪОГіРДЃЛLCDЕФзжФЃЪ§ОндђДцДЂдкFPGAФкЧЖROMжаЁЃ

ЭМ10.83 RTCЁЂLCDгыUARTСЊКЯЪЕР§ЙІФмПђЭМ БОЪЕР§ФЃПщЛЎЗжШчЭМ10.84ЫљЪОЁЃ

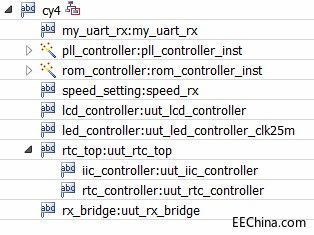

ЭМ10.84 RTCЁЂLCDгыUARTСЊКЯЪЕР§ФЃПщВуДЮ етаЉФЃПщМИКѕЧАУцЕФЪЕР§жаЖМЪЙгУЙ§ЃЌБОЪЕР§жЛЪЧНЋЫћУЧећКЯдквЛЦ№ЃЌЮЈвЛашвЊЬиБ№НјааЩшМЦЕФЪЧlcd_controller.vФЃПщжазжФЃЯдЪОЮЛжУвдМАЯрЙиТпМЕФЪЕЯжЁЃ СЌНгКУЯТдиЯпЃЌСЌНгКУSF-CY4КЫаФАхКЭSF-LCDзгАхЃЌИјЫќУЧЙЉЕчЁЃДђПЊQuartus IIЃЌНјШыЯТдиНчУцЃЌНЋБОЪЕР§ЙЄГЬЯТЕФcy4.sofЮФМўЩеТМЕНFPGAжадкЯпдЫааЁЃ ДЫЪБЃЌШчЭМ10.86ЫљЪОЃЌПЩвдПДЕНLCDЩЯЯдЪОСЫКкЕзРЖзжЕФЪБМфаХЯЂЁЃ

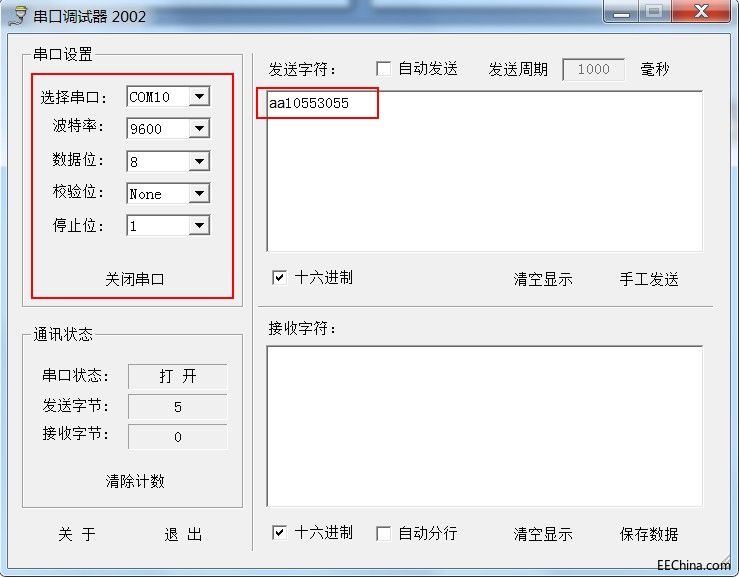

ЭМ10.86 LCDЯдЪОЪБМф ШчЭМ10.87ЫљЪОЃЌДђПЊЁАДЎПкЕїЪдЦїЁБЃЌзіКУЩшжУЃЌШЛКѓЪфШыЪ§ОнЁАaa10553055ЁБЃЌЦфжаaaБэЪОжЁЭЗЃЌ55БэЪОжЁЮВЃЌЪБМфЩшЖЈЮЊЁА10:55:30ЁБЁЃЕуЛїЁАЪжЙЄЗЂЫЭЁБЃЌдђПЩвдПДЕНвКОЇЦСЩЯЕФЪБМфвВИњзХБфЛЏСЫЃЌетЪЧвђЮЊRTCаОЦЌвбОаДШыСЫаТЕФЪБМфЪ§ОнЁЃ

ЭМ10.87 UARTавщжЁжижУЪБМф |

ЭјгбЦРТл